GaN器件结构和制备方法与流程

本申请涉及半导体,更具体而言,涉及一种gan器件结构和制备方法。

背景技术:

1、目前,常开耗尽型器件需要给器件施加负电压使得器件保持关断,这导致在器件不使用的期间增加额外的功耗,对栅驱动电路设计具有极大挑战,引起一系列的安全性问题。cascode型ganhemt是由高压耗尽型ganhemt与低压增强型simosfet级联,利用simosfet的正阈值电压和gan的高关态阻断电压实现了整体器件的高压常关特性。由于晶体管的特性决定,ganhemt最大源漏泄漏电流idss高于低压simosfet。级联的ganhemt和simosfet通过的idss一致,漏极高压下导致simosfet的实际idss大于器件承受的idss,这对于simosfet在高压条件下的可靠性具有巨大挑战,甚至可能造成simosfet击穿失效。

技术实现思路

1、本申请实施方式提供了一种gan器件结构和制备方法。

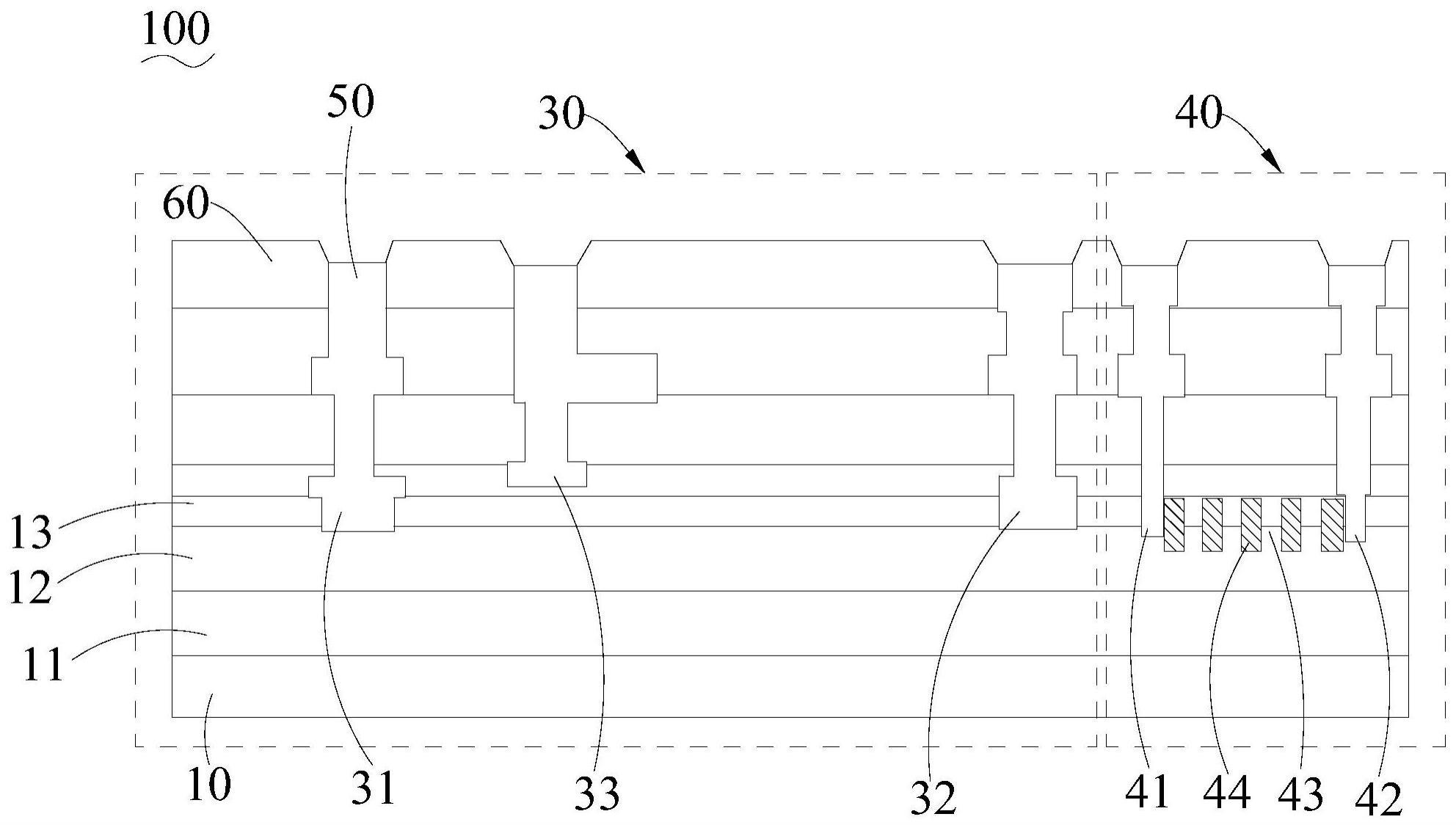

2、本申请实施方式的gan器件结构包括衬底、gan器件和电阻件,所述gan器件设置在所述衬底上,所述gan器件连接si器件,所述si器件用于控制所述gan器件,所述电阻件设置在所述衬底上,所述电阻件与所述si器件并联。

3、在本申请实施方式的gan器件结构中,gan器件和电阻件可集成在一个衬底上,简化封装流程,同时将电阻件与si器件并联,在gan器件结构关断情况下,si器件并联电阻件对源漏泄漏电流idss进行泄流,避免si器件承受高压下的idss,甚至超过器件承受水平造成si器件损坏,从而保护si器件,提高器件可靠性。

4、在某些实施方式中,所述gan器件包括源极、漏极和栅极,所述电阻件的两端分别连接所述源极和所述栅极。如此,将电阻件和高压gan器件制备在一个衬底上,简化封装流程,再将高压gan器件、电阻件与低压硅器件封装形成具有集成电阻的cascode型高压ganhemt器件。

5、在某些实施方式中,所述电阻件包括第一欧姆接触区和第二欧姆接触区,所述第一欧姆接触区连接所述源极,所述第二欧姆接触区连接所述栅极。如此,通过金属层封装外连以使得电阻件与si器件实现并联,使得电阻件可以对源漏泄漏电流idss进行泄流,避免si器件承受高压下的idss甚至超过器件承受水平造成si器件损坏,保护si器件。

6、在某些实施方式中,所述电阻件还包括电阻区,所述电阻区呈长条状弯折布置,所述电阻区的两端分别连接所述第一欧姆接触区和所述第二欧姆接触区。如此,电阻区弯折布置可以在有限的空间内尽可能地增加电阻区的长度,进而可以保证电阻件的阻值合适。

7、在某些实施方式中,所述电阻件还包括隔离区,所述电阻区弯折形成多段,多段所述电阻区平行设置,所述隔离区设置在所述电阻区的相邻段之间,并用于阻隔相邻段的所述电阻区。如此,隔离区可以阻隔相邻段的电阻区,避免相邻段的电阻区短路连接,造成电阻件的阻值减小。

8、在某些实施方式中,所述电阻件的电阻值大于或等于1兆欧。如此,电阻件的电阻值至少为1兆欧,以保证与si器件并联后,电阻件可以对器件idss水平进行调整,对通过si器件的idss进行泄流,保护si器件。

9、本申请实施方式的制备方法用于制作上述任一项实施方式所述的gan器件结构,所述gan器件的制备方法包括:

10、提供一衬底;

11、在所述衬底上形成algan/gan异质结外延层;

12、在所述algan/gan异质结外延层远离所述衬底的一侧制备gan器件和电阻件;

13、在所述gan器件和所述电阻件上制备金属层;

14、在所述金属层上制备钝化层,所述钝化层覆盖所述金属层。

15、如此,通过制备方法可以同时制备gan器件和电阻件,将gan器件和电阻件集成在一个衬底上,简化封装流程。

16、在某些实施方式中,所述在所述algan/gan异质结外延层远离所述衬底的一侧制备gan器件和电阻件,包括:

17、在所述algan/gan异质结外延层远离所述衬底的一侧制备gan器件的源极、漏极和栅极;

18、在所述algan/gan异质结外延层远离所述衬底的一侧通过离子注入隔离的方法制备电阻件。

19、如此,在制备电阻件和gan器件的时候,可以制备电阻区和隔离区以形成电阻件,制备源极、漏极和栅极以形成gan器件,形成基本的gan器件结构。

20、在某些实施方式中,所述在所述gan器件和所述和电阻件上制备金属层,包括:

21、制备金属层以使得所述gan器件和所述电阻件向外连接si器件。

22、如此,制备金属层以形成电路连接外部的si器件,进而使得si器件与电阻件并联在一起,保证电阻件可以保护si器件,避免si器件承受高压下的idss。

23、在某些实施方式中,所述制备方法还包括:

24、将所述gan器件结构与所述si器件封装,使得所述电阻件可以与所述si器件并联在一起。

25、如此,在gan器件和电阻件上制备金属层,再将高压gan器件结构与低压si器件封装,使得电阻件可以与si器件并联在一起,在gan器件结构关断情况下电阻件对源漏泄漏电流idss进行泄流,避免si器件承受高压下的idss,甚至超过器件承受水平造成si器件损坏,从而保护si器件,提高器件可靠性。

26、本申请的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本申请的实践了解到。

技术特征:

1.一种gan器件结构,其特征在于,包括:

2.根据权利要求1所述的gan器件结构,其特征在于,所述gan器件包括源极、漏极和栅极,所述电阻件的两端分别连接所述源极和所述栅极。

3.根据权利要求2所述的gan器件结构,其特征在于,所述电阻件包括第一欧姆接触区和第二欧姆接触区,所述第一欧姆接触区连接所述源极,所述第二欧姆接触区连接所述栅极。

4.根据权利要求3所述的gan器件结构,其特征在于,所述电阻件还包括电阻区,所述电阻区呈长条状弯折布置,所述电阻区的两端分别连接所述第一欧姆接触区和所述第二欧姆接触区。

5.根据权利要求4所述的gan器件结构,其特征在于,所述电阻件还包括隔离区,所述电阻区弯折形成多段,多段所述电阻区平行设置,所述隔离区设置在所述电阻区的相邻段之间,并用于阻隔相邻段的所述电阻区。

6.根据权利要求1所述的gan器件结构,其特征在于,所述电阻件的电阻值大于或等于1兆欧。

7.一种制备方法,用于制作权利要求1-6任一项所述的gan器件结构,其特征在于,所述制备方法包括:

8.根据权利要求7所述的制备方法,其特征在于,所述在所述algan/gan异质结外延层远离所述衬底的一侧制备gan器件和电阻件,包括:

9.根据权利要求8所述的制备方法,其特征在于,所述在所述gan器件和所述和电阻件上制备金属层,包括:

10.根据权利要求9所述的制备方法,其特征在于,所述制备方法还包括:

技术总结

本申请公开了一种GaN器件结构和制备方法。GaN器件结构包括衬底、GaN器件和电阻件,GaN器件设置在衬底上,GaN器件连接Si器件,Si器件用于控制GaN器件,电阻件设置在衬底上,电阻件与Si器件并联。在本申请实施方式的GaN器件结构中,GaN器件和电阻件可集成在一个衬底上,简化封装流程,同时将电阻件与Si器件并联,在GaN器件结构关断情况下,Si器件并联电阻件对源漏泄漏电流I<subgt;DSS</subgt;进行泄流,避免Si器件承受高压下的I<subgt;DSS</subgt;,甚至超过器件承受水平造成Si器件损坏,从而保护Si器件,提高器件可靠性。

技术研发人员:庞振江,洪海敏,文豪,葛俊雄,温雷,顾才鑫,廖刚

受保护的技术使用者:深圳智芯微电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!