一种瞬态抑制二极管芯片的制作方法

本发明涉及一种二极管芯片,尤其涉及一种瞬态抑制二极管芯片,本发明属于半导体器件。

背景技术:

1、瞬态电压抑制二极管(transientvoltagesuppressiondiode)也称为tvs二极管,是一种保护用的电子零件,可以保护电器设备不受导线引入的电压尖峰破坏。对于高频电路的保护,则需要低电容或者超低电容,以减少寄生电容对电路的干扰降低高频电路信号的衰减。在常规的工程领域,降低结电容的办法是减小pn结的面积或者采用串联小电阻的方式。当减小pn结面积的时候,会让二极管对浪涌电流的吸收能力下降;而当与小电容串联的方式时,除了增大电路板面积外,也显著增加了成本。

2、在常规的器件设计方案中,工程人员为了提升tvs二极管的浪涌泄放能力,通常会在器件结构中引入三极管。如图3-4共同所示,利用npn型三极管和pnp型三极管在闩锁效益启动后,器件呈现出负阻特性,从而提高tvs二极管的浪涌泄放能力,但该结构不能实现低电容吸收能力。

技术实现思路

1、为了解决上述技术所存在的不足之处,本发明提供了一种瞬态抑制二极管芯片。

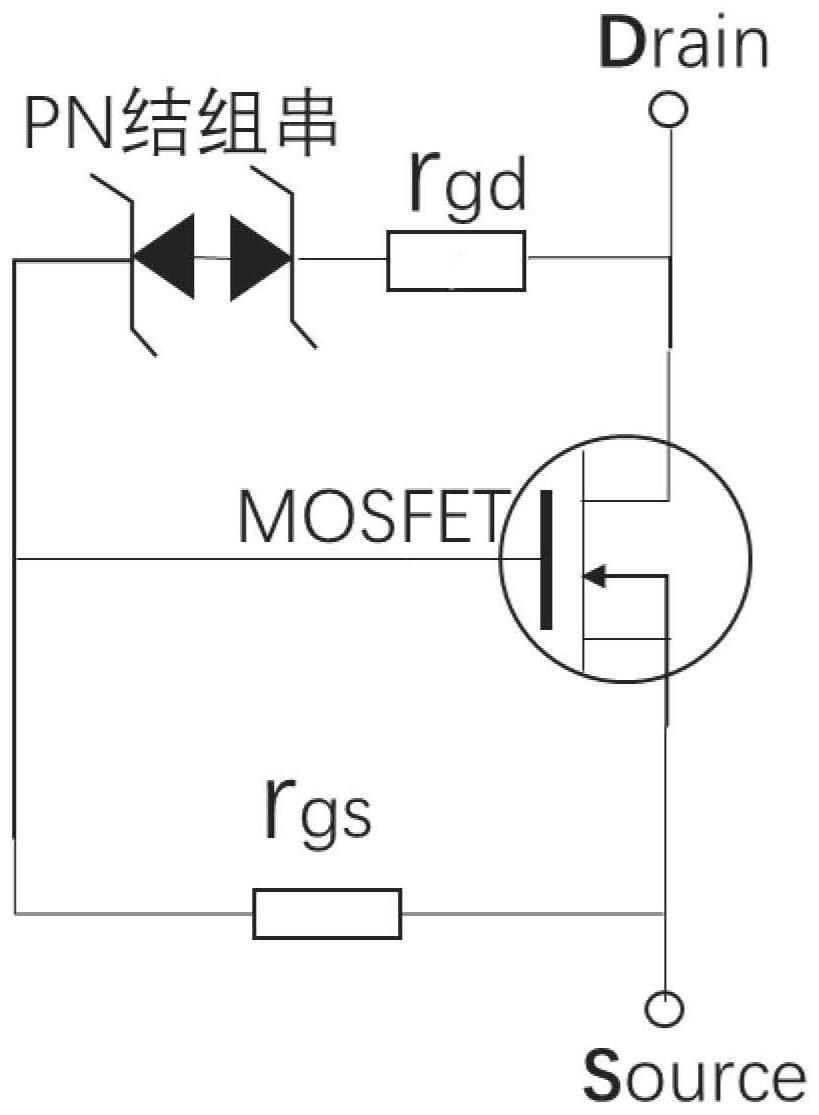

2、为了解决以上技术问题,本发明采用的技术方案是:新器件结构为在金属-氧化物-半导体场效应管的栅极和漏极之间并联有pn结组串,栅极位于mos元胞区,漏极位于芯片外围连接区,pn结组串形成有pn结组串区;

3、新器件结构包括n型重掺杂硅衬底以及形成于n型重掺杂硅衬底表面的n型轻掺杂外延层;

4、位于mos元胞区的n型轻掺杂外延层内左右间隔设置有两处p型重掺杂区,每处p型重掺杂区内均设置有n型重掺杂区;

5、位于芯片外围连接区的n型轻掺杂外延层内设置有n型重掺杂区。

6、进一步地,mos元胞区的n型轻掺杂外延层的表面上形成有栅极氧化层,栅极氧化层位于左右两处n型重掺杂区之间且跨接在两处p型重掺杂区相互靠近的单端上。

7、进一步地,栅极氧化层的表面形成有栅极多晶硅层,栅极多晶硅层为n型掺杂区。

8、进一步地,芯片外围连接区的n型轻掺杂外延层上形成有场氧化层,场氧化层避开n型重掺杂区设置。

9、进一步地,pn结组串区的n型轻掺杂外延层上形成有场氧化层,场氧化层的表面上形成有栅极多晶硅层的n型掺杂区、p型掺杂区,n型掺杂区、p型掺杂区从左到右依次交替排布且两端均为n型掺杂区。

10、进一步地,栅极与pn结组串通过栅极多晶硅层的n型掺杂区结合n型重掺杂区形成的多晶硅薄膜进行连接。

11、进一步地,漏极通过其n型重掺杂区连通pn结组串另一端的n型掺杂区进行连接。

12、进一步地,mos元胞区、pn结组串区、芯片外围连接区从左到右依次设置且三者之间相互形成有沟道。

13、本发明公开了一种瞬态抑制二极管芯片,实际上在金属-氧化物-半导体场效应管的源极和漏极之间形成具有电压瞬态抑制功能的器件,它的结电容通过电容串联的方式使之显著减小,同时通过金属-氧化物-半导体场效应管的沟道使其能量泄放能力显著增强,如此在同一颗芯片上,实现低电容和高浪涌吸收能力的双优能力,不仅如此,本发明创新的新器件结构与金属-氧化物-半导体场效应管的兼容性强,进而成本控制的宽容度高。

技术特征:

1.一种瞬态抑制二极管芯片,形成有新器件结构,其特征在于:所述新器件结构为在金属-氧化物-半导体场效应管的栅极和漏极之间并联有pn结组串,所述栅极位于mos元胞区,所述漏极位于芯片外围连接区,pn结组串形成有pn结组串区;

2.根据权利要求1所述的瞬态抑制二极管芯片,其特征在于:所述mos元胞区的n型轻掺杂外延层的表面上形成有栅极氧化层,所述栅极氧化层位于左右两处n型重掺杂区之间且跨接在两处p型重掺杂区相互靠近的单端上。

3.根据权利要求2所述的瞬态抑制二极管芯片,其特征在于:所述栅极氧化层的表面形成有栅极多晶硅层,所述栅极多晶硅层为n型掺杂区。

4.根据权利要求1所述的瞬态抑制二极管芯片,其特征在于:所述芯片外围连接区的n型轻掺杂外延层上形成有场氧化层,所述场氧化层避开n型重掺杂区设置。

5.根据权利要求1所述的瞬态抑制二极管芯片,其特征在于:所述pn结组串区的n型轻掺杂外延层上形成有场氧化层,所述场氧化层的表面上形成有栅极多晶硅层的n型掺杂区、p型掺杂区,所述n型掺杂区、p型掺杂区从左到右依次交替排布且两端均为n型掺杂区。

6.根据权利要求5所述的瞬态抑制二极管芯片,其特征在于:所述栅极与pn结组串通过栅极多晶硅层的n型掺杂区结合n型重掺杂区形成的多晶硅薄膜进行连接。

7.根据权利要求5所述的瞬态抑制二极管芯片,其特征在于:所述漏极通过其n型重掺杂区连通pn结组串另一端的n型掺杂区进行连接。

8.根据权利要求1所述的瞬态抑制二极管芯片,其特征在于:所述mos元胞区、pn结组串区、芯片外围连接区从左到右依次设置且三者之间相互形成有沟道。

技术总结

本发明公开了一种瞬态抑制二极管芯片,形成有新器件结构,栅极和漏极之间并联有PN结组串,新器件结构包括N型重掺杂硅衬底以及形成于N型重掺杂硅衬底表面的N型轻掺杂外延层,位于MOS元胞区的N型轻掺杂外延层内左右间隔设置有两处P型重掺杂区,每处P型重掺杂区内均设置有N型重掺杂区,位于芯片外围连接区的N型轻掺杂外延层内设置有N型重掺杂区;本发明器件的结电容通过电容串联的方式减小,还通过金属‑氧化物‑半导体场效应管的沟道使其能量泄放能力显著增强,如此在同一颗芯片上,实现低电容和高浪涌吸收能力的双优能力,本发明创新的新器件结构与金属‑氧化物‑半导体场效应管的兼容性强,进而成本控制的宽容度高。

技术研发人员:柳菲

受保护的技术使用者:青岛鑫蓬电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!