半导体封装的制作方法

本公开涉及半导体封装以及制造该半导体封装的方法,具体地,涉及可包括基板和堆叠在其上的多个半导体芯片的堆叠型半导体封装以及制造该堆叠型半导体封装的方法。

背景技术:

1、随着近来电子工业的进步,对高性能、高速度和紧凑电子部件的需求正在增长。为了满足这种需求,正在开发用于将多个半导体芯片安装在单个封装中的封装技术。

2、近来,在市场中对便携式电子装置的需求已经迅速增长,因此,可能需要减小构成便携式电子装置的电子部件的尺寸和重量。为此,需要开发减小每个部件的尺寸和重量以及将多个单独的部件集成在单个封装中的封装技术。可以使用多个粘合构件将部件彼此附接,但是增加粘合构件的数量可能导致各种技术问题。

技术实现思路

1、一个或更多个示例实施方式提供具有改善的结构稳定性的半导体封装以及制造该半导体封装的方法、以及减少在制造半导体封装的工艺中的故障的方法和由此制造的半导体封装。

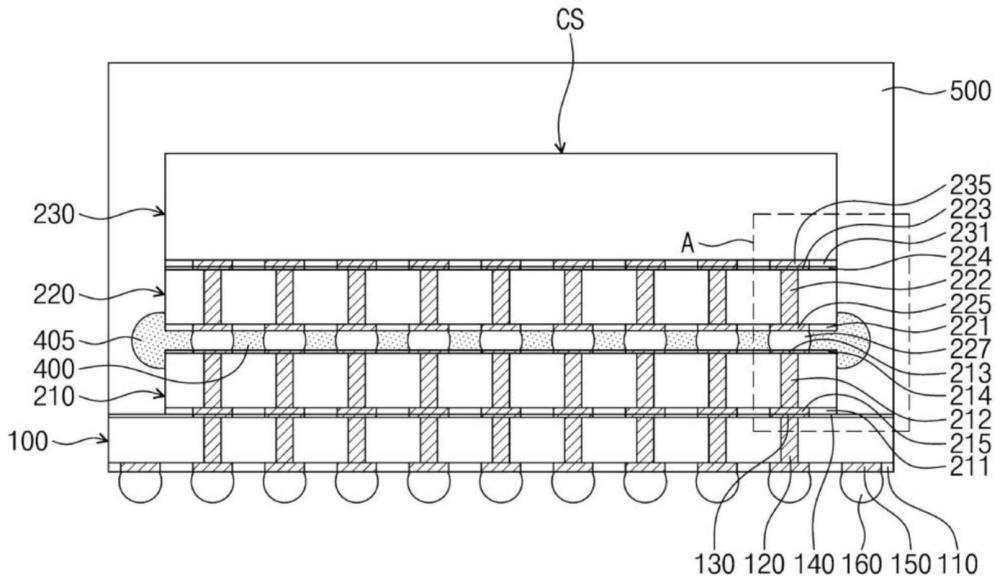

2、根据一示例实施方式的一方面,一种半导体封装包括:基板,包括多个通路;芯片堆叠,在基板上;以及模层,在基板上以及在芯片堆叠的至少一部分上,其中芯片堆叠包括:第一半导体芯片;第二半导体芯片,堆叠在第一半导体芯片上;第三半导体芯片,在第二半导体芯片中的最上面一个上;以及非导电层,在第一半导体芯片和第二半导体芯片之间,其中第一半导体芯片的第一芯片焊盘接合到基板的基板焊盘,其中第一芯片焊盘和基板焊盘的每个包括相同的金属材料并形成第一单个结构或层,其中第二半导体芯片中的最上面一个的第二芯片焊盘接合到第三半导体芯片的第三芯片焊盘,其中第二芯片焊盘和第三芯片焊盘的每个包括相同的金属材料并形成第二单个结构或层,每个第二半导体芯片使用在每个第二半导体芯片的底表面上的连接端子电连接到第二半导体芯片中的另一个或第一半导体芯片。

3、根据一示例实施方式的一方面,一种半导体封装包括:半导体基板;芯片堆叠,在半导体基板上;以及模层,在半导体基板和芯片堆叠上,其中芯片堆叠包括:第一半导体芯片,在半导体基板上;芯片结构,堆叠在第一半导体芯片上;以及非导电层,在第一半导体芯片和芯片结构中的最下面一个之间以及在相邻的芯片结构之间,其中每个芯片结构包括:第二半导体芯片;第三半导体芯片,在第二半导体芯片上;以及第一连接端子,在第二半导体芯片的底表面上,第一半导体芯片的底表面与半导体基板的顶表面直接接触,其中,在芯片结构中,第三半导体芯片的底表面与第二半导体芯片的顶表面直接接触,其中非导电层在第一半导体芯片和芯片结构中的最下面一个之间以及在相邻的芯片结构之间设置在第一连接端子周围,以及其中非导电层与半导体基板间隔开。

4、根据一示例实施方式的一方面,一种半导体封装包括:半导体基板,包括基板焊盘;在半导体基板上的第一半导体芯片,第一半导体芯片包括接合到半导体基板的基板焊盘的第一芯片焊盘,第一芯片焊盘和基板焊盘的每个包括相同的金属材料并形成单个结构或层;第二半导体芯片,在第一半导体芯片上并使用设置在第二半导体芯片的底表面上的连接端子电连接到第一半导体芯片;非导电层,在第二半导体芯片的底表面上和在连接端子周围;在第二半导体芯片上的第三半导体芯片,第二半导体芯片和第三半导体芯片分别包括第二芯片焊盘和第三芯片焊盘,其中第二芯片焊盘和第三芯片焊盘的每个包括相同的金属材料并彼此接合并且形成单个结构或层;以及模层,在半导体基板和第一至第三半导体芯片上,其中非导电层与半导体基板和第三半导体芯片间隔开。

5、根据一示例实施方式的一方面,一种制造半导体封装的方法包括:提供包括基板焊盘的半导体基板;提供包括第一芯片焊盘的第一半导体芯片;使第一半导体芯片与半导体基板接触,使得第一芯片焊盘与基板焊盘垂直对准;对半导体基板和第一半导体芯片执行第一热处理工艺,以将第一半导体芯片接合到半导体基板;提供包括第二芯片焊盘的第二半导体芯片;提供包括第三芯片焊盘的第三半导体芯片;使第三半导体芯片与第二半导体芯片接触,使得第二芯片焊盘与第三芯片焊盘垂直对准;对第二半导体芯片和第三半导体芯片执行第二热处理工艺,以将第三半导体芯片接合到第二半导体芯片;以及使用第一连接端子将第二半导体芯片安装在第一半导体芯片上,其中基板焊盘和第一芯片焊盘的每个包括相同的金属材料并通过第一热处理工艺形成单个结构或层,第二芯片焊盘和第三芯片焊盘通过第二热处理工艺形成由与基板焊盘相同的金属材料形成的单个结构或层。

技术特征:

1.一种半导体封装,包括:

2.根据权利要求1所述的半导体封装,其中所述非导电层在所述第一半导体芯片和所述第二半导体芯片之间设置在所述连接端子周围。

3.根据权利要求1所述的半导体封装,其中所述非导电层突出到在所述芯片堆叠的侧表面上的区域,以及

4.根据权利要求1所述的半导体封装,其中所述第一半导体芯片的底表面与所述基板的顶表面直接接触,以及

5.根据权利要求1所述的半导体封装,其中所述连接端子包括在所述第二半导体芯片的所述底表面上的焊料球和焊料凸块中的至少一种。

6.根据权利要求1所述的半导体封装,还包括在所述第一半导体芯片和所述第三半导体芯片之间的第四半导体芯片,

7.根据权利要求6所述的半导体封装,其中,在所述芯片结构中,所述第二半导体芯片具有面对所述基板的有源表面,所述第四半导体芯片具有面对所述基板的有源表面。

8.根据权利要求6所述的半导体封装,其中,在所述芯片结构中,所述第二半导体芯片具有面对所述第三半导体芯片的有源表面,所述第四半导体芯片具有面对所述基板的有源表面。

9.根据权利要求6所述的半导体封装,其中每个所述芯片结构使用在所述第二半导体芯片的所述底表面上的所述连接端子电连接到所述芯片结构中的另一个。

10.根据权利要求1所述的半导体封装,其中所述非导电层的宽度随着离所述基板的距离的减小而增大。

11.一种半导体封装,包括:

12.根据权利要求11所述的半导体封装,其中所述非导电层与所述芯片结构中的最上面一个中的所述第三半导体芯片间隔开。

13.根据权利要求11所述的半导体封装,其中所述第一半导体芯片的第一芯片焊盘接合到所述基板的基板焊盘,以及

14.根据权利要求11所述的半导体封装,其中,在所述芯片结构中,所述第二半导体芯片的第二芯片焊盘接合到所述第三半导体芯片的第三芯片焊盘,所述第二芯片焊盘和所述第三芯片焊盘的每个包括相同的金属材料并形成单个结构或层。

15.根据权利要求11所述的半导体封装,其中所述非导电层突出到在所述芯片堆叠的侧表面上的区域,以及

16.根据权利要求11所述的半导体封装,其中所述第一连接端子包括在所述第二半导体芯片的所述底表面上的焊料球和焊料凸块中的至少一种。

17.根据权利要求11所述的半导体封装,其中,在每个所述芯片结构中,所述第二半导体芯片的有源表面和所述第三半导体芯片的有源表面面对所述基板,所述第三半导体芯片的所述有源表面接触所述第二半导体芯片的无源表面。

18.根据权利要求11所述的半导体封装,其中,在每个所述芯片结构中,所述第二半导体芯片的有源表面和所述第三半导体芯片的有源表面彼此面对,所述第三半导体芯片的所述有源表面和所述第二半导体芯片的所述有源表面彼此接触。

19.根据权利要求11所述的半导体封装,其中每个所述芯片结构还包括在所述第三半导体芯片上的第四半导体芯片,以及

20.一种半导体封装,包括:

技术总结

一种半导体封装包括:基板,包括多个通路;在基板上的芯片堆叠;以及在基板上和在芯片堆叠的至少一部分上的模层。芯片堆叠包括:第一半导体芯片;堆叠在第一半导体芯片上的第二半导体芯片;在第二半导体芯片中的最上面一个上的第三半导体芯片;以及在第一半导体芯片和第二半导体芯片之间的非导电层。第一半导体芯片的第一芯片焊盘接合到基板的基板焊盘。第二半导体芯片中的最上面一个的第二芯片焊盘接合到第三半导体芯片的第三芯片焊盘。每个第二半导体芯片电连接到第二半导体芯片中的另一个或第一半导体芯片。

技术研发人员:张根豪

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!