半导体封装组件的制作方法

本发明涉及半导体,尤其涉及一种半导体封装组件。

背景技术:

1、随着对具有更多功能的更小装置的需求不断增加,叠层封装(package-on-package,pop)技术已经变得越来越流行。pop技术垂直堆叠两个或多个封装,并最大限度地减少不同组件(例如控制器和存储设备)之间的走线长度。这提供了更好的电气性能,因为更短的互连布线可以产生更快的信号传播并减少噪声和串扰缺陷。

2、尽管现有的半导体封装组件通常是足够的,但它们并非在各个方面都令人满意。例如,满足将不同组件集成到封装中的通道要求(channel requirement)是一项挑战。因此,需要进一步改进半导体封装组件以提供通道设计的灵活性。

技术实现思路

1、为解决上述问题,本发明提供了一种半导体封装组件,以解决上述问题。

2、根据本发明的第一方面,公开一种半导体封装组件,包括:

3、彼此堆叠的第一半导体晶粒和第二半导体晶粒,其中所述第一半导体晶粒包括:第一接口,与布置在所述第二半导体晶粒上的第二接口重叠并电连接所述第二接口;以及第三接口,布置在所述第一半导体晶粒的第一边缘上;以及

4、存储器封装,位于所述第一半导体晶粒旁边,其中所述存储器封装通过所述第三接口电连接到所述第一半导体晶粒。

5、进一步的,所述第一半导体晶粒具有第一关键尺寸并且所述第二半导体晶粒具有第二关键尺寸,其中所述第一关键尺寸比所述第二关键尺寸窄。由此以更先进的第一半导体晶粒来作为控制第三半导体晶粒及其对应封装的晶粒,从而可以应用于更高速的场景,使半导体封装组件具有更高效的处理能力。

6、进一步的,所述第一半导体晶粒包括布置在所述第一半导体晶粒的第二边缘上并连接到所述第一边缘的第四接口,其中所述存储器封装通过所述第四接口电连接到所述第一半导体晶粒和所述第二半导体晶粒。从而可以具有更多的连接路径,使连接通道更具灵活性。

7、进一步的,所述第一半导体晶粒和所述存储器封装沿第一方向并排布置,并且其中所述第一半导体晶粒沿着与所述第一方向不同的第二方向堆叠在所述第二半导体晶粒上。由此,可以在例如水平方向上第一半导体晶粒和所述存储器封装并排设置,而在竖直方向上第一半导体晶粒堆叠在第二半导体晶粒之上。

8、进一步的,所述第三接口布置为邻近于所述第一接口并且沿所述第一方向位于所述第一接口与所述存储器封装之间。由此形成的接口设计可以让第一半导体晶粒与第二半导体晶粒之间、第一半导体晶粒与存储器封装之间、第二半导体晶粒与存储器封装之间的连接路径更短。

9、进一步的,所述第二半导体晶粒包括:

10、第一通孔(tv)互连,设置在第二半导体晶粒中,并与所述第一半导体晶粒的所述第三接口重叠并电连接;以及

11、第二tv互连,设置在所述第二接口内并且电连接到所述第一半导体晶粒的第一接口。从而使第一半导体晶粒与存储器封装通过第一tv互连进行电性连接,第一半导体晶粒与第二半导体晶粒通过第二tv互连进行电性连接,并且还可以将第一半导体晶粒、第二半导体晶粒、存储器封装三者电性连接。

12、进一步的,所述第二半导体晶粒包括嵌入在所述第二半导体晶粒中并且通过所述第一半导体晶粒的第三接口电连接到所述存储器封装的沟槽电容器。从而以更加节省空间的方式来增加半导体封装组件的电容值。

13、根据本发明的第二方面,公开一种半导体封装组件,包括:

14、彼此堆叠的第一半导体晶粒和第二半导体晶粒,其中所述第一半导体晶粒包括:第一接口,与布置在所述第二半导体晶粒上的第二接口重叠并电连接所述第二接口;第三接口,布置在所述第一半导体晶粒的第一边缘上;以及

15、存储器封装,位于所述第二半导体晶粒旁边,其中所述存储器封装通过所述第三接口电连接到所述第一半导体晶粒;

16、所述第二半导体晶粒和所述存储器封装沿第一方向并排布置,并且其中所述第二半导体晶粒和所述存储器封装沿着与所述第一方向不同的第二方向堆叠在所述第一半导体晶粒上。采用这种方式可以使用位于下方的第一半导体晶粒来控制存储器封装,第一半导体晶粒与存储器封装之间的电性连接路径较短,从而最大限度地减少不同组件之间的走线长度,提供更好的电气性能、更快的信号传播,并减少噪声和串扰缺陷,并且提高半导体封装组件的通道设计的灵活性;并且由于第二半导体晶粒与存储器封装并排设置,第二半导体晶粒的厚度可以较大,从而提高第二半导体晶粒的热性能。

17、进一步的,所述第三接口被布置为沿所述第二方向与所述存储器封装件重叠。从而使得第一半导体晶粒与存储器封装之间的电性连接路径更短。

18、进一步的,所述第一接口布置在所述第一半导体晶粒的第三边缘上并且所述第三边缘与所述第一边缘相对。从而让第一半导体晶粒分别在两个相对的边缘来设置不同功能的接口,同时满足对第二半导体晶粒和存储器封装的较短的通信路径。

19、进一步的,所述第一半导体晶粒包括:

20、第一通孔(tv)互连,设置在所述第三接口内并电连接到所述存储器封装;以及

21、第二tv互连,设置在所述第一接口内并且电连接到所述第二半导体晶粒的第二接口。从而使第一半导体晶粒分别连接到存储器封装和第二半导体晶粒。

22、进一步的,所述存储器封装包括排列成组并具有第一分布区域的第一导电结构,所述第一tv互连具有与所述第一分布区域对应且至少部分重叠的第二分布区域。这样可以让第一半导体晶粒以更短的电性或通信路径连接到存储器封装及存储器封装的导电结构。

23、进一步的,所述第一tv互连布置在第一列和与所述第一列相邻的第二列中,并且包括:

24、接地tv互连,仅布置在所述第一列;以及

25、信号tv互连,布置在所述第一列和所述第二列中,其中所述第一列中的信号tv互连与接地tv互连交错,并且第二列中的信号tv互连与地tv互连相邻。从而减少相邻信号tv互连之间的串扰。

26、进一步的,所述第一半导体晶粒包括嵌入在所述第三接口内并且电连接到所述存储器封装的沟槽电容器。从而在几乎不增加封装的平面面积的情况下增加半导体封装组件的整体电容值。

27、进一步的,还包括:

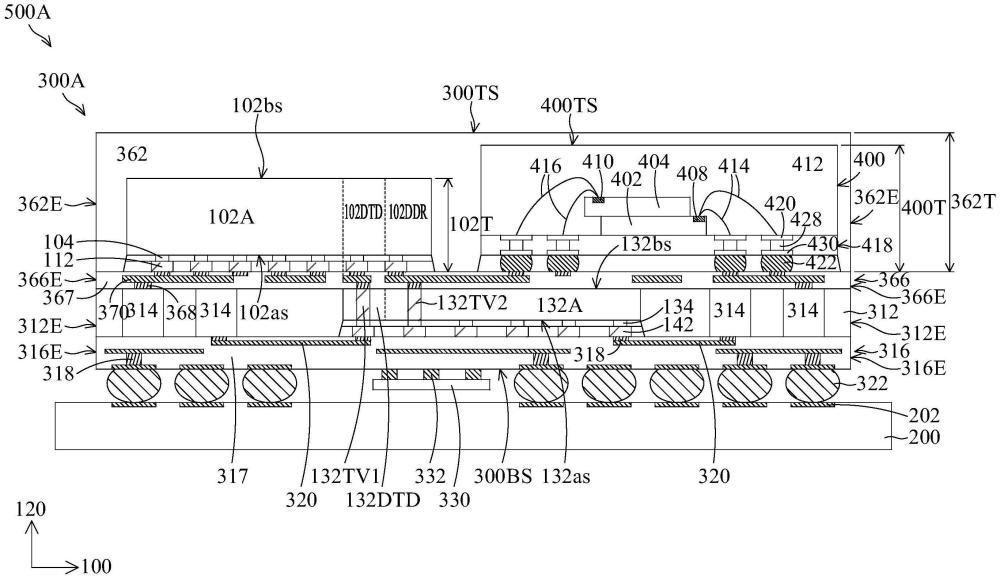

28、扇出封装,包括所述第一半导体晶粒、所述第二半导体晶粒和所述存储器封装,其中扇出封装还包括:

29、第一重分布层(rdl)结构,设置在所述第一半导体晶粒和所述第二半导体晶粒之间,其中所述第一rdl结构电连接到所述第一接口、所述第二接口、所述第三接口和所述存储器封装;

30、第二重分布层(rdl)结构,电连接到所述第一rdl结构并通过所述第一rdl结构与所述存储器封装分离;

31、第一模塑料,覆盖所述第一rdl结构与所述存储器封装;

32、第二模塑料,填充所述第一rdl结构和所述第二rdl结构之间的空间;

33、第三tv互连,穿过所述第二模塑料并电连接至所述第一rdl结构和所述第二rdl结构;以及

34、第二导电结构,与所述第二rdl结构接触并电连接。第三tv互连可以是穿过模塑料的通孔,从而进行例如电源或接地的连接。

35、进一步的,所述第一半导体晶粒包括第五接口,所述第五接口被布置为邻近于所述第三接口并且比所述第三接口更靠近所述第一边缘。第五接口可以为输入/输出接口,从而将不同功能的接口进行配置以满足需求。

36、进一步的,所述第五接口通过所述第二rdl结构而非所述第一rdl结构电连接到所述第一边缘之外的所述第二导电结构。从而输入/输出接口以更短的通信或电性连接路径连接到外部或基底等部件,通信效率更高,受干扰更少。

37、根据本发明的第三方面,公开一种半导体封装组件,包括:

38、扇出封装,包括:

39、存储器封装;

40、第一半导体晶粒,沿第一方向布置在所述存储器封装旁边;以及

41、第二半导体晶粒,沿第二方向布置在所述存储器封装件旁边,其中所述第一半导体晶粒包括:第一接口,与布置在所述第二半导体晶粒上的第二接口重叠并电连接所述第二接口;以及第三接口,靠近所述存储器封装设置并电连接至所述存储器封装。采用这种方式可以使第二半导体晶粒与存储器封装之间的电性连接路径较短,从而最大限度地减少不同组件之间的走线长度,提供更好的电气性能、更快的信号传播,并减少噪声和串扰缺陷,并且提高半导体封装组件的通道设计的灵活性;并且由于第一半导体晶粒与存储器封装并排设置,第一半导体晶粒的厚度可以较大,从而提高第一半导体晶粒的热性能。

42、进一步的,所述第一半导体晶粒包括第四接口,其中所述第三接口和所述第四接口布置在所述第一半导体晶粒的相邻边缘上,其中所述存储器封装通过的第一半导体晶粒的第四接口电连接到所述第一半导体晶粒。从而使第一半导体晶粒具有更多样及不同的与存储器封装的通信或电性连接路径,设计灵活性更高。

43、进一步的,还包括:

44、第一重分布层(rdl)结构,设置在所述第一半导体晶粒和所述第二半导体晶粒之间,其中所述第一rdl结构电连接到所述第一接口、所述第二接口、所述第三接口和所述存储器封装;以及

45、第二重分布层(rdl)结构,电连接到所述第一rdl结构并通过所述第一rdl结构与所述存储器封装分隔开。以满足封装中及封装与其他部件之间的通信及电性连接。

46、进一步的,所述第一半导体晶粒设置在所述第一rdl结构和所述第二rdl结构之间并且包括设置在所述第一接口和所述第三接口内的通孔(tv)互连。以进行第一rdl结构和所述第二rdl结构之间的电性连接。

47、进一步的,所述存储器封装包括布置成组并具有第一分布区域的第一导电结构;并且布置在所述第三接口内的tv互连具有第二分布区域,所述第二分布区域对应于所述第一分布区域并且至少部分地重叠。从而缩短半导体晶粒与存储器封装之间的电性连接路径。

48、进一步的,设置在所述第三接口内的所述tv互连布置在第一列和与所述第一列相邻的第二列中,并且包括:

49、接地tv互连,仅布置在所述第一列;以及

50、信号tv互连,布置在所述第一列和所述第二列中,其中所述第一列中的信号tv互连与接地tv互连交错,并且第二列中的信号tv互连与地tv互连相邻。从而减少相邻信号tv互连之间的串扰。

51、进一步的,所述第一半导体晶粒包括与所述第三接口相邻并且在所述第一半导体晶粒的第一边缘上布置的所述第五接口,使得所述第三接口沿着所述第二方向布置在所述第一接口和所述第五接口之间。从而使得接口布置更加灵活。

52、进一步的,所述第五接口电连接至所述第二导电结构,所述第二导电结构接触并通过第二rdl结构而不是第一rdl结构电连接至第二重布层结构,且所述第二导电结构位于第一边缘之外。从而以更短的路径连接到存储器封装及其导电结构。

53、进一步的,所述第一半导体晶粒包括嵌入在所述第三接口内并通过所述第一rdl结构电连接到所述存储器封装的沟槽电容器。以尽量不增加封装的横向面积的情况下增加电容值。

54、进一步的,所述第二半导体晶粒设置在所述第一rdl结构和所述第二rdl结构之间并且包括与所述第一半导体晶粒的所述第一接口和所述第三接口重叠的通孔(tv)互连。以便进行第一rdl结构和所述第二rdl结构的电连接。

55、进一步的,所述第二半导体晶粒包括嵌入在所述第二半导体晶粒中的沟槽电容器,其中所述沟槽电容器与所述第三接口重叠并且电连接到所述存储器封装。以尽量不增加封装的横向面积的情况下增加电容值。

56、根据本发明的第四方面,公开一种半导体封装组件,包括:

57、扇出封装,包括:

58、彼此堆叠的第一重分布层(rdl)结构与第二rdl结构;

59、顶部半导体晶粒和存储器封装,设置在第一重分布层(rdl)结构上,其中所述顶部半导体晶粒包括第一接口;以及

60、底部半导体晶粒,设置在所述第一rdl结构和所述第二rdl结构之间,其中所述底部半导体晶粒包括:第二接口,与所述第一接口重叠;以及第一通孔(tv)互连,布置在所述第二接口内并通过所述第一rdl结构电连接到所述第一接口,以及

61、其中所述存储器封装通过所述第一rdl结构而不是所述第二rdl结构电连接到所述顶部半导体晶粒和所述底部半导体晶粒。可以以路径更短的方式由顶部半导体晶粒电性连接到存储器封装,从而最大限度地减少不同组件之间的走线长度,提供更好的电气性能、更快的信号传播,并减少噪声和串扰缺陷,并且提高半导体封装组件的通道设计的灵活性;并且由于顶部半导体晶粒与存储器封装并排设置,顶部半导体晶粒的厚度可以较大,从而提高顶部半导体晶粒的热性能。

62、进一步的,所述顶部半导体晶粒包括第三接口,位于所述第一接口旁边并靠近所述存储器封装,其中所述存储器封装通过所述第三接口电连接到所述顶部半导体晶粒。从而增加与存储器封装的连接路径和通道,设计更加灵活。

63、进一步的,所述底部半导体晶粒包括与所述第三接口重叠并且通过所述第一rdl结构电连接到所述第三接口的第二通孔(tv)互连。从而通过通孔(tv)互连的进行电性连接。

64、进一步的,所述底部半导体晶粒包括与所述存储器封装重叠的第四接口,其中所述存储器封装通过所述第四接口电连接到所述底部半导体晶粒。从而使得底部半导体晶粒与所述存储器封装以更短的路径连接。

65、进一步的,所述底部半导体晶粒包括布置为邻近于所述第四接口并且位于所述底部半导体晶粒的第一边缘上的第五接口,使得所述第四接口设置在所述第二接口和所述第五接口之间。从而使得接口配置更加灵活和全面。

66、进一步的,所述底部半导体晶粒包括布置在所述第四接口内并且电连接到所述存储器封装的第三通孔(tv)互连。从而缩短电性连接路径。

67、进一步的,所述第三tv互连布置在第一列和与所述第一列相邻的第二列中,并且包括:

68、接地tv互连,仅布置在所述第一列;以及

69、信号tv互连,布置在所述第一列和所述第二列中,其中所述第一列中的信号tv互连与接地tv互连交错,并且第二列中的信号tv互连与地tv互连相邻。从而减少相邻信号tv互连之间的串扰。

70、进一步的,所述底部半导体晶粒包括嵌入在所述底部半导体晶粒中并且电连接到所述存储器封装的沟槽电容器。以尽量不增加封装的横向面积的情况下增加电容值。

71、本发明的半导体封装组件由于包括:彼此堆叠的第一半导体晶粒和第二半导体晶粒,其中所述第一半导体晶粒包括:第一接口,与布置在所述第二半导体晶粒上的第二接口重叠并电连接所述第二接口;以及第三接口,布置在所述第一半导体晶粒的第一边缘上;以及存储器封装,位于所述第一半导体晶粒旁边,其中所述存储器封装通过所述第三接口电连接到所述第一半导体晶粒。采用本发明的上述方案,可以以路径更短的方式由第一半导体晶粒电性连接到存储器封装,从而最大限度地减少不同组件之间的走线长度,提供更好的电气性能、更快的信号传播,并减少噪声和串扰缺陷,并且提高半导体封装组件的通道设计的灵活性;并且由于第一半导体晶粒与存储器封装并排设置,第一半导体晶粒的厚度可以较大,从而提高第一半导体晶粒的热性能。

- 还没有人留言评论。精彩留言会获得点赞!