一种沟槽屏蔽栅MOSFET器件及其制造方法和电子设备与流程

本发明涉及半导体器件的,尤其涉及一种沟槽屏蔽栅mosfet器件及其制造方法和电子设备。

背景技术:

1、屏蔽栅mosfet器件可以采用较低电阻率外延材料获得同等击穿电压实现电场调制,具有集成度高、导通电阻低、开关速度快、开关损耗小的特点,广泛应用于各类同步整流、储能等应用及开关转换。随着工业的发展,由于全球气候变暖,越来越重视节能减碳和可持续发展,因而对于功率mosfet器件的使用效率要求越来越高。

2、mosfet器件的开关损耗主要受制于栅极电荷大小,栅极电荷越小,开关损耗也越小,目前,为了降低开关损耗,追求高效使用能源,会从降低导通电阻和栅极电荷两个途径着手。

3、但其存在的问题是,在实际应用过程中,由于电网波动或运行过程尖峰电压等原因,屏蔽栅mosfet会短时处于击穿状态,屏蔽栅处于击穿状态时,击穿产大量的空穴,其中很大一部分空穴会朝着屏蔽栅的方向运动,并撞击位于屏蔽栅与漏极之间厚氧层,从而在外延/厚氧化层产生很多陷阱,进而影响电场分布,导致击穿电压不稳定,降低器件的可靠性。

技术实现思路

1、本发明实施例提供一种沟槽屏蔽栅mosfet器件及其制造方法和电子设备,有效的提高了器件对电场的调制效果,进而提高了击穿电压。

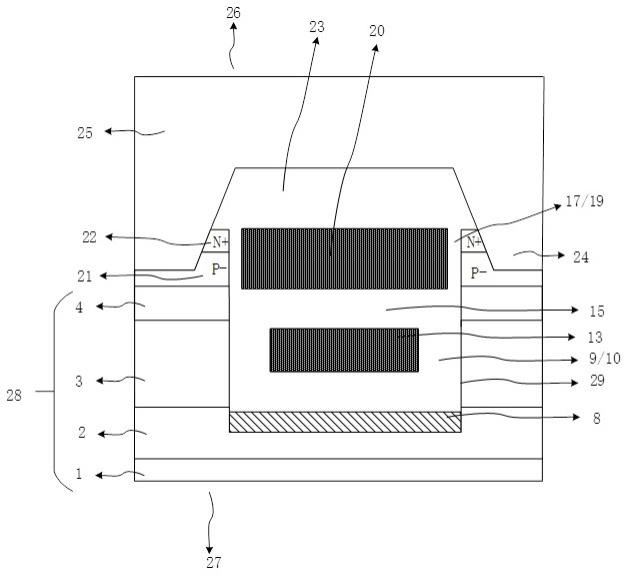

2、根据本发明的第一方面,提供了一种沟槽屏蔽栅mosfet器件,该器件包括半导体基板,所述半导体基板具有相对的第一主面与第二主面,所述第一主面与第二主面之间包括第一导电类型外延层,所述第一导电类型外延层包括沿远离所述第二主面依次设置的第一导电类型漏极区、第一导电类型第一外延层和第一导电类型第二外延层;

3、所述第一导电类型外延层内的上部设有第二导电类型阱层;元胞沟槽位于第一导电类型外延层上方,深度伸入第二导电类型阱层下方的第一导电类型外延层;

4、所述元胞沟槽上部设有栅导电多晶硅,所述元胞沟槽中下部设有屏蔽栅导电多晶硅,所述栅导电多晶硅和所述屏蔽栅导电多晶硅之间设有绝缘氧化层;相邻所述元胞沟槽的侧壁上方设有第一导电类型源极区,所述第一导电类型源极区位于所述第二导电类型阱层的上部;

5、所述第一导电类型外延层还包括第一导电类型第三外延层,所述第一导电类型第三外延层位于所述第一导电类型第二外延层远离所述第一导电类型第一外延层的一侧;

6、所述第一导电类型第二外延层的平均电阻率小于所述第一导电类型第三外延层的平均电阻率。

7、可选的,所述第一导电类型第二外延层中,电阻率沿所述第一主面指向所述第二主面的方向梯度递减。

8、可选的,第一导电类型第二外延层中,电阻率沿所述第一主面指向所述第二主面的方向保持不变。

9、可选的,沟槽屏蔽栅mosfet器件还包括电场屏蔽层,所述电场屏蔽层位于所述元胞沟槽朝向所述第二主面的一侧。

10、可选的,所述栅导电多晶硅位于所述元胞沟槽的中心区,且所述栅导电多晶硅体覆盖所述元胞沟槽的槽口;所述栅导电多晶硅与所述元胞沟槽的侧壁、顶部两侧间设有绝缘栅氧化层;所述屏蔽栅导电多晶硅位于所述栅导电多晶硅的下方,所述屏蔽栅导电多晶硅和所述栅导电多晶硅之间设有绝缘氧化层;所述屏蔽栅导电多晶硅与所述元胞沟槽的侧壁、底部设有第二氧化层和第三氧化层。

11、根据本发明的第二方面,提供了一种沟槽屏蔽栅mosfet器件的制造方法,该方法包括:

12、a、提供具有相对的第一主面与第二主面的半导体基板,所述第一主面与第二主面之间包括第一导电类型外延层,所述第一导电类型外延层包括沿远离所述第二主面依次设置的第一导电类型漏极区、第一导电类型第一外延层、第一导电类型第二外延层和第一导电类型第三外延层;

13、b、在所述半导体基板的第一主面上淀积硬掩膜层,并选择性地掩蔽和刻蚀所述硬掩膜层,在所述半导体基板的第一主面上形成沟槽刻蚀的硬掩膜窗口;

14、c、利用所述硬掩膜窗口,在第一主面上通过干法刻蚀所述半导体基板,在所述第一导电类型第一外延层上方形成沟槽,所述沟槽包括元胞沟槽;

15、e、去除所述硬掩膜层,在所述半导体基板的第一主面上生长第二氧化层,然后再淀积一层第三氧化层,所述第二氧化层和第三氧化层覆盖于第一主面上,并覆盖于所述元胞沟槽的侧壁及底部表面,且在所述元胞沟槽内形成屏蔽栅导电多晶硅淀积槽;

16、f、在所述半导体基板的第一主面上淀积导电多晶硅体材料层,制作光刻胶,通过光刻定义出屏蔽栅导电多晶硅需要去除的区域后,通过刻蚀去除导电多晶硅体材料层中未被光刻胶覆盖的部分,形成屏蔽栅导电多晶硅;

17、g、在所述半导体基板的第一主面上淀积第四氧化层,制作光刻胶,通过光刻定义出第四氧化层需要去除的区域后,通过刻蚀去除所述第四氧化层中未被光刻胶覆盖的部分,形成屏蔽栅导电多晶硅及栅导电多晶硅间的绝缘氧化层;

18、h、在所述半导体基板的第一主面上生长第五氧化层,然后通过湿法刻蚀去除所述第五氧化层,继续在所述半导体基板的第一主面上生长第六氧化层,所述第六氧化层覆盖于第一主面上,并覆盖于所述元胞沟槽的侧壁及所述屏蔽栅导电多晶硅的上部,且在所述元胞沟槽内形成栅导电多晶硅淀积槽;

19、i、在所述半导体基板的第一主面上淀积导电多晶硅体材料层,制作光刻胶,通过光刻定义出栅导电多晶硅需要去除的区域后,通过刻蚀去除导电多晶硅体材料层中未被光刻胶覆盖的部分,形成栅导电多晶硅;

20、j、在所述半导体基板的第一主面上注入第二导电类型杂质离子,并通过推阱形成第二导电类型阱层;

21、k、在所述半导体基板的第一主面上,制作光刻胶,进行源极区光刻,并注入第一导电类型杂质离子,去除光刻胶后,通过推阱形成第一导电类型源极区;

22、其中,所述第一导电类型第二外延层的平均电阻率小于所述第一导电类型第三外延层的平均电阻率。

23、可选的,在步骤e之前,还包括:

24、d、在所述半导体基板的第一主面上生长第一氧化层,然后注入第二导电型导电类型杂质,在所述元胞沟槽的底部形成电场屏蔽层;

25、步骤e还包括:去除所述第一氧化层。

26、可选的,在步骤k之后,还包括:

27、l、在所述半导体基板的第一主面上淀积绝缘介质层;

28、m、对所述绝缘介质层进行光刻和刻蚀,在所述栅导电多晶硅的两侧均形成接触孔;

29、n、在所述绝缘介质层上淀积第一金属层,所述第一金属层覆盖于绝缘介质层上,并填充于所述接触孔内,形成金属连线;所述金属连线与所述第一导电类型源极区及所述第二导电类型阱层欧姆接触。

30、可选的,在步骤n之后,还包括:

31、o、在所述金属连线上淀积钝化层,并在所述钝化层上制作光刻胶定义出金属线窗口,通过干法刻蚀所述钝化层形成所述金属线窗口。

32、根据本发明的第三方面,提供了一种电子设备,该电子设备包括了以上任意一种沟槽屏蔽栅mosfet器件。

33、根据本发明实施例提供的沟槽屏蔽栅mosfet器件,该器件通过添加第一导电类型第三外延层,并且第一导电类型第二外延层的平均电阻率小于第一导电类型第三外延层的平均电阻率,提高了器件对电场的调制效果,从而提高了击穿电压,解决了击穿电压不稳定,器件的可靠性低的问题。

- 还没有人留言评论。精彩留言会获得点赞!