一种低正向导通损耗的增强型器件的制作方法

本发明涉及半导体器件领域,具体为一种低正向导通损耗的增强型器件。

背景技术:

1、第三代宽禁带半导体是相较于第一代硅、锗和第二代砷化镓等禁带更宽的宽禁带半导体。氮化镓材料作为第三代半导体材料,具有宽带隙、直接带隙、高击穿电场、较低的介电常数、高电子饱和漂移速度、抗辐射能力强和良好的化学稳定性等良好的性质。是实现高温与大功率、高频及抗辐射器件的理想材料,是未来高新技术发展的关键基础材料。但是现有的氮化镓增强型器件在设定为较大的阈值电压时,同时也会产生很大的功耗。

技术实现思路

1、本发明的目的在于克服现有氮化镓增强型器件功耗大的问题,提供了一种低正向导通损耗的增强型器件。

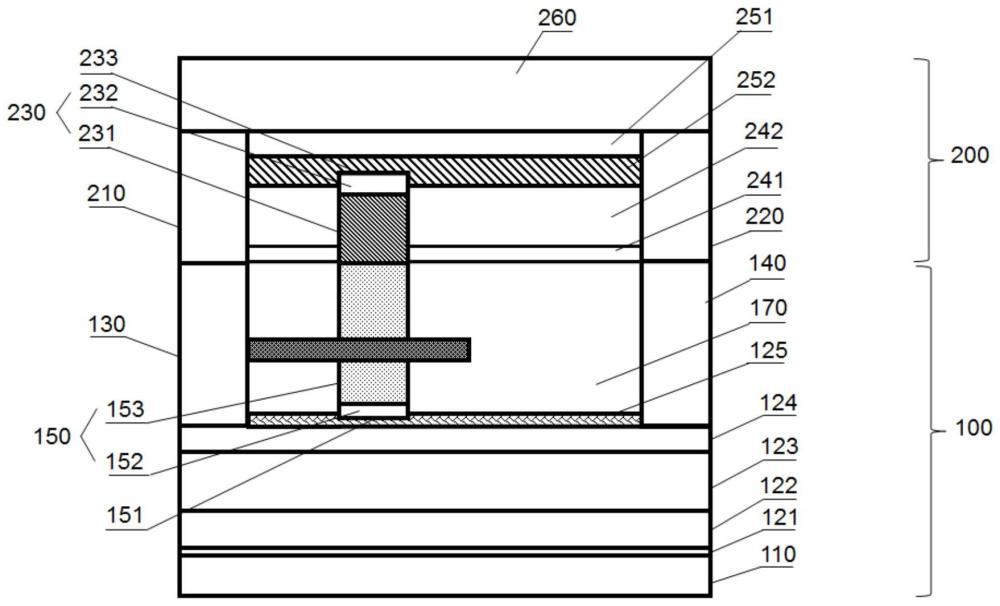

2、为了实现上述目的,本发明提供一种低正向导通损耗的增强型器件,包括:第一增强型器件结构和第二增强型器件结构;

3、所述第一增强型器件结构包括第一源极、第一漏极和第一栅极;

4、所述第二增强型器件结构包括第二源极、第二漏极、第二栅极、第二沟道结构,所述第二增强型器件结构位于所述第一增强型器件结构表面,且所述第一增强型器件结构的第一源极、第一漏极、第一栅极和所述第二增强型器件结构的第二源极、第二漏极、第二栅极相对设置,所述第二源极和所述第一源极电连接,所述第二栅极和所述第一栅极电连接,所述第二漏极和所述第一漏极电连接,所述第二沟道结构位于所述第二栅极表面且位于所述第二源极、所述第二漏极之间。

5、作为一种可实施方式,所述第一增强型器件结构还包括金属场板。

6、作为一种可实施方式,所述第二源极位于所述第一源极表面,实现所述第二源极和所述第一源极电连接;所述第二栅极位于所述第一栅极表面,实现所述第二栅极和所述第一栅极电连接;所述第二漏极位于所述第一漏极表面,实现所述第二漏极和所述第一漏极电连接。

7、作为一种可实施方式,所述第二沟道结构暴露至少部分所述第二源极表面、所述第二漏极表面,或者,所述第二沟道结构还位于所述第二源极、所述第二漏极的表面。

8、作为一种可实施方式,所述第二栅极包括位于所述第一增强型器件结构表面的第二栅极金属、位于所述第二沟道结构和所述第二栅极金属之间的第二p-gan层;或者,所述第二栅极包括位于所述第一增强型器件结构表面的第二栅极金属、位于所述第二栅极金属表面的第二中间介质层、位于所述第二沟道结构和所述第二中间介质层之间的第二p-gan层。

9、作为一种可实施方式,所述第二沟道结构面向所述第二栅极的一侧表面具有第二栅极凹槽;所述第二栅极包括:

10、位于所述第一增强型器件结构表面的第二栅极金属;

11、位于所述第二栅极金属和所述第二栅极凹槽之间的第二栅介质层。

12、作为一种可实施方式,所述第二增强型器件结构还包括:

13、位于所述第一增强型器件结构表面和所述第二沟道结构之间的第二介质层。

14、作为一种可实施方式,所述第二介质层包括:

15、位于所述第一增强型器件结构表面的第二成核层;

16、位于所述第二成核层表面的第二缓冲层。

17、作为一种可实施方式,所述第二沟道结构包括:

18、位于所述第二栅极表面的第二势垒层;

19、位于所述第二势垒层表面的第二沟道层;

20、其中,所述第二沟道层暴露至少部分所述第二源极表面、所述第二漏极表面;或者,所述第二沟道层还位于所述第二源极表面、所述第二漏极表面。

21、作为一种可实施方式,所述第二增强型器件结构还包括:

22、位于所述第二沟道结构表面的绝缘介质层;或者,位于所述第二沟道结构5表面、所述第二源极表面、所述第二漏极表面的绝缘介质层。

23、作为一种可实施方式,所述第一增强型器件结构还包括:

24、第一衬底;

25、位于所述第一衬底表面的第一外延结构;

26、位于所述第一外延结构表面的第一沟道结构;

27、0位于所述第一沟道结构表面的第一栅极;

28、位于所述第一沟道结构表面、所述第一栅极表面的第一介质层;

29、其中,所述第一源极、所述第一漏极位于所述第一沟道结构表面;所述第一介质层暴露至少部分所述第一源极表面、所述第一漏极表面。

30、作为一种可实施方式,所述第一栅极包括位于所述第一沟道结构表面的第5一p-gan层、位于所述第一p-gan层表面的第一栅极金属;或者,所述第一栅极包括位于所述第一沟道结构表面的第一p-gan层、位于所述第一p-gan层表面的第一中间介质层、位于所述第一中间介质层表面的第一栅极金属。

31、作为一种可实施方式,所述第一沟道结构表面具有第一栅极凹槽,所述第一栅极包括:

32、0位于所述第一栅极凹槽内表面的第一栅介质层;

33、位于所述第一栅介质层表面的第一栅极金属。

34、作为一种可实施方式,所述第一外延结构包括:

35、位于所述第一衬底表面的第一成核层;

36、位于所述第一成核层表面的第一缓冲层;

37、5位于所述第一缓冲层表面的第一高阻层。

38、作为一种可实施方式,所述第一沟道结构包括:

39、位于所述第一外延结构表面的第一沟道层;

40、位于所述第一沟道层表面的第一势垒层。

41、作为一种可实施方式,所述第一增强型器件结构和所述第二增强型器件结构都为氮化镓增强型器件结构。

42、本发明的有益效果:本发明涉及半导体器件领域,公开了一种低正向导通损耗的增强型器件,包括:第一增强型器件结构和第二增强型器件结构;通过将所述第二增强型器件结构设于所述第一增强型器件结构表面,所述第二增强型器件结构位于所述第一增强型器件结构表面,且所述第一增强型器件结构的第一源极、第一漏极、第一栅极和所述第二增强型器件结构的第二源极、第二漏极、第二栅极相对设置,并使得所述第二增强型器件结构的第二源极、第二栅极、第二漏极分别电连接所述第一增强型器件结构的第一源极、第一栅极、第一漏极。使得通过垂直外延的方式,在保持器件面积不变的情况下,使导通电阻降低至原来的一半,大大降低了正向导通时的功耗。且电流密度增加一倍,且保持了寄生电容不增加,大大的提高了gan材料的电流能力。

技术特征:

1.一种低正向导通损耗的增强型器件,其特征在于,包括:第一增强型器件结构和第二增强型器件结构;

2.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第一增强型器件结构还包括金属场板。

3.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第二源极位于所述第一源极表面,实现所述第二源极和所述第一源极电连接;所述第二栅极位于所述第一栅极表面,实现所述第二栅极和所述第一栅极电连接;所述第二漏极位于所述第一漏极表面,实现所述第二漏极和所述第一漏极电连接。

4.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第二沟道结构暴露至少部分所述第二源极表面、所述第二漏极表面,或者,所述第二沟道结构还位于所述第二源极、所述第二漏极的表面。

5.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第二栅极包括位于所述第一增强型器件结构表面的第二栅极金属、位于所述第二沟道结构和所述第二栅极金属之间的第二p-gan层;或者,所述第二栅极包括位于所述第一增强型器件结构表面的第二栅极金属、位于所述第二栅极金属表面的第二中间介质层、位于所述第二沟道结构和所述第二中间介质层之间的第二p-gan层。

6.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第二沟道结构面向所述第二栅极的一侧表面具有第二栅极凹槽;所述第二栅极包括:

7.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第二增强型器件结构还包括:

8.根据权利要求7所述的低正向导通损耗的增强型器件,其特征在于,所述第二介质层包括:

9.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第二沟道结构包括:

10.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第二增强型器件结构还包括:

11.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第一增强型器件结构还包括:

12.根据权利要求11所述的低正向导通损耗的增强型器件,其特征在于,所述第一栅极包括位于所述第一沟道结构表面的第一p-gan层、位于所述第一p-gan层表面的第一栅极金属;或者,所述第一栅极包括位于所述第一沟道结构表面的第一p-gan层、位于所述第一p-gan层表面的第一中间介质层、位于所述第一中间介质层表面的第一栅极金属。

13.根据权利要求11所述的低正向导通损耗的增强型器件,其特征在于,所述第一沟道结构表面具有第一栅极凹槽,所述第一栅极包括:

14.根据权利要求11所述的低正向导通损耗的增强型器件,其特征在于,所述第一外延结构包括:

15.根据权利要求11所述的低正向导通损耗的增强型器件,其特征在于,所述第一沟道结构包括:

16.根据权利要求1所述的低正向导通损耗的增强型器件,其特征在于,所述第一增强型器件结构和所述第二增强型器件结构都为氮化镓增强型器件结构。

技术总结

本发明涉及半导体器件技术领域,公开了一种低正向导通损耗的增强型器件,包括:第一增强型器件结构和第二增强型器件结构;通过将所述第二增强型器件结构设于所述第一增强型器件结构表面,并使得所述第二增强型器件结构的第二源极、第二栅极、第二漏极分别电连接所述第一增强型器件结构的第一源极、第一栅极、第一漏极。使得通过垂直外延的方式,在保持器件面积不变的情况下,使导通电阻降低至原来的一半,大大降低了正向导通时的功耗。且电流密度增加一倍,且保持了寄生电容不增加,大大的提高了GaN材料的电流能力。

技术研发人员:黄明乐,鲁怀贤,夏元治

受保护的技术使用者:合肥仙湖半导体科技有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!