超结IGBT器件的制作方法

本发明涉及一种半导体集成电路,特别是涉及一种超结(sj)绝缘栅双极型晶体管(igbt)器件。

背景技术:

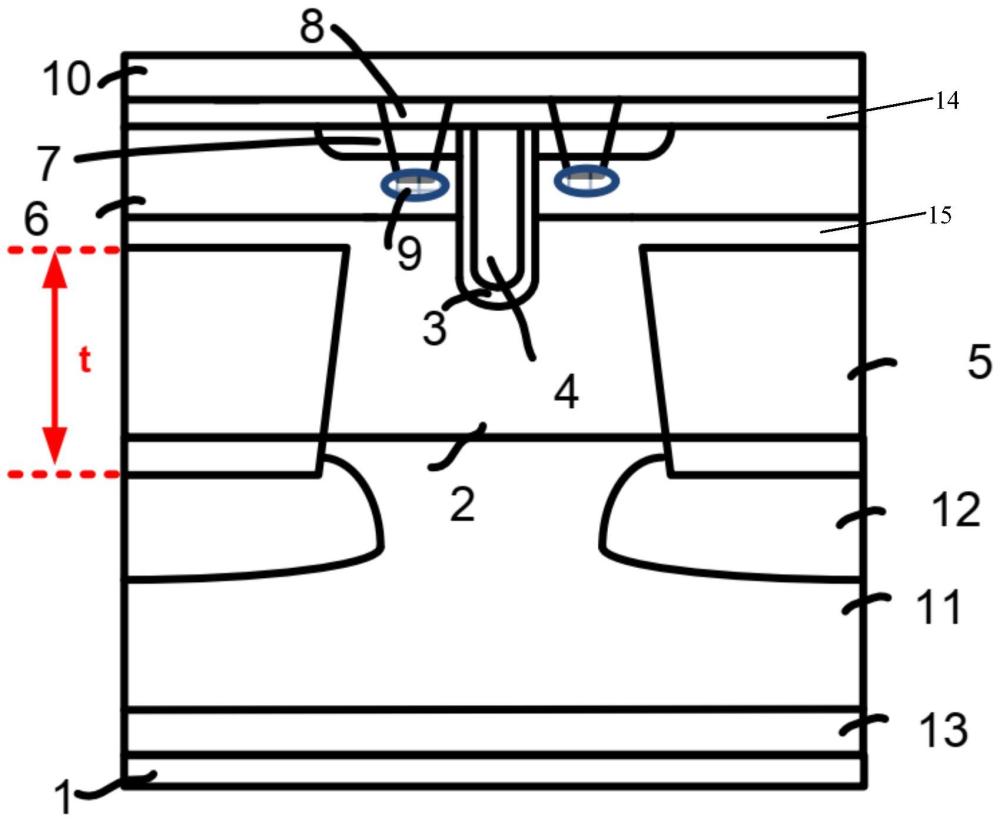

1、如图1所示,是现有超结igbt器件(sj-igbt)的结构示意图;现有超结igbt器件包括:

2、集电区101,采用背面注入形成,以n型器件为例,集电区101为p型掺杂,采用p型背面注入形成;注入的杂质通常是硼(boron),也可以是bf2,注入的能量是在15~100kev之间,注入的剂量通常在1e12/cm2~1e14/cm2之间。通常背面注入的剂量越高,器件导通时,导通压降更低,但是关断时,电流拖尾越大,关断损耗越高。因此对于低速应用的igbt器件,其背面注入的剂量通常较高,而对于高速应用的场景,背面注入的剂量通常比较低。

3、n型外延层102组成器件的n型漂移区。跟现有传统的igbt不同,sj-igbt,在n型外延层102中还形成有p柱105,p柱105和p柱105之间的n型外延层102组成的n柱交替排列形成超结结构,超结结构的厚度t101为p型105的厚度。p柱105通常有两种实现方式,一种是沟槽刻蚀和p型硅填入,这种方式的好处是工艺步骤少,但是其沟槽刻蚀的深宽比髙,工艺难度大;而且p型硅填入的时候,容易引入缺陷,造成器件的漏电大,更重要的是沟槽刻蚀的倾斜角度很难监控(monitor),这也给工艺控制带来了很大的难度。另外一种是基于多次外延和离子注入,这种方式的好处是工艺实现简单,但是工艺步骤多,成本高。sj-igbt的击穿电压就是通过p柱105和p柱105之间的n型漂移区的横向耗尽,降低了等效的掺杂浓度,从而可以在不降低击穿电压的情况下,大幅提高漂移区的掺杂浓度。以650v igbt为例,传统的igbt,漂移区的掺杂浓度通常在2e14/cm3以下,而sj-igbt漂移区的掺杂浓度能够在2e15/cm3以上,甚至达到1e16/cm3以上。p柱105的深度很深,这样可以在igbt关断的时候,实现电荷的快速抽取,提升了关断过程中的dv/dt。但是为了增加igbt的电导调制效应,p柱105通常是浮空(floating)的。这个在工艺上面可以通过外延,也可以通过高能量的n型离子注入实现即在p柱105的顶部形成n型掺杂区112。

4、图1中的栅极结构为沟槽栅,包括形成于栅极沟槽内侧表面的栅介质层103以及填充在栅极沟槽中的多晶硅栅104。栅介质层103通常为栅氧化层,通常栅氧化层的厚度在附近。

5、在超结结构的顶部形成有p型的沟道区106,igbt为了降低闩锁效应(latch-up),沟道区106的掺杂浓度通常比较高,沟道区106是通过离子注入形成的,注入的剂量通常在1e13/cm2~1e14/cm2之间。

6、在沟道区106的表面形成有n+掺杂的源区即发射区107,发射区107通常是采用砷(arsenic)注入,注入的剂量通常在1e15/cm2~1e16/cm2之间。发射区107通过金属通孔108跟正面金属层110形成的源极相连。金属通孔108通常是用钨(tungsten)填充形成的。为了使金属通孔108跟沟道区106能够形成很好的欧姆接触,有一通孔注入形成的沟道引出区109,通孔注入通常是采用bf2注入,注入的能量通常在15~100kev之间,注入的剂量通常在1e14/cm2~5e15/cm2之间。

7、sj-igbt的漂移区对应的n型外延层102的掺杂浓度是传统的igbt的5倍以上,其击穿电压主要是靠n型外延层102形成的n柱和p柱5的横向耗尽实现,这样就降低了漂移区的等效掺杂浓度,从而实现相应的击穿电压(bv);因此,其击穿电压主要取决于p柱5的深度t101;通常对于650v的sj-igbt,其深度t101需要大于40μm;而如果要实现1200v的sj-igbt,其深度t101需要大于80μm;这给工艺的实现带来了非常大的难度。

技术实现思路

1、本发明所要解决的技术问题是提供一种超结igbt器件,能提高器件的击穿电压并同时降低工艺难度,能使器件的击穿电压达1200v以上。

2、为解决上述技术问题,本发明提供的超结igbt器件包括:第一导电类型掺杂的第一外延层以及形成于所述第一外延层顶部表面上的第一导电类型掺杂的第二外延层。

3、在所述第二外延层中形成有多个第二导电类型柱,由各所述第二导电类型柱之间的所述第二外延层组成第一导电类型柱;所述第一导电类型柱和所述第二导电类型柱交替排列形成超结结构。

4、所述第二导电类型柱的掺杂浓度和所述第二外延层的掺杂浓度相匹配使所述第一导电类型柱和所述第二导电类型柱的电荷匹配,在器件反偏时,所述超结结构耗尽并形成顶部耐压层。

5、所述第二导电类型柱的底部表面位于所述第一外延层的顶部表面之下,在各所述第二导电类型柱的底部表面之下的所述第一外延层中形成有第二导电类型的第一底部掺杂区。

6、所述第一底部掺杂区和所述第二导电类型柱的延伸到所述第一外延层中的延伸部分相接触且叠加形成第二底部掺杂区,在器件反偏时,各所述第二底部掺杂区对所述第一外延层进行耗尽并形成底部耐压层;所述第二导电类型柱的掺杂浓度具有由工艺产生的波动,所述第一底部掺杂区的掺杂浓度满足在所述第二导电类型柱的掺杂浓度为波动的最低值时依然保证在器件反偏时对所述第一外延层进行耐压所需要的充分耗尽。

7、超结igbt器件的正面结构包括第二导电类型掺杂的沟道区。

8、所述沟道区和所述第二导电类型柱之间具有第一导电类型掺杂的第一顶部掺杂区,所述第一顶部掺杂区使所述第二导电类型柱和所述沟道区相间隔并从而使所述第二导电类型柱呈浮置结构。

9、所述超结igbt器件的背面结构形成于所述第一外延层的背面。

10、进一步的改进是,所述第二导电类型柱的组成结构包括填充于超结沟槽中第二导电类型的第三外延层。

11、进一步的改进是,所述第二导电类型柱的底部表面由所述超结沟槽的底部表面确定,所述超结沟槽的底部表面位于所述第一外延层的顶部表面之下。

12、所述第一底部掺杂区为自对准形成于所述超结沟槽底部的第二导电类型的离子注入区。

13、进一步的改进是,所述第一底部掺杂区的离子注入能量为50kev~200kev,注入剂量为5e11cm-2~2e12cm-2。

14、进一步的改进是,所述第一外延层的电阻率为所述第二外延层的电阻率的5倍以上。

15、进一步的改进是,所述第一外延层的电阻率为所述第二外延层的电阻率的10倍以上。

16、进一步的改进是,所述正面结构还包括:栅极结构、第一导电类型重掺杂的发射区、层间膜、穿过所述层间膜的通孔以及由正面金属层图形化形成的发射极和栅极。

17、所述栅极结构包括栅介质层和栅极导电材料层。

18、所述发射区形成于所述沟道区的表面且和所述栅极结构自对准。

19、所述发射区通过顶部对应的所述通孔和所述发射极连接。

20、所述栅极导电材料层通过顶部对应的所述通孔和所述栅极连接。

21、进一步的改进是,所述发射区对应的所述通孔还穿过所述发射区并和所述沟道区接触;在所述发射区对应的所述通孔的底部还形成有第二导电类型重掺杂的沟道引出区,所述沟道引出区和顶部的所述通孔形成欧姆接触,所述沟道区通过所述沟道引出区和所述通孔接触。

22、进一步的改进是,所述栅极结构采用沟槽栅,所述沟槽栅还包括栅极沟槽,所述栅介质层形成于所述栅极沟槽的内侧表面,所述栅极导电材料层将所述栅极沟槽填充。

23、漂移区的组成部分包括所述沟道区底部的所述第一顶部掺杂区、所述第一导电类型柱和所述第一外延层。

24、所述栅极沟槽纵向穿过所述沟道区,被所述沟槽栅侧面覆盖的所述沟道区的侧面用于形成连接所述发射区和所述漂移区的导电沟道。

25、进一步的改进是,所述栅极结构采用平面栅。

26、在所述超结结构的顶部形成有第一导电类型掺杂的第四外延层,所述第一顶部掺杂区由所述第四外延层组成,所述沟道区形成于所述第四外延层的选定区域中。

27、漂移区的组成部分包括所述沟道区底部的所述第一顶部掺杂区、所述沟道区之间的所述第四外延层以及底部的所述第一导电类型柱和所述第一外延层。

28、所述平面栅形成于所述沟道区的正面并延伸到所述漂移区表面,被所述平面栅正面覆盖的所述沟道区的表面用于形成连接所述发射区和所述漂移区的导电沟道。

29、进一步的改进是,所述超结结构的步进为所述第一导电类型柱的宽度和所述第二导电类型柱的宽度的和。

30、所述沟槽栅的步进为所述栅极沟槽的宽度和所述栅极沟槽的间距的和。

31、所述沟槽栅的步进独立于所述超结结构的步进,使所述沟槽栅的步进小于等于或者大于所述超结结构的步进。

32、进一步的改进是,在至少部分所述栅极沟槽之间还设置有一个以上的发射极沟槽。

33、在所述发射极沟槽的内侧表面形成有第二介质层以及填充有发射极导电材料层,所述发射极导电材料层,所述发射极导电材料层通过顶部对应的所述通孔和所述发射极连接。

34、进一步的改进是,所述正面结构还包括:第一导电类型重掺杂的载流子存储层,所述载流子存储层设置在所述沟道区和所述第一顶部掺杂区之间。

35、进一步的改进是,所述背面结构包括:

36、第二导电类型重掺杂的集电区。

37、在所述集电区的背面形成有背面金属层并由所述背面金属层引出集电极。

38、进一步的改进是,所述背面结构包括:

39、第一导电类型掺杂的缓冲层,所述缓冲层位于所述第一外延层的顶部表面和所述集电区的顶部表面之间,所述缓冲层的掺杂浓度大于所述第一外延层的掺杂浓度,在器件反偏时防止所述第一外延层被完全耗尽时形成器件穿通。

40、进一步的改进是,所述缓冲层通过背面离子注入形成于所述第一外延层的背面,所述缓冲层的背面离子注入的注入能量为100kev~2mev,注入剂量为1e12cm-2~3e13cm-2。

41、进一步的改进是,超结igbt器件为n型器件,第一导电类型为n型,第二导电类型为p型;或者,超结igbt器件为p型器件,第一导电类型为p型,第二导电类型为n型。

42、本发明超结igbt器件在反偏时采用超结结构耗尽形成的顶部耐压层以及超结结构底部的第一外延层耗尽形成的底部耐压层一起实现耐压,这样能提高器件的击穿电压,同时避免单独增加超结结构的厚度来增加耐压时所带来的工艺难度增加的缺陷,所以本发明能在提高器件的击穿电压的同时降低工艺难度,能使器件的击穿电压达1200v以上。

43、本发明中,第一外延层的耗尽是通过采用第二导电类型柱向下延伸到第一外延层中的延伸部分来实现,由于第二导电类型柱的掺杂浓度需要保证满足和第一导电类型柱的电荷匹配的需要,不能根据对第一外延层的耗尽需要来调节第二导电类型柱的掺杂浓度,为了保证对第一外延层实现充分耗尽,本发明在第二导电类型柱的底部增加了第一底部掺杂区,第一底部掺杂区能补偿第二导电类型柱的掺杂浓度波动时对第一外延层的耗尽不足,从而能保证即使在第二导电类型柱的掺杂浓度为波动的最低值时依然能实现对第一外延层的充分耗尽,从而能保证击穿电压达到要求值;另外,第一底部掺杂区能通过离子注入自对准形成于第二导电类型柱的底部,所以具有工艺简单的优点。

44、本发明通过设置第一底部掺杂区很容易实现对第一外延层的充分耗尽,同时为了避免第一外延层完全耗尽所带来的器件穿通问题,本发明还能在第一外延层的底部增加掺杂浓度大于第一外延层的缓冲层,缓冲层能防止器件穿通,同时反过来又有利于第一外延层和第一底部掺杂区的设置,使器件的工艺更加简单。

- 还没有人留言评论。精彩留言会获得点赞!