一种基于TSV转接板的综合电子SIP模块的制作方法

本发明涉及半导体封装,具体涉及一种基于tsv转接板的综合电子sip模块。

背景技术:

1、集成电路产业一直在延续摩尔定律飞速发展,更小尺寸和更高性能的芯片满足了同时期人们对于计算、存储的需求。然而,随着电子产品性能增强、尺寸减小、功能增多、结构复杂、使用环境更加严格多变,摩尔定律发展已然接近物理极限,需要技术革新来弥补当前技术存在的不足。

2、目前,以2.5d和3d封装为主的系统级封装技术与系统芯片的发展正共同推动着新一轮的技术革新。其中,2.5d封装是将芯片在同一平面上排列,然后通过微凸点(microbump)与中介层(interposer)相连,作为中间层的硅基板采用凸点(bump)与基板相连,硅基板表面通过rdl布线、硅通孔(tsv,through siliconvia)作为硅基板上、下表面电气连接的通道,芯片采用倒装焊方式安装在硅基板上,上述2.5d封装方式适合芯片规模较大、引脚密度高的情形,无法满足武器装备中对于高密度、小体积和轻量化的要求。

技术实现思路

1、(一)解决的技术问题

2、针对现有技术所存在的上述缺点,本发明提供了一种基于tsv转接板的综合电子sip模块,能够有效克服现有技术所存在的现有2.5d封装无法满足高密度、小体积和轻量化要求的缺陷。

3、(二)技术方案

4、为实现以上目的,本发明通过以下技术方案予以实现:

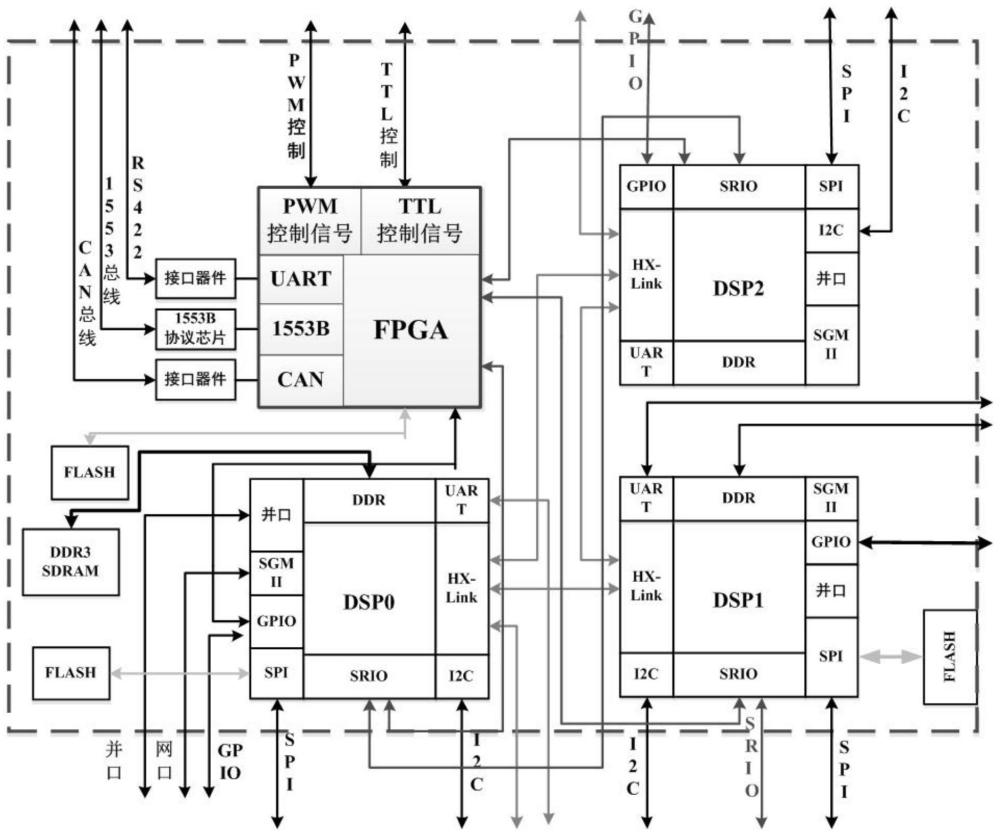

5、一种基于tsv转接板的综合电子sip模块,包括数据处理核心芯片dsp、可编程逻辑阵列fpga、存储芯片、接口芯片和阻容器件,所述数据处理核心芯片dsp、可编程逻辑阵列fpga和存储芯片采用tsv转接板混合封装方式集成在单模块中。

6、优选地,所述存储芯片包括数据存储芯片ddr和程序存储芯片flash,所述程序存储芯片flash通过重布线技术和凸块技术进行加工,制作成倒装焊芯片。

7、优选地,所述数据处理核心芯片dsp与可编程逻辑阵列fpga之间通过srio高速接口通信,所述数据处理核心芯片dsp通过ddr控制器与数据存储芯片ddr连接,所述数据处理核心芯片dsp通过spi外设接口与程序存储芯片flash连接,所述数据处理核心芯片dsp通过倒装焊工艺与tsv转接板连接。

8、优选地,所述可编程逻辑阵列fpga通过低速接口与接口芯片连接,所述接口芯片包括sm3096接口芯片、sm3030接口芯片、smsja1000 can总线芯片和sm164245电平转换芯片。

9、优选地,该综合电子sip模块还包括作为封装外壳的双腔体陶瓷管壳,所述双腔体陶瓷管壳包括正面腔体和背面腔体;

10、所述正面腔体封装有tsv转接板、数据存储芯片ddr、程序存储芯片flash及若干阻容器件,所述tsv转接板上集成有数据处理核心芯片dsp和可编程逻辑阵列fpga,所述tsv转接板、数据存储芯片ddr和程序存储芯片flash通过倒装焊工艺连接于正面腔体上;

11、所述背面腔体封装有sm3096接口芯片、sm3030接口芯片、smsja1000 can总线芯片、sm164245电平转换芯片及若干阻容器件,所述sm3096接口芯片、sm3030接口芯片、smsja1000 can总线芯片和sm164245电平转换芯片通过引线键合技术连接于背面腔体上。

12、优选地,所述tsv转接板包括ubm层、pi2层、m2层、pi1层、m1层、sio2层、tsv层、pi1_b层、m1_b层、pi2_b层和btm_bump层。

13、优选地,所述双腔体陶瓷管壳采用25层陶瓷材料叠层结构,上10层为100μm厚度的倒装焊fc布线区域,下15层为150/200μm厚度的引线键合wb布线区域;

14、其中,双腔体陶瓷管壳的第4、7、10、12、14、16、18、20层为布线层,第3、6、22、24层为电源层,其余层为gnd层。

15、(三)有益效果

16、与现有技术相比,本发明所提供的一种基于tsv转接板的综合电子sip模块,基于tsv转接板,以数据处理核心芯片dsp、可编程逻辑阵列fpga为核心,配合数据存储芯片ddr和程序存储芯片flash,进行数据处理与控制sip模块设计,通过采用tsv转接板、裸芯片重布线、凸块、倒装焊、引线键合等封装技术,让装置体积更小、重量更轻、可靠性更好。

技术特征:

1.一种基于tsv转接板的综合电子sip模块,其特征在于:包括数据处理核心芯片dsp、可编程逻辑阵列fpga、存储芯片、接口芯片和阻容器件,所述数据处理核心芯片dsp、可编程逻辑阵列fpga和存储芯片采用tsv转接板混合封装方式集成在单模块中。

2.根据权利要求1所述的基于tsv转接板的综合电子sip模块,其特征在于:所述存储芯片包括数据存储芯片ddr和程序存储芯片flash,所述程序存储芯片flash通过重布线技术和凸块技术进行加工,制作成倒装焊芯片。

3.根据权利要求2所述的基于tsv转接板的综合电子sip模块,其特征在于:所述数据处理核心芯片dsp与可编程逻辑阵列fpga之间通过srio高速接口通信,所述数据处理核心芯片dsp通过ddr控制器与数据存储芯片ddr连接,所述数据处理核心芯片dsp通过spi外设接口与程序存储芯片flash连接,所述数据处理核心芯片dsp通过倒装焊工艺与tsv转接板连接。

4.根据权利要求3所述的基于tsv转接板的综合电子sip模块,其特征在于:所述可编程逻辑阵列fpga通过低速接口与接口芯片连接,所述接口芯片包括sm3096接口芯片、sm3030接口芯片、smsja1000 can总线芯片和sm164245电平转换芯片。

5.根据权利要求4所述的基于tsv转接板的综合电子sip模块,其特征在于:该综合电子sip模块还包括作为封装外壳的双腔体陶瓷管壳,所述双腔体陶瓷管壳包括正面腔体和背面腔体;

6.根据权利要求1-5中任意一项所述的基于tsv转接板的综合电子sip模块,其特征在于:所述tsv转接板包括ubm层、pi2层、m2层、pi1层、m1层、sio2层、tsv层、pi1_b层、m1_b层、pi2_b层和btm_bump层。

7.根据权利要求5所述的基于tsv转接板的综合电子sip模块,其特征在于:所述双腔体陶瓷管壳采用25层陶瓷材料叠层结构,上10层为100μm厚度的倒装焊fc布线区域,下15层为150/200μm厚度的引线键合wb布线区域;

技术总结

本发明涉及半导体封装,具体涉及一种基于TSV转接板的综合电子SIP模块,包括数据处理核心芯片DSP、可编程逻辑阵列FPGA、存储芯片、接口芯片和阻容器件,数据处理核心芯片DSP、可编程逻辑阵列FPGA和存储芯片采用TSV转接板混合封装方式集成在单模块中;本发明提供的技术方案能够有效克服现有技术所存在的现有2.5D封装无法满足高密度、小体积和轻量化要求的缺陷。

技术研发人员:邢正伟,徐硕,马强,周乐,李岩,高艳丽,白洁雷

受保护的技术使用者:安徽芯纪元科技有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!