微半导体装置及其电子装置的制作方法

本发明涉及一种电子装置,特别是针对微半导体堆叠结构阵列构成的电子装置。

背景技术:

1、一般半导体阵列为沿平面排列,在更小面积的元件需求下,工艺能力的持续精进使工艺可达更小线宽一直是半导体相关制造厂努力的目标,由于产业考虑成本与设备投资的平衡下,最小线宽的推进已趋缓。

2、以微发光二极管显示技术为例,如图1,红、绿、蓝光三个微发光二极管分别为三个次像素110a、120a、130a,在一个平面内相邻排列而形成一个像素100a,多个像素100a阵列组成一个显示器200a。以三个相同尺寸的微发光二极管为例,微发光二极管具长度l、宽度w,像素100a的单位面积受到次像素组合后的总宽度3w的限制,组合后像素宽度p略大于3w,像素面积p*p略大于3w*3w。随着追求高分辨率(有限面积的像素更多),像素长宽纷纷缩小至微米级,纵使如此,仍遭受成本与技术瓶颈,亟待业界提出一种新的解决方式。

技术实现思路

1、有鉴于此,本发明提出一种微半导体堆叠结构及其电子装置,可缩小以微半导体堆叠结构为单元的最小面积,并在电子装置有限面积内提升微半导体堆叠结构阵列的密度。

2、有鉴于此,本发明提出一种微半导体堆叠结构及其电子装置,在电子装置有限面积内同时达到低成本与高分辨率。

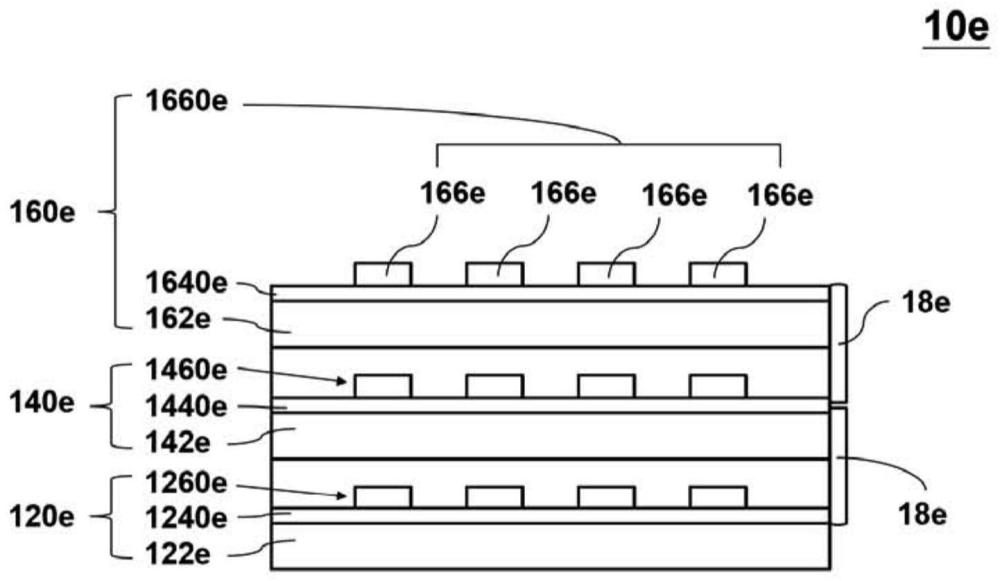

3、一种微半导体堆叠结构包括至少两个层叠结构,其中一个层叠结构叠加于另一层叠结构上。其中,其中一个层叠结构沿另一层叠结构的垂直方向叠加;各层叠结构包括基材、设于基材上的导电图层、以及设于基材上且与导电图层电连接的至少一个微半导体器件。各层叠结构定义目标区域,各层叠结构的微半导体器件设于目标区域内。两两层叠结构间的这些目标区域沿垂直方向彼此对齐;在至少两个层叠结构中的至少一个层叠结构中,导电图层是有源电路。

4、一种微半导体堆叠结构包括三个层叠结构,其中两个层叠结构叠加于最下层层叠结构上;其中:两个层叠结构沿最下层层叠结构的垂直方向叠加;各层叠结构包括基材、设于基材上的导电图层、以及设于基材上且与导电图层电连接的至少一个微发光二极管晶片。各层叠结构定义像素,各层叠结构中的至少一个微发光二极管晶片设于像素内;两两层叠结构间的这些目标区域沿垂直方向彼此对齐;在三个层叠结构的至少一个层叠结构中,导电图层是有源电路。

5、在一些实施例中,一种微半导体堆叠结构,更进一步具有至少一个阶部;沿朝向上层层叠结构或远离下层层叠结构的方向,至少一个阶部由这些基材的尺寸依序渐缩所形成。

6、在一些实施例中,一种微半导体堆叠结构,两两层叠结构的各导电图层以电连接部件连接。

7、在一些实施例中,一种微半导体堆叠结构,至少一个阶部具有电连接部件;两两层叠结构的各导电图层以电连接部件连接。

8、在一些实施例中,一种微半导体堆叠结构,微半导体器件的尺寸范围为1-50um。在一些实施例中,一种微半导体堆叠结构,微发光二极管晶片的尺寸范围为1-50um。

9、在一些实施例中,一种微半导体堆叠结构,这些层叠结构的所述基材是透明的;或者,最下层层叠结构的基材是非透明的。

10、在一些实施例中,一种微半导体堆叠结构,基材是硬质基板、软性基板、或半导体涂覆工艺所形成的介电层。

11、在一些实施例中,一种微半导体堆叠结构,最下层层叠结构的导电图层是有源电路,设有tft或mos开关。

12、在一些实施例中,一种微半导体堆叠结构,各层叠结构的微半导体器件是微发光二极管晶片、微米级光感测晶片、或其组合。

13、在一些实施例中,一种微半导体堆叠结构,沿朝向上层层叠结构或远离下层层叠结构的方向,三个层叠结构的所述微半导体器件依层为红色、绿色、蓝色微发光二极管晶片,且这些微发光二极管晶片的发光侧皆靠近上层层叠结构或远离下层层叠结构。

14、在一些实施例中,一种微半导体堆叠结构,两两层叠结构之间通过胶材接合。

15、在一些实施例中,一种微半导体堆叠结构,胶材平坦化下层层叠结构。

16、一种微半导体堆叠结构包括至少两个层叠结构阵列单元,其中一个层叠结构阵列单元叠加于另一层叠结构阵列单元上;其中一个层叠结构阵列单元沿另一层叠结构阵列单元的垂直方向叠加,各层叠结构阵列单元包括基材、导电图层、以及多个设于基材上阵列排列的多个微半导体器件;各层叠单元包括矩阵电路,这些微半导体器件电连接矩阵电路。各层叠结构阵列单元定义有以阵列排列的多个目标区域;在各层叠结构阵列单元中,这些微半导体器件的至少一个对应并位于这些目标区域的其中一个目标区域内;在两两层叠结构阵列单元之间,上层层叠结构阵列单元的所述目标区域个别对应、并沿该垂直方向对齐下层层叠结构阵列单元的所述目标区域;在三个层叠结构阵列单元的至少一个层叠结构阵列单元中,导电图层的该矩阵电路是有源式矩阵电路。

17、一种微半导体堆叠结构包括三个层叠结构阵列单元,其中两个层叠结构阵列单元叠加于最下层层叠结构阵列单元上;其中:两个层叠结构阵列单元沿最下层层叠结构阵列单元的垂直方向叠加,各层叠结构阵列单元包括基材、导电图层、以及多个设于基材上阵列排列的多个微发光二极管晶片;这些导电图层包括矩阵电路,这些微发光二极管晶片电连接矩阵电路。各层叠结构阵列单元定义有以阵列排列的多个像素,在各层叠结构阵列单元中,这些微发光二极管晶片的至少一个对应并位于这些像素的其中一个像素内;在两两层叠结构阵列单元之间,上层层叠结构阵列单元的所述像素个别对应、并沿垂直方向对齐下层层叠结构阵列单元的所述像素;在三个层叠结构阵列单元的至少一个层叠结构阵列单元中,该导电图层的该矩阵电路是有源式矩阵电路。

18、在一些实施例中,一种微半导体堆叠结构,更进一步具有至少一个阶部;其中:沿朝向上层层叠结构阵列单元或远离下层层叠结构阵列单元的方向,至少一个阶部由这些基材的尺寸依序渐缩所形成。

19、在一些实施例中,一种微半导体堆叠结构,在两两层叠结构阵列单元间,上层层叠结构阵列单元的所述导电图层以至少一个电连接部件连接下层层叠结构阵列单元的所述导电图层。

20、在一些实施例中,一种微半导体堆叠结构,该至少一个阶部具有电连接部件;在两两层叠结构阵列单元间,上层层叠结构阵列单元的所述导电图层以电连接部件连接下层层叠结构阵列单元的所述导电图层。

21、一种微半导体堆叠结构,微半导体器件的尺寸范围为1-50um。

22、在一些实施例中,一种微半导体堆叠结构,各微发光二极管晶片的尺寸范围为1-50um。

23、在一些实施例中,一种微半导体堆叠结构,这些层叠结构阵列单元的所述基材是透明的;或者,最下层层叠结构阵列单元的所述基材是非透明的。

24、在一些实施例中,一种微半导体堆叠结构,这些层叠结构阵列单元的所述基材为硬质基板、软性基板。

25、在一些实施例中,一种微半导体堆叠结构,两两层叠结构阵列单元之间通过胶材接合。

26、在一些实施例中,一种微半导体堆叠结构,胶材平坦化下层层叠结构。

27、在一些实施例中,一种微半导体堆叠结构,这些层叠结构阵列单元的所述基材是半导体涂覆工艺所形成的介电层。

28、在一些实施例中,一种微半导体堆叠结构,最下层层叠结构阵列单元的所述导电图层是有源式矩阵电路,设有tft或mos开关。

29、在一些实施例中,一种微半导体堆叠结构,各层叠结构阵列单元的微半导体器件是微发光二极管晶片、微米级光感测晶片、或其组合。

30、在一些实施例中,一种微半导体堆叠结构,沿朝向上层层叠结构阵列单元或远离下层层叠结构阵列单元的方向,三层层叠结构阵列单元依单元设置有红色、绿色、蓝色微发光二极管晶片,且这些微发光二极管晶片的发光侧靠近上层层叠结构阵列单元或远离下层层叠结构阵列单元。

31、在一些实施例中,一种电子装置包括多个微半导体堆叠结构以阵列排列,以及外部电控结构,电连接至少一个层叠结构的所述导电图层。

32、在一些实施例中,一种电子装置包括微半导体堆叠结构,以及外部电控结构,电连接至少一个层叠结构的所述导电图层。

33、在一些实施例中,一种电子装置包括微半导体堆叠结构,以及至少一个外部电控结构,电连接至少一个层叠结构阵列单元的所述导电图层。

- 还没有人留言评论。精彩留言会获得点赞!