一种测试芯片的封装方法与流程

本技术涉及半导体封装技术的领域,尤其是涉及一种测试芯片的封装方法。

背景技术:

1、晶圆级封装(waferlevelpackaging,wlp)属于“晶圆封装后再切割”的方式,采用了集成电路芯片制造厂中的晶圆作业模式,即在整片晶圆上完成封装后再切割,一次性得到大量成品芯片。

2、晶圆级封装,第一凸点质量主要通过电性能还有外观,结合力来表征。在封装制程中会插入各种测试,用来检验质量。漏电流测试又叫leakage测试,测试的意义在于在 长完bump后检测芯片的open-short 状况,有效防止芯片电性能测试出现大面积电失效问题。是晶圆级封装中重要的检测手段。

3、现有技术中存在以下问题,每种芯片因为设计不同使得检测位置会不同,但是检测位置的差异会影响检测结果,导致测试结果不在同一个水平体现,无法尚有改进的空间。

技术实现思路

1、为了改善芯片因为设计不同使得检测位置会不同,但是检测位置的差异会影响检测结果,导致测试结果不在同一个水平体现的问题,本技术提供一种测试芯片的封装方法。

2、第一方面,本技术提供一种测试芯片的封装方法,采用如下的技术方案:

3、一种测试芯片的封装方法,应用于不具有再布线结构的芯片上,包括:

4、提取第一集成电路晶圆并于第一集成电路晶圆裸露出第一电极的一侧覆盖第一介电层,所述第一集成电路晶圆上设有第一待成型芯片,所述第一待成型芯片上设有第一电极和第一电路模块,所述第一集成电路晶圆上覆盖有第一钝化层,所述第一钝化层远离第一集成电路晶圆的一侧设有露出第一电极的第一开口;

5、于第一介电层远离第一集成电路晶圆的一侧溅射第一金属ticu层;

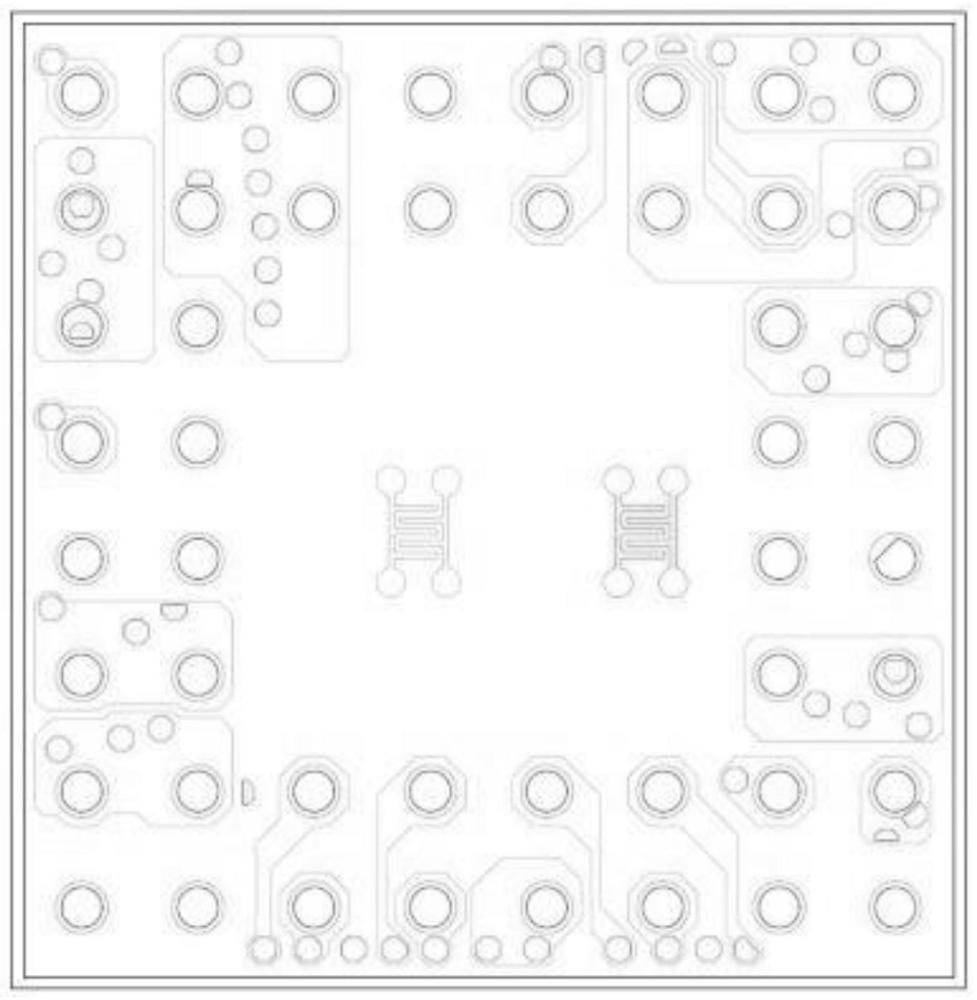

6、将预设的第一掩模版上的图像进行光刻以在第一金属ticu层上形成第一光刻层,所述第一光刻层包括预设的第一设计芯片图像和第一测试芯片图像;

7、于第一光刻层上电镀第一ubm金属层;

8、依次去除第一光刻层和第一金属ticu层,以露出成型为第一设计芯片图像和第一测试芯片图像的第一电镀金属层;

9、于第一电镀金属层上形成第一凸点,所述形成工艺为植球工艺或者回流工艺;

10、于经过检测后将第一集成电路晶圆切割成单个第一芯片,所述第一芯片包括具有第一设计芯片图像的设计芯片和具有第一测试芯片图像的第一测试芯片。

11、通过采用上述技术方案,通过在封装过程中设计中心有特殊图像的测试芯片,从而在测试芯片上进行漏电检测,不受芯片表面图形设计的限制,使得每次检测都处于同一个水平,检测结果较为准确且判断依据标准化,提高了检测的效率。

12、可选的,所述第一测试芯片图像包括设置于不同第一测试芯片上的第一漏电测试图像和第一剪切力测试图像,所述第一剪切力测试图像设置于第一光刻层的边缘处,包含有第一漏电测试图像的所述第一测试芯片上设置有与外界连接进行电路测试的触点和相同线宽线距且连接两个触点的中间走线。

13、通过采用上述技术方案,由于漏电检测过程不干扰剪切力检测过程,故可以在同一个封装过程中同时设计漏电测试图像和剪切力测试图像,提高了封装检测的效率。

14、可选的,所述第一测试芯片图像上包括设置于同一测试芯片上的第一漏电测试图像和第一剪切力测试图像,所述第一剪切力测试图像设置于第一光刻层的边缘处,包含有第一漏电测试图像的所述第一测试芯片上设置有与外界连接进行电路测试的第一触点和相同线宽线距且连接两个第一触点的第一中间走线。

15、通过采用上述技术方案,由于漏电测试芯片一般也不是需要的芯片,故可以将两种不同检测的图案设计在同一个芯片上,从而尽可能减少测试芯片的需求数量,提高了芯片的封装良率。

16、可选的,设置有第一剪切力测试图像的所述第一测试芯片设于预设的第一有效范围的边缘线上且部分超出第一有效范围外。

17、通过采用上述技术方案,由于在有效范围的边缘线上,故一般这些芯片也会在后期被切割掉而报废,将测试芯片设计在边缘无效位置,避免有效芯片良率损失,提升封装良率。

18、第二方面,本技术提供一种测试芯片的封装方法,采用如下的技术方案:

19、一种测试芯片的封装方法,应用于具有再布线结构的芯片上,包括:

20、提取第二集成电路晶圆并于第二集成电路晶圆裸露出第二电极的一侧覆盖第二介电层,所述第二集成电路晶圆上设有第二待成型芯片,所述第二待成型芯片上设有第二电极和第二电路模块,所述第二集成电路晶圆上覆盖有第二钝化层,所述第二钝化层的一侧设有露出第二电极的第二开口;

21、于第二介电层远离第二集成电路晶圆的一侧溅射第二金属ticu层;

22、将预设的第二掩模版上的图像进行光刻以在第二金属ticu层上形成第二光刻层,所述第二光刻层包括预设的第二设计芯片图像和第二测试芯片图像,所述第二测试芯片图像包括第二漏电测试图像;

23、于第二光刻层上电镀再布线层;

24、于再布线层上电镀第二ubm金属层;

25、依次去除第二光刻层和第二金属ticu层,以露出成型为第二设计芯片图像和第二测试芯片图像的第二电镀金属层;

26、于第二电镀金属层上形成第二凸点,所述形成工艺为植球工艺或者回流工艺;

27、于经过检测后将第二集成电路晶圆切割成单个第二芯片,所述第二芯片包括具有第二设计芯片图像的设计芯片和具有第二测试芯片图像的第一测试芯片,所述第二测试芯片上设置有与外界连接进行电路测试的触点和相同线宽线距且连接两个触点的中间走线。

28、通过采用上述技术方案,通过在封装过程中设计中心有特殊图像的测试芯片,从而在测试芯片上进行漏电检测,不受芯片表面图形设计的限制,使得每次检测都处于同一个水平,检测结果较为准确且判断依据标准化,提高了检测的效率。

29、可选的,于第二光刻层上电镀再布线层的步骤和于再布线层上电镀第二ubm金属层的步骤之间还包括以下步骤:

30、继续于再布线层上涂覆第三介电层并溅射第三金属ticu层;

31、于第二集成电路晶圆裸露出第二电极的一侧覆盖第三介电层;

32、于第三介电层远离第二集成电路晶圆的一侧溅射第三金属ticu层;

33、将预设的第三掩模版上的图像进行光刻以在第三金属ticu层上形成第三光刻层,所述第三光刻层包括预设的第三测试芯片图像,所述第三测试芯片图像包括第二剪切力测试图像。

34、通过采用上述技术方案,由于漏电检测过程不干扰剪切力检测过程,故可以在同一个封装过程中同时设计漏电测试图像和剪切力测试图像,提高了封装检测的效率。

35、可选的,所述第二漏电测试图像和所述第二剪切力测试图像在将第二集成电路晶圆切割成单个第二芯片的步骤后位于同一个第二测试芯片上。

36、通过采用上述技术方案,由于漏电测试芯片一般也不是需要的芯片,故可以将两种不同检测的图案设计在同一个芯片上,从而尽可能减少测试芯片的需求数量,提高了芯片的封装良率。

37、可选的,还包括是否继续于再布线层上涂覆第三介电层并溅射第三金属ticu层的步骤的判断方法,该方法包括:

38、执行预设的漏电流检测方法并获取漏电流检测结果;

39、基于漏电流检测结果分析异常可能原因;

40、基于异常可能原因从预设的检测数据库中查找到对应的检测方案;

41、执行检测方案后确定准确异常原因;

42、基于准确异常原因从预设的处理数据库中查找到对应的处理方案;

43、于处理方案所对应的处理类型为预设的继续刻蚀类别时执行处理方案并重新获取漏电流检测结果;

44、于漏电流检测结果为预设的正常结果时执行继续于再布线层上涂覆第三介电层并溅射第三金属ticu层的步骤;

45、于处理方案所对应的处理类型为机器调整类别时输出处理方案并不再执行继续于再布线层上涂覆第三介电层并溅射第三金属ticu层的步骤。

46、通过采用上述技术方案,在封装过程中当已经可以进行漏电检测时,则直接开始漏电检测,若检测结果没有问题或者可以解决,那么才可以执行剪切测试的步骤,若检测结果有问题且无法解决,则说明晶圆本身已经报废或者需要很久时间的解决,那么此时晶圆无需进行下一步操作而搁置于一旁,减少了晶圆封装的不良率。

47、可选的,还包括第二掩模版上第二测试芯片图像的布置方法,该方法包括:

48、确定可选芯片位置以及可选数量,所述可选芯片位置为落在预设的第二有效范围的边缘线上且部分超出第二有效范围外的第二待成型芯片所对应的第二掩模版上的位置;

49、于可选数量大于预设的检测要求数量时将可选芯片位置作为第二测试芯片图像进行输出;

50、于可选数量小于检测要求数量时分析第二设计芯片图像以得到设计图像编号;

51、基于设计图像编号从预设的需求数据库中查找到对应的设计需求数量;

52、统计设计图像编号的数量,将该数量定义为设计实际数量;

53、于设计实际数量大于设计需求数量时基于可选数量和检测要求数量计算出需求数量差;

54、基于设计实际数量和设计需求数量确定实际数量差;

55、于需求数量差小于实际数量差时分析统计图像编号确定最外围图像编号和外围芯片位置;

56、任意选择需求数量差对应的外围芯片位置和可选数量对应的可选芯片位置作为第二测试芯片图像的位置进行输出。

57、通过采用上述技术方案,当在边缘线上的测试芯片数量不够时,则若有些设计芯片的数量有多余的,则在多余的设计芯片上进行测试,保证测试芯片的测试数量。

58、可选的,还包括第二掩模版上第二测试芯片图像的进一步布置方法,该方法包括:

59、于可选数量小于检测要求数量时分析第二测试芯片图像以得到测试图像编号;

60、基于最外围图像编号和测试图像编号从预设的比较数据库中查找到对应的等同替换可能性;

61、于存在大于预设的不影响概率的等同替换可能性时将该等同替换可能性对应的最外围图像编号定义为等同设计图像编号,将该等同替换可能性对应的测试图像编号定义为等同测试图像编号;

62、基于等同测试图像编号对应的第二测试芯片图像和等同设计图像编号对应的第二设计芯片图像进行局部更新以得到更新漏电测试图像;

63、统计等同设计图像编号对应的芯片数量;

64、计算芯片数量和可选数量之和,将该和定义为可选总数量;

65、于可选总数量小于检测要求数量时继续查找等同测试图像编号并更新可选总数量;

66、于可选总数量大于预设的最低漏电检测要求数量且需求数量差和可选数量之和大于预设的最低剪切力要求数量时将可选芯片位置作为第二漏电测试图像进行输出,且将等同设计图像编号对应的第二设计芯片图像所对应的第二掩模版上的位置作为更新漏电测试图像对应的位置进行输出。

67、通过采用上述技术方案,将部分和测试图像相似的设计芯片进行更新并得到测试芯片时,在不影响剪切力测试需求的同时若漏电测试结果满足需求,仍然可以作为正常芯片进行使用,节约了芯片成本,提高了芯片的使用率。

68、综上所述,本技术包括以下至少有益技术效果:

69、1.通过在封装过程中设计中心有特殊图像的测试芯片,使得每次检测都处于同一个水平,检测结果较为准确且判断依据标准化,提高了检测的效率;

70、2.在同一个封装过程中同时设计漏电测试图像和剪切力测试图像,提高了封装检测的效率;

71、3.将两种不同检测的图案设计在同一个芯片上,从而尽可能减少测试芯片的需求数量,提高了芯片的封装良率。

- 还没有人留言评论。精彩留言会获得点赞!