一种芯片堆叠结构、芯片堆叠结构的形成方法及相关设备与流程

本技术涉及芯片,具体涉及一种芯片堆叠结构、芯片堆叠结构的形成方法及相关设备。

背景技术:

1、2.5d&3d堆叠和封装技术,可以极大地提高芯片的封装集成度,减小封装尺寸,是目前最为重要的封装技术和发展方向。现有技术是通过ubump(under bump metallurgy,底部导电化)实现裸芯片的垂直堆叠互连,芯片间通过通孔进行电信号的连接。

2、然而,现有的封装结构过于复杂且工艺兼容性较低。

技术实现思路

1、有鉴于此,本技术实施例提供一种芯片堆叠结构、芯片堆叠结构的形成方法及相关设备,以提升工艺兼容性。

2、为实现上述目的,本技术实施例提供如下技术方案。

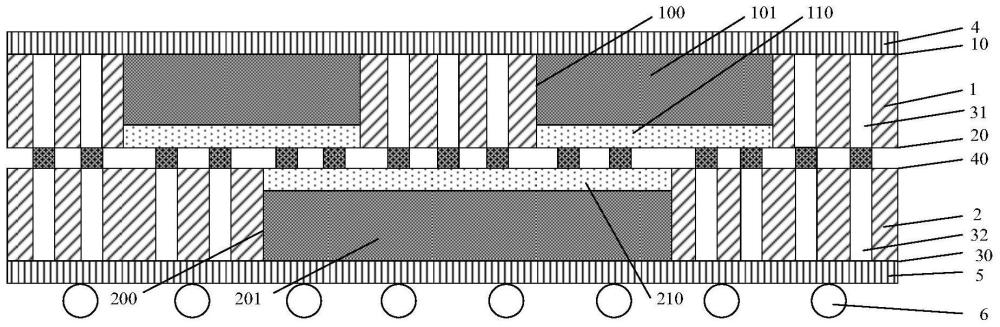

3、第一方面,本技术实施例提供一种芯片堆叠结构,包括:

4、第一转接板,贯穿所述第一转接板的第一芯片容纳腔;

5、位于所述第一芯片容纳腔内依次堆叠的第一芯片和第一导电层;其中,以所述第一转接板暴露所述第一芯片的一面为第一表面,以所述第一转接板暴露所述第一导电层的一面为第二表面;

6、第二转接板,贯穿所述第二转接板的第二芯片容纳腔;

7、位于所述第二芯片容纳腔内依次堆叠的第二芯片和第二导电层;其中,以所述第二转接板暴露所述第二芯片的一面为第三表面,以所述第二转接板暴露所述第二导电层的一面为第四表面;

8、所述第二表面和所述第四表面键合连接。

9、可选地,所述第一转接板设置有多个第一芯片容纳腔,所述第二转接板至少设置有1个第二芯片容纳腔,其中,所述第一芯片容纳腔在所述第二转接板的投影,基于所述第二芯片容纳腔的中心对称分布。

10、可选地,还包括:

11、位于所述第一转接板第一表面上的第一重布线层,所述第一重布线层用于实现所述第一转接板的信号的再分布和转接;

12、位于所述第二转接板第三表面上的第二重布线层,所述第二重布线层用于实现所述第二转接板的信号的再分布和转接。

13、可选地,所述第一转接板中,在第一芯片容纳腔以外的区域设置有第一通孔,所述第一通孔内设置有贯穿所述第一转接板的第一导电插塞;所述第二转接板中,在第二芯片容纳腔以外的区域设置有第二通孔,所述第二通孔内设置有贯穿所述第二转接板的第二导电插塞。

14、可选地,所述第二表面和所述第四表面键合连接,具体为:

15、所述第一导电插塞键合至所述第二导电插塞或者所述第二导电层,所述第二导电插塞键合至所述第一导电插塞或者所述第一导电层。

16、可选地,所述第二表面和所述第四表面键合连接的方式为导电柱体、导电凸块和混合键合中的一种。

17、可选地,所述第一转接板的厚度与所述第一芯片和所述第一导电层的厚度之和相同,所述第二转接板的厚度与所述第二芯片和所述第二导电层的厚度之和相同。

18、可选地,所述第一芯片的活性面朝向所述第二表面,所述第二芯片的活性面朝向所述第四表面。

19、第二方面,本技术实施例提供一种芯片堆叠结构的形成方法,包括:

20、提供第一转接板;

21、在所述第一转接板上形成贯穿所述第一转接板的第一芯片容纳腔;

22、在所述第一芯片容纳腔内形成依次堆叠的第一芯片和第一导电层;其中,以所述第一转接板暴露所述第一芯片的一面为第一表面,以所述第一转接板暴露所述第一导电层的一面为第二表面;

23、提供第二转接板;

24、在所述第二转接板上形成贯穿所述第二转接板的第二芯片容纳腔;

25、在所述第二芯片容纳腔内形成依次堆叠的第二芯片和第二导电层;其中,以所述第二转接板暴露所述第二芯片的一面为第三表面,以所述第二转接板暴露所述第二导电层的一面为第四表面;

26、键合所述第二表面和所述第四表面。

27、可选地,所述在所述第一转接板上形成贯穿所述第一转接板的第一芯片容纳腔的步骤中,所述第一芯片容纳腔为多个;

28、所述在所述第二转接板上形成贯穿所述第二转接板的第二芯片容纳腔的步骤中,所述第二芯片容纳腔为至少1个;

29、其中,所述第一芯片容纳腔在所述第二转接板的投影,基于所述第二芯片容纳腔的中心对称分布。

30、可选地,所述键合所述第二表面和所述第四表面之后,还包括:

31、在所述第一转接板第一表面上形成第一重布线层,所述第一重布线层用于实现所述第一转接板的信号的再分布和转接;

32、在所述第二转接板第三表面上形成第二重布线层,所述第二重布线层用于实现所述第二转接板的信号的再分布和转接。

33、可选地,所述在所述第一转接板上形成贯穿所述第一转接板的第一芯片容纳腔的步骤之后,所述在所述第一芯片容纳腔内形成依次堆叠的第一芯片和第一导电层的步骤之前,还包括:

34、在所述第一转接板中所述第一芯片容纳腔以外的区域形成第一通孔;

35、在所述第一通孔内形成贯穿所述第一转接板的第一导电插塞。

36、可选地,所述在所述第二转接板上形成贯穿所述第二转接板的第二芯片容纳腔的步骤之后,所述在所述第二芯片容纳腔内形成依次堆叠的第二芯片和第二导电层的步骤之前,还包括:

37、在所述第二转接板中所述第二芯片容纳腔以外的区域形成第二通孔;

38、在所述第二通孔内形成贯穿所述第二转接板的第二导电插塞。

39、可选地,所述键合所述第二表面和所述第四表面的步骤,具体为:

40、将所述第一导电插塞键合至所述第二导电插塞或者所述第二导电层,将所述第二导电插塞键合至所述第一导电插塞或者所述第一导电层。

41、可选地,所述键合所述第二表面和所述第四表面的步骤中,采用的键合方式为导电柱体、导电凸块和混合键合中的一种。

42、可选地,所述第一转接板的厚度与所述第一芯片和所述第一导电层的厚度之和相同,所述第二转接板的厚度与所述第二芯片和所述第二导电层的厚度之和相同。

43、可选地,所述第一芯片的活性面朝向所述第二表面,所述第二芯片的活性面朝向所述第四表面。

44、第三方面,本技术实施例提供一种芯片堆叠封装,包括:

45、封装基板,所述封装基板的表面设置有芯片堆叠结构,所述芯片堆叠结构为前述第一方面所述的芯片堆叠结构,其中,所述芯片堆叠结构中的第二转接板相对第一转接板靠近所述封装基板。

46、可选地,所述芯片堆叠结构中的第二重布线层上设置有焊球,所述焊球用于实现与所述封装基板的电性连接。

47、第四方面,本技术实施例提供一种电子设备,包括:

48、印制电路板;

49、如上述第三方面所述的芯片堆叠封装,所述印制电路板与所述芯片堆叠封装电连接。

50、与现有技术相比,本技术实施例的技术方案具有以下优点:

51、本技术实施例提供了一种芯片堆叠结构、芯片堆叠结构的形成方法及相关设备,其中,所述芯片堆叠结构,包括:第一转接板,贯穿所述第一转接板的第一芯片容纳腔;位于所述第一芯片容纳腔内依次堆叠的第一芯片和第一导电层;其中,以所述第一转接板暴露所述第一芯片的一面为第一表面,以所述第一转接板暴露所述第一导电层的一面为第二表面;第二转接板,贯穿所述第二转接板的第二芯片容纳腔;位于所述第二芯片容纳腔内依次堆叠的第二芯片和第二导电层;其中,以所述第二转接板暴露所述第二芯片的一面为第三表面,以所述第二转接板暴露所述第二导电层的一面为第四表面;所述第二表面和所述第四表面键合连接。

52、可以看出,本技术实施例所提供的芯片堆叠结构,通过把第一芯片嵌入第一转接板的第一芯片容纳腔内、把第二芯片嵌入第二转接板的第二芯片容纳腔内,再将所述第二表面和所述第四表面键合连接,实现所述第一转接板与所述第二转接板的堆叠,进而实现第一芯片与第二芯片之间的面对面堆叠。本技术实施例通过采用转接板的堆叠方式,可以更加容易的实现芯片之间的面对面堆叠,从而降低了工艺的复杂性,提高了工艺的兼容性。

- 还没有人留言评论。精彩留言会获得点赞!