阵列基板、显示面板及显示装置的制作方法

本公开涉及显示,尤其涉及一种阵列基板、显示面板及显示装置。

背景技术:

1、目前,oled(organic light-emitting diode,有机发光二极管)显示装置因其具有自发光、快速响应、宽视角和可制作在柔性衬底上等特点,受到广泛应用,oled显示装置包括多个子像素,各子像素包括像素驱动电路和发光器件,通过像素驱动电路驱动发光器件发光,从而实现显示。

技术实现思路

1、本公开的实施例的目的在于提供一种阵列基板、显示面板及显示装置,用于提高显示面板的ppi。

2、为达到上述目的,本公开的实施例提供了如下技术方案:

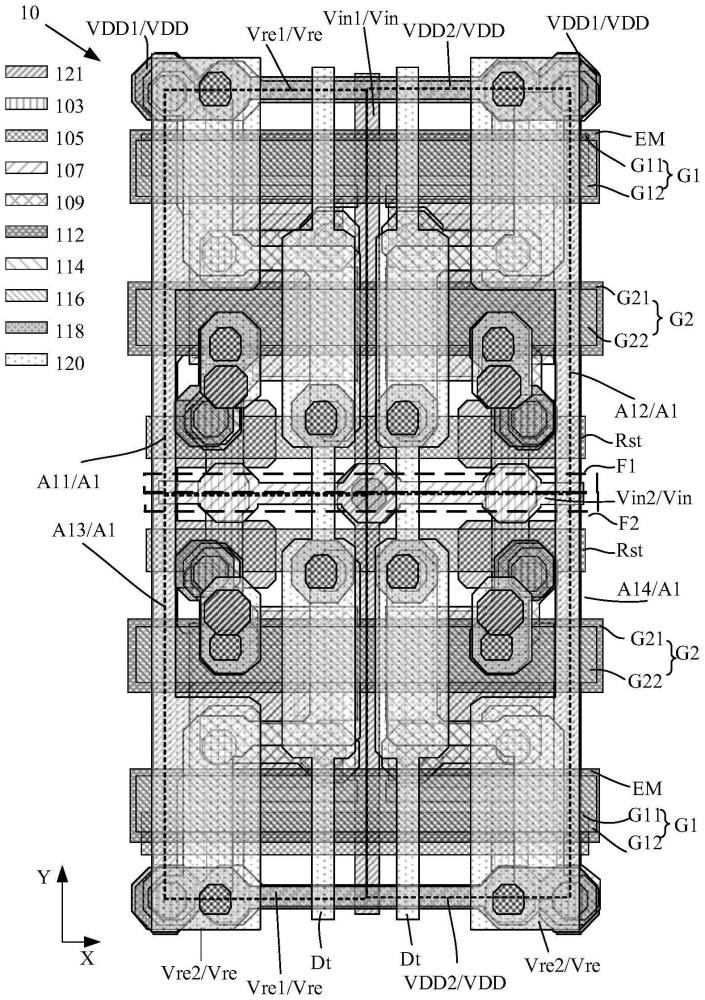

3、一方面,提供一种阵列基板,阵列基板包括:多个子像素区域,每个子像素区域中设置有一个像素驱动电路,多个像素驱动电路呈多行多列排布,所述多个像素驱动电路中的每个像素驱动电路包括多个第一类晶体管和多个第二类晶体管。所述阵列基板包括:衬底基板、设置于所述衬底基板一侧的第一有源膜层以及设置于所述第一有源膜层远离所述衬底基板一侧的第二有源膜层,所述第一有源膜层包括所述多个第一类晶体管的有源层图案,所述第二有源膜层包括所述多个第二类晶体管的有源层图案。且,相邻行子像素区域的膜层图案镜像设置,相邻列子像素区域的膜层图案镜像设置。所述阵列基板还包括:多条直流信号线,与所述多条直流信号线中的一条直流信号线相邻的两列所述子像素区域的像素驱动电路共用该直流信号线;与所述多条直流信号线中的一条直流信号线相邻的两行所述子像素区域的像素驱动电路共用该直流信号线。

4、上述阵列基板中,采用相邻行子像素区域的膜层图案镜像设置,相邻列子像素区域的膜层图案镜像设置可以实现直流信号线的共用,从而能够减少阵列基板中所设置的直流信号线的数量,减少布线,进一步能够使得相邻像素驱动电路设置更加紧凑,减小相邻像素驱动电路的间距,从而能够减小多个子像素区域的总面积,进一步降低了多个子像素所占的空间,有利于提高显示面板的ppi。

5、在一些实施例中,阵列基板还包括:设置于所述衬底基板和所述第一有源膜层之间的遮挡层和设置于所述第一有源膜层和所述第二有源膜层之间的第二栅金属层,所述遮挡层包括沿所述列方向延伸的多条第一电压信号线第一支线和多条初始化信号线第一支线,所述第二栅金属层包括沿所述行方向延伸的多条第一电压信号线第二支线和多条初始化信号线第二支线。所述多条第一电压信号线第二支线中的每条第一电压信号线第二支线与所述多条第一电压信号线第一支线通过过孔连接;所述多条初始化信号线第二支线中的每条初始化信号线第二支线与所述多条初始化信号线第一支线通过过孔连接。

6、在一些实施例中,与一条所述第一电压信号线第一支线相邻的两列所述子像素区域的像素驱动电路共用该第一电压信号线第一支线;与一条所述第一电压信号线第二支线相邻的两行所述子像素区域的像素驱动电路共用该第一电压信号线第二支线。

7、在一些实施例中,与一条所述初始化信号线第一支线相邻的两列所述子像素区域的像素驱动电路共用该初始化信号线第一支线;与一条所述初始化信号线第二支线相邻的两行所述子像素区域的像素驱动电路共用该初始化信号线第二支线。

8、在一些实施例中,在所述子像素区域中,所述第一类晶体管包括:发光控制晶体管和第二复位晶体管所述发光控制晶体管的有源层图案与所述第一电压信号线第二支线连接;所述第二复位晶体管的有源层图案与所述初始化信号线第二支线连接。

9、在一些实施例中,所述第一类晶体管还包括:驱动晶体管,所述发光控制晶体管的有源层图案、所述驱动晶体管的有源层图案和所述第二复位晶体管的有源层图案依次连接。

10、在一些实施例中,所述像素驱动电路还包括电容器;所述第二栅金属层还包括所述电容器的第二极板图案。所述阵列基板还包括:设置于所述第一有源膜层和所述第二栅金属层之间的第一栅金属层,所述第一栅金属层包括:所述电容器的第一极板图案。所述阵列基板还包括:设置于所述第二栅金属层和所述第二有源膜层之间的第一源漏金属层,所述第一源漏金属层包括第一转接图案,所述第一转接图案通过过孔与所述第二复位晶体管的有源层图案连接,且同时与所述电容器的第二极板图案连接。

11、在一些实施例中,阵列基板还包括:设置于所述第二有源膜层远离所述衬底基板一侧的第二源漏金属层和设置于所述第二源漏金属层远离所述衬底基板一侧的第三源漏金属层,所述第二源漏金属层包括第三转接图案,所述第三源漏金属层包括第四转接图案,所述第二有源膜层还包括第二转接图案。所述第一转接图案、所述第二转接图案、所述第三转接图案和所述第四转接图案通过过孔依次连接。

12、在一些实施例中,所述第一栅金属层还包括:发光控制信号线和复位信号线,所述发光控制信号线经过所述发光控制晶体管的有源层图案,所述复位信号线经过所述第二复位晶体管的有源层图案。

13、在一些实施例中,所述遮挡层还包括:第一遮光图案;所述第一遮光图案与所述第一电压信号线第一支线连接,所述驱动晶体管在所述衬底基板的正投影位于所述第一遮光图案在所述衬底基板的正投影内;和/或,所述遮挡层还包括:第二遮光图案,所述第二遮光图案与所述第一电压信号线第一支线连接,所述第二复位晶体管在所述衬底基板的正投影位于所述第二遮光图案在所述衬底基板的正投影内。

14、在一些实施例中,阵列基板还包括:设置于所述第二有源膜层远离所述衬底基板一侧的第二源漏金属层和设置于所述第二源漏金属层远离所述衬底基板一侧的第三源漏金属层,所述第二源漏金属层包括沿所述行方向延伸的多条第二电压信号线第一支线,所述第三源漏金属层包括沿所述列方向延伸的多条第二电压信号线第二支线。所述多条第二电压信号线第一支线中的每条第二电压信号线第一支线与所述多条第二电压信号线第二支线通过过孔连接。

15、在一些实施例中,与一条所述第二电压信号线第一支线相邻的两列所述子像素区域的像素驱动电路共用该第二电压信号线第一支线;与一条所述第二电压信号线第二支线相邻的两列所述子像素区域的像素驱动电路共用该第二电压信号线第二支线。

16、在一些实施例中,在所述子像素区域中,所述第二类晶体管包括:第一复位晶体管,所述第一复位晶体管的有源层图案与所述第二电压信号线第一支线连接。

17、在一些实施例中,所述第二类晶体管还包括:写入晶体管,所述写入晶体管的有源层图案与所述第一复位晶体管的有源层图案连接。

18、在一些实施例中,所述像素驱动电路还包括电容器;所述阵列基板还包括:设置于所述第一有源膜层和所述第二有源膜层之间的第一栅金属层,以及设置于所述第一栅金属层和所述第二有源膜层之间的第一源漏金属层。所述第一栅金属层包括:所述电容器的第一极板图案,所述第一源漏金属层包括第五转接图案。所述第五转接图案通过过孔与所述第一极板图案连接,且所述第五转接图案通过过孔与所述写入晶体管的有源层图案连接,以使所述第一极板图案与所述写入晶体管的有源层图案连接。

19、在一些实施例中,所述第二有源膜层还包括第二转接图案,所述第三源漏金属层包括:数据信号线和第四转接图案,所述数据信号线与所述写入晶体管的有源层图案通过第一节点图案连接,所述第四转接图案与所述第二转接图案通过第二节点图案连接。其中,沿所述行方向,所述第一节点图案和所述第二节点图案的之间的尺寸与所述子像素区域膜层图案的尺寸的比值大于或等于30%。

20、在一些实施例中,阵列基板还包括:设置于所述第一有源膜层和所述第二有源膜层之间的第三栅金属层,以及设置于所述第二有源膜层和所述第二源漏金属层之间的第四栅金属层;其中,所述第三栅金属层包括第一扫描信号线第一支线和第二扫描信号线第一支线,所述第四栅金属层包括第一扫描信号线第二支线和第二扫描信号线第二支线,所述第一扫描信号线第一支线和所述第一扫描信号线第二支线经过所述第一复位晶体管的有源层图案,所述第二扫描信号线第一支线和所述第二扫描信号线第二支线经过所述写入晶体管的有源层图案。所述第一扫描信号线第一支线和所述第一扫描信号线第二支线电连接;所述第二扫描信号线第一支线和所述第二扫描信号线第二支线电连接。

21、在一些实施例中,所述第一有源膜层为低温多晶硅层,所述第二有源膜层为氧化物层。

22、在一些实施例中,阵列基板还包括:设置于所述第一有源膜层和所述第二有源膜层之间的第一平坦层,所述第一平坦层的材料包括有机材料,所述第一平坦层的厚度范围为1.5μm~2μm;或,所述第一平坦层的材料包括无机材料,所述第一平坦层的厚度范围为1.2μm~1.5μm。

23、另一方面,提供一种显示面板。所述显示面板包括:如上述任一实施例所述的阵列基板。

24、上述显示面板具有与上述一些实施例中提供的阵列基板相同的结构和有益技术效果,在此不再赘述。

25、又一方面,提供一种显示装置。所述显示装置包括:如上述任一实施例所述的显示面板,所述显示装置还包括驱动芯片,驱动芯片用于驱动所述显示面板进行显示。

26、上述显示装置具有与上述一些实施例中提供的阵列基板相同的结构和有益技术效果,在此不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!