半导体封装件的制作方法

本申请涉及半导体,更具体地,涉及一种半导体封装件。

背景技术:

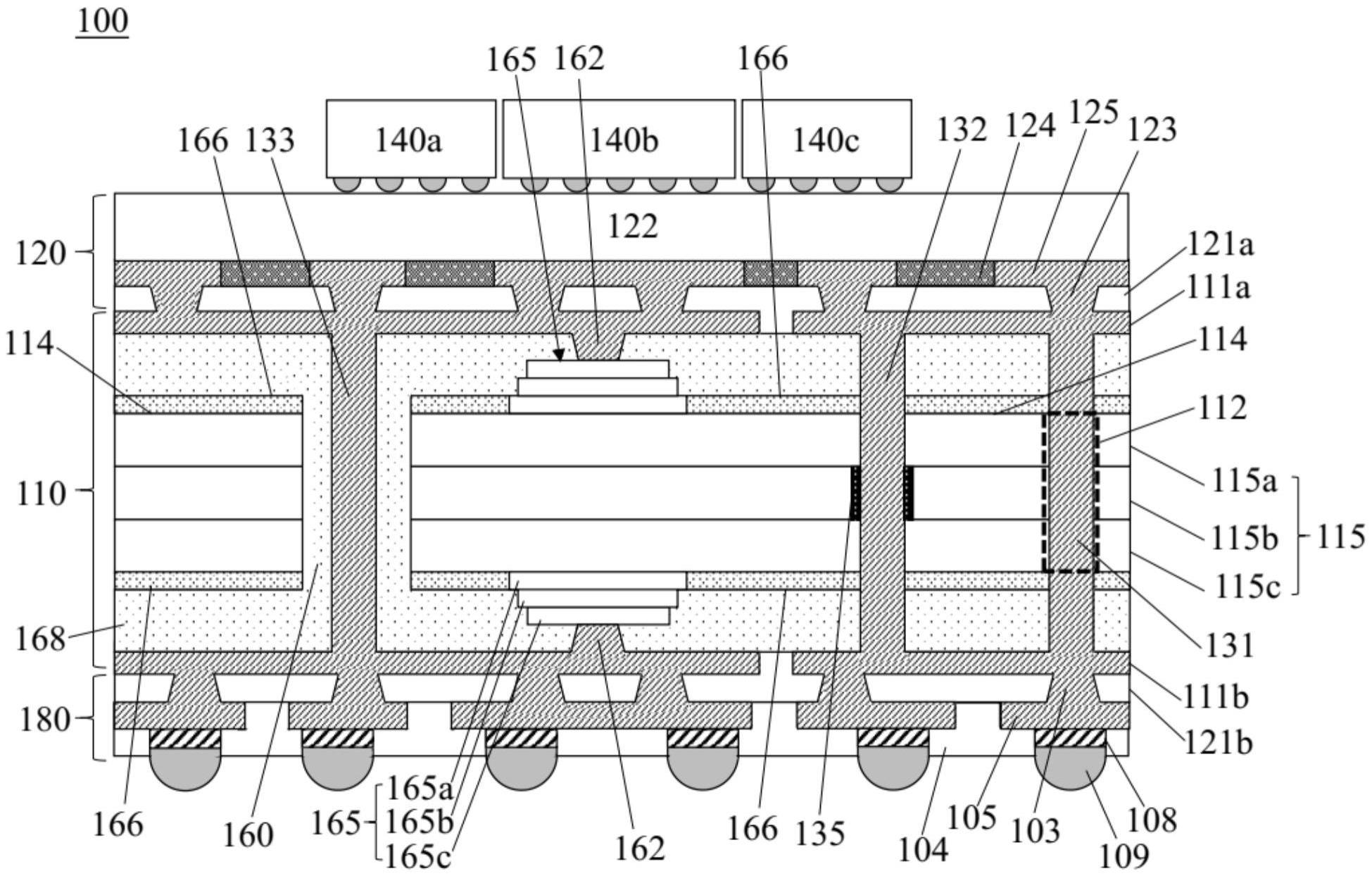

1、参考图1所示,现行的电力集成(power integration)封装结构,主要是将有源或无源的电子元件10内埋至基板核心(substrate core)20的空腔内,然后再利用树脂(resin)24填充电子元件10周围的空腔,并设置穿过基板核心20的pth(plating throughhole,电镀穿孔)21,以经由pth 21提供电子元件10上方及下方的电性传导,并在电子元件10上方设置重布线层(rdl,re-distribution layer)30及多个芯片40,以达成垂直传导的短路径并改善电性。

2、但电子元件10与基板核心20的材料之间存在cte(coefficient of thermalexpansion,热膨胀系数)差异,基板核心20、电子元件10、树脂24三者之间cte差异也使等效cte变化更加复杂,并且cte为材料本身受热膨胀的先天物理特性,不易借由制程手法降低其带来之影响。cte差异会造成翘曲问题(例如240μm翘曲)、或是脱层问题。此外,树脂24与电子元件10之间为一异质界面,异质界面的接着能力是造成脱层现象的要因。因此,树脂24在填充过程中,容易因有气泡产生而造成脱层现象,导致后续产品良率低下,成本高昂。

3、另外,因制程流程,造成电子元件10上方与下方树脂24的厚度不一致,这也会产生翘曲问题。在另一方面,在将电子元件10放置在空腔中时,随着电子元件10来料的基准标记(fiducial mark)外观形状异常,造成机台无法读取,会有抛料的状况发生,通常至少需额外准备10%的物料以应付抛料问题。在又一方面,需要使用热释放膜(thermal releasefilm)以支撑和固定电子元件10,避免电子元件10在置件制程中产生位移,并在树脂24填充固化之后移除热释放膜。然而在移除热释放膜解时,有连同电子元件10一同被剥落的风险,以及可能有残胶风险。故需要一种技术或结构可以改善上述问题。

技术实现思路

1、针对以上问题,本申请提出一种半导体封装件,以至少能够减少异质材料导致的cte不匹配的状况,从而改善翘曲与脱层问题。

2、本申请的技术方案是这样实现的:

3、根据本申请的一个方面,提供了一种半导体封装件,该半导体封装件包括:无源元件,包含功能区和连接区;线路层,设置于无源元件上且与无源元件电连接;其中,连接区提供连接至线路层的一导电路径,导电路径不经过功能区。

4、在一些实施例中,无源元件包含具有金属氧化物层、金属层和金属氧化物层的堆叠结构。

5、在一些实施例中,半导体封装件还包括第一导电柱,第一导电柱设置于连接区并用作导电路径,并且第一导电柱接触堆叠结构。

6、在一些实施例中,第一导电柱贯穿堆叠结构。

7、在一些实施例中,半导体封装件还包括第二导电柱,第二导电柱设置于功能区,并且接触堆叠结构。

8、在一些实施例中,第二导电柱接触一复合材料层,复合材料层将第二导电柱与堆叠结构中的金属层隔开。

9、在一些实施例中,半导体封装件还包括第三导电柱,第三导电柱不接触堆叠结构。

10、在一些实施例中,连接区连接线路层至无源元件的与线路层相对的另一侧。

11、在一些实施例中,任意两个功能区之间具有间隙。

12、在一些实施例中,无源元件还包括通孔,通孔电连接至堆叠结构,其中,通孔与堆叠结构之间设置有聚合物层、碳层和铜层的多层结构。

13、上述技术方案,通过将导电路径功能整合于无源元件的连接区,可以提供电性传导,增加垂直沟通的能力,还可以降低电容器本身的电阻。还可以减少异质材料间cte不匹配的状况,改善了翘曲问题和脱层问题。另外,由于不需要将无源元件埋入基板核心中,因此可避免抛料状况的发生,无需额外多准备物料以应付抛料问题;也不需使用热释放膜来支撑与固定无源元件,避免无源元件在置件制程中产生位移,也避免了由于解板导致的无源元件剥落与残胶问题。

技术特征:

1.一种半导体封装件,其特征在于,包括:

2.根据权利要求1所述的半导体封装件,其特征在于,所述无源元件包含具有金属氧化物层、金属层和金属氧化物层的堆叠结构。

3.根据权利要求2所述的半导体封装件,其特征在于,还包括第一导电柱,所述第一导电柱设置于所述连接区并用作所述导电路径,并且所述第一导电柱接触所述堆叠结构。

4.根据权利要求3所述的半导体封装件,其特征在于,所述第一导电柱贯穿所述堆叠结构。

5.根据权利要求2所述的半导体封装件,其特征在于,还包括第二导电柱,所述第二导电柱设置于所述功能区,并且接触所述堆叠结构。

6.根据权利要求5所述的半导体封装件,其特征在于,所述第二导电柱接触一复合材料层,所述复合材料层将所述第二导电柱与所述堆叠结构中的所述金属层隔开。

7.根据权利要求5所述的半导体封装件,其特征在于,还包括第三导电柱,所述第三导电柱不接触所述堆叠结构。

8.根据权利要求1所述的半导体封装件,其特征在于,所述连接区连接所述线路层至所述无源元件的与所述线路层相对的另一侧。

9.根据权利要求1所述的半导体封装件,其特征在于,任意两个所述功能区之间具有间隙。

10.根据权利要求2所述的半导体封装件,其特征在于,所述无源元件还包括通孔,所述通孔电连接至所述堆叠结构,其中,所述通孔与所述堆叠结构之间设置有聚合物层、碳层和铜层的多层结构。

技术总结

本申请公开了一种半导体封装件,包括:无源元件,包含功能区和连接区;线路层,设置于无源元件上且与无源元件电连接;其中,连接区提供连接至线路层的一导电路径,导电路径不经过功能区。上述技术方案,通过将导电路径功能整合于无源元件的连接区,至少能够减少异质材料导致的CTE不匹配的状况,从而改善翘曲与脱层问题。

技术研发人员:庄弘毅,唐心陆,许武州

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:20230202

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!