集成电路的制作方法

本揭示案的是关于一集成电路,特别是包含静电放电路径的集成电路。

背景技术:

1、esd事件产生极高的电压且导致持续时间短的高电流脉冲,该些脉冲会损害集成电路装置。举例而言,当esd电流在集成电路的端子之间放电时,集成电路的晶体管中的栅极氧化物层被击穿。为了有效的esd保护,esd保护电路经常需要占用大面积的大量nmos/pmos。

技术实现思路

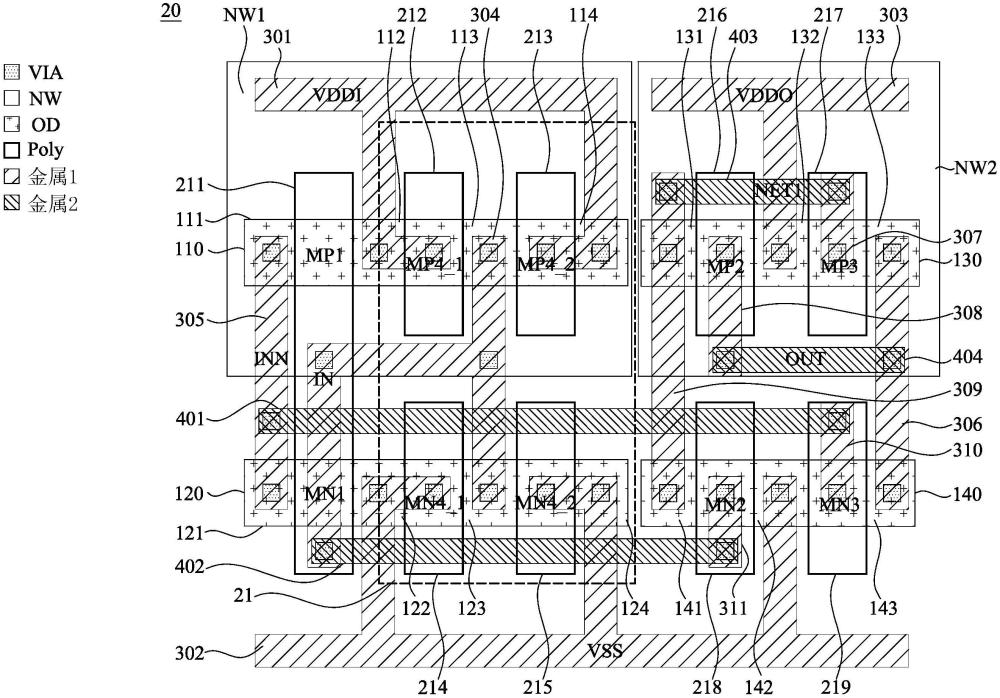

1、根据本揭示案的一实施例,提供一种集成电路且集成电路包括:第一导电型的第一主动区域,第一主动区域耦接至第一电压端子且对应于包括在位准移位器电路的反相器中的第一晶体管的第一端子及第二晶体管的第一端子,其中第一晶体管用以使静电电荷放电至第一电压端子;及对应于第三晶体管的不同于第一导电型的第二导电型的第二主动区域及第三主动区域,其中第二主动区域耦接至第二电压端子,且第三主动区域耦接至位准移位器电路的不同于第二电压端子的第一端子。第三晶体管用以传输用于集成电路的来自第二电压端子的第一供应电压。

2、根据本揭示案的一实施例,提供一种集成电路且集成电路包括:第一导电型的第一主动区域,第一主动区域耦接至第一电压端子且对应于包括在位准移位器电路的反相器中的第一晶体管的第一端子及第二晶体管的第一端子,第一晶体管及第二晶体管在布局图中在第一方向上彼此分开,其中第一晶体管用以使静电电荷放电至第一电压端子;及对应于第三晶体管的不同于第一导电型的第二导电型的第二主动区域及第三主动区域,第三晶体管包括在静电放电保护电路中,其中第二主动区域耦接至第二电压端子,且第三主动区域耦接至位准移位器电路的不同于第二电压端子的端子,其中第三晶体管用以传输用于集成电路的来自第二电压端子的第一供应电压。

3、根据本揭示案的一实施例,提供一种集成电路且集成电路包括:第一导电型的第一主动区域,第一主动区域耦接至第一电压端子且对应于包括在位准移位器电路的反相器中的第一晶体管的第一端子及第二晶体管的第一端子,第一晶体管及第二晶体管在布局图中在第一方向上彼此分开,其中第一晶体管用以使静电电荷放电至第一电压端子;及对应于第三晶体管的不同于第一导电型的第二导电型的第二主动区域及第三主动区域,第三晶体管包括在静电放电保护电路中,其中第二主动区域耦接至第二电压端子,且第三主动区域耦接至位准移位器电路的不同于第二电压端子的一端子,其中第三晶体管用以传输用于集成电路的来自第二电压端子的第一供应电压,以及在布局图中,第三晶体管在第一方向上配置在第一晶体管与第二晶体管之间。

技术特征:

1.一种集成电路,其特征在于,包含:

2.如权利要求1所述的集成电路,其特征在于,该集成电路进一步包含:

3.如权利要求1所述的集成电路,其特征在于,该集成电路进一步包含:

4.如权利要求1所述的集成电路,其特征在于,该集成电路进一步包含:

5.如权利要求1所述的集成电路,其特征在于,该集成电路进一步包含:

6.如权利要求1所述的集成电路,其特征在于,该集成电路进一步包含:

7.一种集成电路,其特征在于,包含:

8.如权利要求7所述的集成电路,其特征在于,其中该静电放电保护电路进一步包含:

9.如权利要求7所述的集成电路,其特征在于,其中该位准移位器电路进一步包括:

10.一种集成电路,其特征在于,包含:

技术总结

提供一种集成电路且该集成电路包括:一第一导电型的一第一主动区域,该第一主动区域耦接至一第一电压端子且对应于包括在一位准移位器电路的一反相器中的一第一晶体管的一第一端子及一第二晶体管的一第一端子,其中该第一晶体管用以使静电电荷放电至该第一电压端子;及对应于一第三晶体管的不同于该第一导电型的一第二导电型的第二主动区域及第三主动区域,其中该第二主动区域耦接至一第二电压端子,且该第三主动区域耦接至该位准移位器电路的不同于该第二电压端子的一第一端子。该第三晶体管用以传输用于该集成电路的来自该第二电压端子的一第一供应电压。

技术研发人员:潘磊,马亚琪,杨惠之,马琴玲

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230629

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!