一种增加JFET区源极接触的屏蔽型SiCMOSFET结构的制作方法

本发明涉及sic mosfet的抗雪崩击穿能力和短路能力的片上结构改进,具体涉及一种增加jfet区源极接触的屏蔽型sic mosfet结构。

背景技术:

1、sic mosfet器件具有高频低损耗的显著优势,在电动汽车、光伏逆变器和充电桩等领域有十分广泛的应用。然而,一方面sic mosfet极快的开关速度使得器件在关断过程中极易产生漏源电压过冲的问题,尤其在800v的电驱系统等应用中易导致sic mosfet器件出现短时的雪崩击穿,在sic mos栅氧附近形成极大的电热应力,长期使用过程中易出现器件性能退化甚至损坏的问题;另一方面sic mosfet在电驱系统发生负载短路时会出现短路故障,瞬时的高压大电流极易导致器件短路失效。目前针对同时优化sic mosfet器件雪崩能力和短路能力的方法极少,大部分仍是基于单种鲁棒性进行优化提升。例如,现有技术通常采用优化p阱掺杂形貌和优化终端电场分布等调整元胞结构参数的方法,或者在器件关断过程中优化驱动防止器件出现漏源电压过冲等方法来提升sic mosfet雪崩能力或者抑制器件出现漏源电压过冲,采用缩短jfet区或者在驱动电路中集成短路保护功能等方法来改善sic mosfet在实际电源系统中的短路故障穿越能力。这些方法通常只能改善器件的一种鲁棒性,而且会给器件的其他性能引入负面影响。例如,缩短jfet宽度可能造成sicmosfet器件比导通电阻增大,导致器件导通损耗增大。如图1所示为提升器件雪崩能力而采用的倒掺杂p阱sic mosfet元胞结构,图2所示为提升器件短路能力而采用的窄jfet区sicmosfet元胞结构。

2、此外,在材料和本身性能应用到极限后,在考虑到器件的性能方面,传统的vdmosfet器件,其体二极管主要由pn结组成,其开启电压相对较大。传统vdmosfet的crss也较大,这是由于栅极(g极)与漏极(d极)的正对面积较大。crss较大,直接导致器件的ciss、coss等参数较大,从而增加器件的开关损耗,如何利用新的性能改进并进一步提升在发生漏源电压过冲时的雪崩能力,而不是单纯的结构叠加,故本专利提供了一种针对sicmosfet器件全方位的性能解决方案。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种增加jfet区源极接触的屏蔽型sic mosfet结构,增加的屏蔽结构和源极接触,一方面在jfet区底部实现大幅缩短jfet区的宽度,有利于在jfet区底部通过耗尽效应减小器件短路时的电流路径宽度,大幅降低器件的短路饱和电流,进而提升sic mosfet的短路能力;另一方面,通过反偏肖特基结与屏蔽结构共同作用,减弱甚至消除在发生漏源电压过冲时在jfet区下形成的极强电场,进一步提升器件的雪崩能力,源极接触设置还将vdmosfet的jfet区顶端多晶硅栅分裂,降低g极与d极的正对面积,大幅降低碳化硅vdmosfet的crss,降低sic mosfet器件的体二极管压降,并使原有结构的体二极管变为现有肖特基二极管的浪涌注入结构,增加体二极管的抗浪涌能力;同时,新结构降低了栅漏两极的正对面积,可以降低器件的开关损耗。

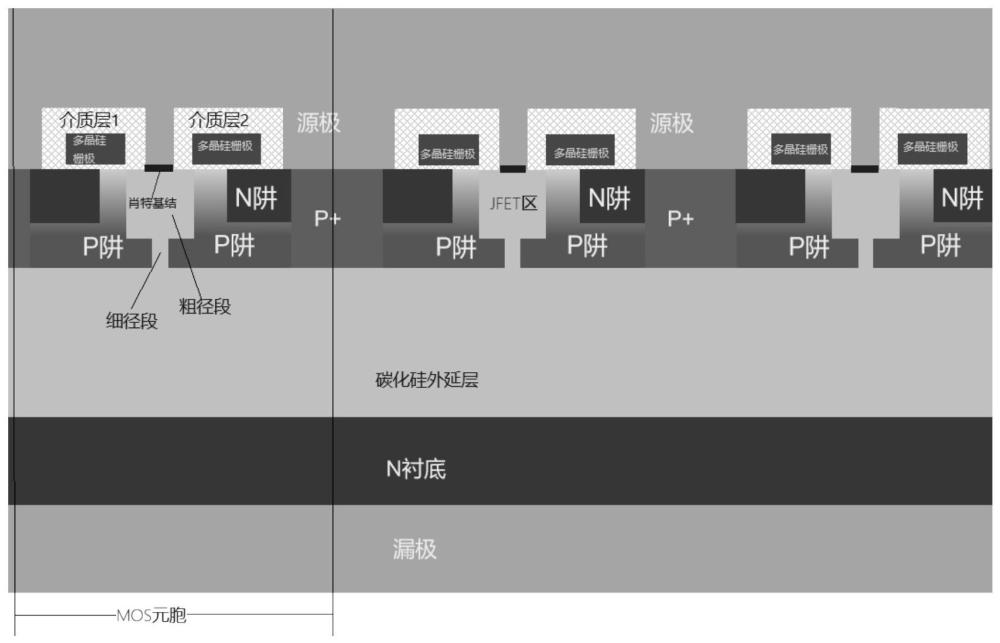

2、为解决以上技术问题,本发明提供一种增加jfet区源极接触的屏蔽型sic mosfet结构,包括多个并联的mos元胞,所述mos元胞中具有jfet区,所述jfet区的横截面呈柱型轮廓,所述柱型轮廓至少具有一粗径段和一细径段以形成屏蔽结构,所述粗径段与所述mos元胞的栅氧层接触,所述jfet区上方具有gate,所述gate包括栅氧层、淀积在栅氧层上的多晶硅栅极及覆盖多晶硅栅极的介质层,所述多晶硅栅极位于所述jfet区上的位置被打断以形成两段的所述多晶硅栅极,所述源极通过两段的所述多晶硅栅极与所述jfet区直接接触以形成肖特基结。

3、在一些实施例中优选地方案,所述粗径段和所述细径段自上而下布置并依次连通。

4、在一些实施例中优选地方案,所述粗径段与所述细径段的直径呈等差数值,和/或,所述粗径段与所述细径段的直径呈非等差数值。

5、在一些实施例中优选地方案,所述jfet区的粗径段和细径段对应的离子浓度相同并且为高浓度。

6、在一些实施例中优选地方案,所述栅氧层也被所述肖特基结打断形成分别位于两段的所述多晶硅栅极下方,所述介质层也被打断并分别形成分别包裹两段的所述多晶硅栅极的介质层1和介质层2。

7、在一些实施例中优选地方案,所述屏蔽型sic mosfet结构还包括碳化硅外延层,所述碳化硅外延层上通过离子注入等距分布呈井状并为p型半导体的p阱,相邻所述p阱之间形成有所述jfet区,所述p阱中部通过极高浓度的相同离子注入形成为p型半导体的p+,所述p+的两侧通过极高浓度的离子注入形成为n型半导体的n阱,所述n阱与所述p+接触,所述n阱不靠近所述p阱侧面,所述jfet区上方形成有所述栅氧层,所述栅氧层上淀积有所述多晶硅栅极,所述多晶硅栅极上淀积有介质层,所述栅氧层和所述多晶硅栅极至少延伸位于所述n阱上方,所述碳化硅外延层上淀积有覆盖所述介质层的源极,所述碳化硅外延层下侧具有n衬底,所述n衬底下方具有漏极,为了便于理解,将由多晶硅栅极纵向对应的单位范围内相同的结构定义为所述mos元胞;

8、其中,所述p阱与所述jfet区外侧对应的结构呈榫卯适配的形貌。

9、在一些实施例中优选地方案,所述介质层为sio2。

10、在一些实施例中优选地方案,所述p阱上的注入的离子为倒注入,即所述p阱的底部离子浓度高于顶部浓度。

11、在一些实施例中优选地方案,所述p阱注入的离子为al离子或b离子,所述p+注入为极高浓度的al离子或b离子,所述n阱注入的离子为极高浓度的p离子或n离子。

12、与现有技术相比,本发明的优点如下:

13、1、本发明引入的屏蔽结构为直接在sic mosfet元胞中的jfet区中直接改进形成,结构简单,工艺易于实现。

14、2、本发明引入的增加的屏蔽结构和源极接触,一方面在jfet区底部实现大幅缩短jfet区的宽度,有利于在jfet区底部通过耗尽效应减小器件短路时的电流路径宽度,大幅降低器件的短路饱和电流,进而提升sic mosfet的短路能力;另一方面,通过反偏肖特基结与屏蔽结构共同作用,减弱甚至消除在发生漏源电压过冲时在jfet区下形成的极强电场,进一步提升器件的雪崩能力;引入肖特基接触端,在体二极管接正向电压时,肖特基接触形成的肖特基结会率先开启,体二极管导通,在电压持续增加时,pn结二极管开启,电阻进一步降低。原有pn结部分可以作为现有体二极管的浪涌注入部分,降低开关的损耗。此种结构相当于将原有结构的体二极管从pn结二极管变成了具有抗浪涌电流功能的肖特基二极管,大幅度提升了器件的体二极管特性,将jfet区的多晶硅栅分开,减少了栅极覆盖面积,直接降低了器件的crss,进一步降低了器件的ciss、coss、qg、eon、eoff等一系列电学参数值,使器件性能更加优异,从而从各个方面保护器件,全方位提升器件的实用性。

15、3、本发明的屏蔽结构的jfet区可以进一步提高栅氧下方粗径段的jfet区的掺杂浓度,进而降低sic mosfet积累层电阻和jfet电阻,实现更低比导通电阻的sic mosfet。

16、4、本发明的结构突破了常规sic mosfet短路能力和导通电阻难以协同优化的难题,可以大幅提升器件的综合性能。

- 还没有人留言评论。精彩留言会获得点赞!