一种具有变深度JTE结构的超宽禁带半导体二极管

本发明属于功率半导体器件,具体涉及一种具有变深度jte结构的超宽禁带半导体二极管及其制备方法。

背景技术:

1、在能源问题和环保问题越来越被人们关注的今天,社会对电力电子系统的效率有了更高的需求,对功率半导体器件的性能也提出了更高的要求。时至今日,硅基功率器件已经在诸多领域内有了广泛的应用。然而随着硅功率器件发展接近成熟以及硅材料本身的材料特性限制,其器件性能已无法满足日益增长的大功率应用需求。因此宽禁带材料(如碳化硅,氮化镓等材料)因其高热导率、高临界场强、高饱和漂移速率等优点受到越来越多的重视和投资。目前宽禁带材料功率器件已经在光伏、充电器和新能源汽车等领域投入应用,并且占有了相当一部分市场。而随着宽禁带半导体材料的应用逐渐成熟,以及人们对更高功率器件的迫切需求,被视为超宽禁带半导体材料的氧化镓(ga2o3)、金刚石等成为了新的焦点。

2、在材料特性方面,氧化镓、金刚石作为超宽带隙半导体材料,具有相近的超宽禁带和10倍于硅的临界击穿电场,二者的饱和漂移速度也远在硅材料之上。具有超宽禁带的两种材料在抗辐照和热稳定性方面上也会有更优良的表现,高饱和漂移速度能使器件工作于更高功率领域。得益于这些优越的特性,ga2o3器件已经在电力电子器件、紫外光电探测器、太阳能电池等诸多领域表现出了巨大的应用潜力,而金刚石器件在微波通信、雷达系统、航空航天、电力系统、生物检测、量子计算等领域拥有广阔的应用前景,但二者目前离大规模市场化应用都还有一段距离。

3、作为超宽禁带半导体,其器件实现的难点在于如何形成有效的掺杂浓度。晶相β-ga2o3具有较好的热稳定性,因此它可以像其他材料一样通过离子注入之后热处理的方式实现较好的n型掺杂,但β-ga2o3中还难以实现稳定可控的高质量p型掺杂。而对于金刚石来说,p型掺杂可以通过硼元素实现,但想要实现良好的n型掺杂仍然是困扰业界的难题。同时,两种材料本身的临界击穿电场非常高,所以根据高斯定理,在器件击穿时上方介质层内部的电场会升高到一个难以接受的数值。受限于这两点,以这两种材料为基础的器件很难充分发挥两种材料本身优越的特性。

技术实现思路

1、本发明所要解决的技术问题是针对现有技术存在的问题,提供一种具有变深度结终端扩展(jte)结构的超宽禁带半导体二极管及其制备方法,以改善超宽禁带半导体器件的耐压能力,提高器件的散热性能,保护介质层的可靠性。

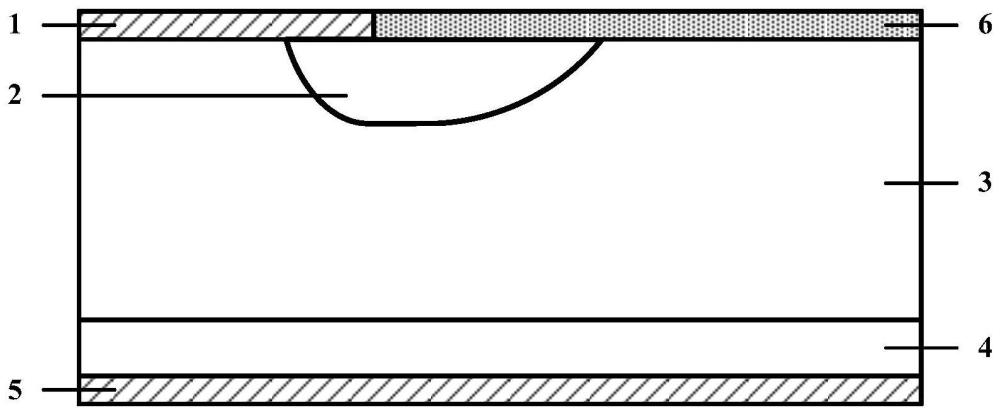

2、为解决上述技术问题,本发明实施例提供一种具有变深度jte结构的超宽禁带半导体二极管,其元胞结构包括从下至上依次层叠设置的阴极金属层5、衬底层4和外延层3,所述外延层3的顶层中具有jte区2,部分jte区2和部分外延层3上设置阳极金属层1,另一部分jte区2及另一部分外延层3上设置介质层6,所述介质层6和所述阳极金属层1的侧面相互接触;

3、阳极金属层1与外延层3形成肖特基接触,阴极金属层5与衬底层4形成欧姆接触;

4、所述衬底层4、外延层3均为第一超宽禁带半导体材料;所述衬底层4的浓度高于外延层3的浓度;所述jte区2为第二超宽禁带半导体材料,第一超宽禁带半导体材料不同于第二超宽禁带半导体材料;jte区2的中间结深不变,两侧的结深为逐渐减小的弧面直至外延层3表面,形成变深度jte结构;所述jte区2靠近阳极金属层一侧的弧面在平行于外延层3表面的方向上的长度小于远离阳极金属层一侧的弧面的长度变深度jte结构;所述jte区2由淀积工艺形成,与外延层3形成异质结来改善电场分布。在上述技术方案的基础上,本发明还可以做如下改进。

5、进一步的,所述第一超宽禁带半导体材料为n型氧化镓、p型金刚石中的一种;所述第二超宽禁带半导体材料为n型氧化镓、p型金刚石中的一种,且与第一超宽禁带半导体材料不同。

6、进一步的,所述n型氧化镓的掺杂元素包括si、sn中的一种或多种;

7、和/或,所述jte区2的掺杂元素为b。

8、进一步的,所述阳极金属层1的材料包括ni、au、pt、al中的一种或多种,厚度为100~500nm;

9、和/或,所述阴极金属层5的材料包括ti、au、cr中的一种或多种,厚度为80~300nm。

10、进一步的,所述介质层6的材料包括si3n4、al2o3、hfo2、zro2中的一种或多种,厚度为150~300nm。

11、进一步的,所述jte区2的底面与弧面之间在分界线处为平滑过渡。

12、采用上述进一步方案的有益效果为:上述结构能够有效消除因几何特征所引发的电力线聚集效应。

13、进一步的,根据设计需要,通过调整工艺也可以使jte区2的两侧呈斜面形貌。

14、进一步的,所述jte区2中,可以根据需要不保留结深不变的区域,旨在节省终端面积。

15、进一步的,所述jte区2通过多次淀积工艺形成。

16、采用上述进一步方案的有益效果为:控制浓度分布来达到更好的电场分布。

17、为解决上述技术问题,本发明实施例提供上述一种具有变深度jte结构的超宽禁带半导体二极管的制备方法,包括以下步骤:

18、s1、在衬底层4上外延形成外延层3;

19、s2、在外延层3的表面制备掩膜层,通过光刻和刻蚀技术在掩模层上形成具有弧面的沟槽形貌;

20、s3、通过干法刻蚀将掩膜层上的弧面沟槽形貌转移到外延层3上;

21、s4、在外延层3表面和沟槽内部填充第二超宽禁带半导体材料,之后对表面进行平坦化处理形成jte区2;

22、s5、在外延层3和jte区2表面制备介质层6,刻蚀形成肖特基接触窗口;

23、s6、在器件表面制备阳极金属层1,所述阳极金属层1位于所述外延层3上,且与jte区2部分交叠;

24、s7、在所述衬底层4的底部制备阴极金属层5。

25、进一步的,步骤s2还包括以下步骤:

26、s21、在外延层3表面淀积低刻蚀速率材料7,并在低刻蚀速率材料7表面旋涂光刻胶,曝光显影后露出刻蚀窗口;

27、s22、采用干法刻蚀工艺,在低刻蚀速率材料7上刻蚀出台阶;

28、s23、在低刻蚀速率材料7表面上淀积第一高刻蚀速率材料8,之后通过光刻技术在第一高刻蚀速率材料8的表面上露出刻蚀窗口;

29、s24、对器件进行湿法刻蚀,在低刻蚀速率材料7上形成弧面,之后去除光刻胶。

30、进一步的,所述低刻蚀速率材料7的厚度应大于第一高刻蚀速率材料8的厚度,所述第一高刻蚀速率材料8的厚度不大于0.5μm,低刻蚀速率材料7的厚度不小于1.0μm。

31、采用上述进一步方案的有益效果为:通过湿法刻蚀对上层材料的快速刻蚀,让湿法试剂能够延伸到光刻胶掩膜下方被覆盖的位置,从而在掩膜下方对低刻蚀材料刻蚀形成更长且角度可控的弧面沟槽。

32、进一步的,步骤s24还包括:去除第一高刻蚀速率材料8。

33、进一步的,步骤s2还包括以下步骤:

34、s21、在外延层3的表面淀积低刻蚀速率材料7,之后在低刻蚀速率材料7表面旋涂光刻胶,曝光显影后露出离子注入窗口;

35、s22、对低刻蚀速率材料7表面进行离子注入,退火形成具有高刻蚀速率的改性层71;

36、s23、通过湿法刻蚀工艺,刻蚀掉改性层71,去除光刻胶,在低刻蚀速率材料7上形成台阶;

37、s24、在低刻蚀速率材料7的表面上淀积第一高刻蚀速率材料8,之后通过光刻技术在第一高刻蚀速率材料8的表面上露出刻蚀窗口;

38、s25、对器件进行湿法刻蚀,在低刻蚀速率材料7上形成弧面,之后去除光刻胶和第一高刻蚀速率材料8。

39、进一步的,步骤s2还包括以下步骤:

40、s21、在外延层3的表面淀积低刻蚀速率材料7;

41、s22、在器件表面上淀积第二高刻蚀速率材料81,之后刻蚀掉部分区域的第二高刻蚀速率材料81,在低刻蚀速率材料7上形成台阶;

42、s23、在低刻蚀速率材料7的表面上淀积第一高刻蚀速率材料8,之后通过光刻技术在第一高刻蚀速率材料8的表面上露出刻蚀窗口;

43、s24、对器件进行湿法刻蚀,在低刻蚀速率材料7上形成弧面,之后去除光刻胶、第一高刻蚀速率材料8和第二高刻蚀速率材料81。

44、进一步的,其形成多区变深度jte结构的方法还应用于mosfet、igbt或gto中。

45、进一步的,所述低刻蚀速率材料7的材料包括sio2、si3n4、al2o3中的一种或多种,厚度由其在所用干法刻蚀中与第一超宽禁带半导体材料的选择比和设计的jte区2的厚度决定。

46、本发明的有益效果是:

47、一、目前通过各种方法外延生长n型氧化镓和p型金刚石的技术已经趋于成熟,其形成的材料具有易于杂质控制、生长速率高和均匀性好等特点。此外,两种材料的临界击穿电场相近,这保证了器件不会在异质结附近过早地发生击穿。综上所述,淀积形成的p型金刚石-n型氧化镓异质结能够有效地改进电场分布,保护介质层,提高器件的耐压能力。

48、二、本发明在器件边缘形成的变深度jte结构能够在占用较小面积的情况下有效缓解甚至消除边缘处电场集中的问题,进一步提高超宽禁带半导体器件的击穿电压。引入的变深度jte结构工艺窗口较常规jte结构更能增加设计裕度,更容易满足其耐压时完全耗尽的要求。同时,jte区域底面处的平滑过渡和两侧的弧面能够有效缓解电场集中现象,进一步改善器件耐压能力。该结构不仅能保护器件上方的介质层可靠性,还能够有效保护肖特基接触。

49、三、本发明提出的利用两层具有不同湿法刻蚀速率的材料实现刻蚀掩膜的方法相比于只对介质层进行湿法刻蚀的方法来说,能够形成较长的jte结构,能够更好改善器件的特性。在淀积之后针对第二超宽禁带半导体材料表面进行的平坦化处理能有效降低表面因各种工艺引入的界面态、表面电荷等会影响终端结构耐压能力的不利因素。同时,变深度jte结构的沟槽是通过一次刻蚀产生的,其一致性和表面粗糙度较好,且易于通过其他工艺处理改善其界面特性。同时,本发明提供的方法不仅可以用于氧化镓或金刚石二极管的结终端制备,还适用于以金刚石或氧化镓材料为基础的各种功率器件,如mos、igbt、gto等。

- 还没有人留言评论。精彩留言会获得点赞!