一种沟槽MOSFET器件及沟槽MOSFET器件阵列的制作方法

本申请涉及半导体,特别涉及一种沟槽mosfet器件及沟槽mosfet器件阵列。

背景技术:

1、目前,随着半导体技术的迅速发展,沟槽金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)器件已经成为人们的研究热点。但是现有的沟槽mosfet器件中,仍然存在利用jfet区保护栅极槽角和其较大导通电阻之间的矛盾关系,影响器件性能进一步提升。因此,提供一种全新的沟槽mosfet器件成为目前急需解决的技术问题。

技术实现思路

1、有鉴于此,本申请的目的在于提供一种沟槽mosfet器件及沟槽mosfet器件阵列,降低了器件的导通电阻,增大器件导通电流,可以提升沟槽mosfet器件的导通特性,提升沟槽mosfet的器件性能。其具体方案如下:

2、第一方面,本申请提供了一种沟槽mosfet器件,包括:

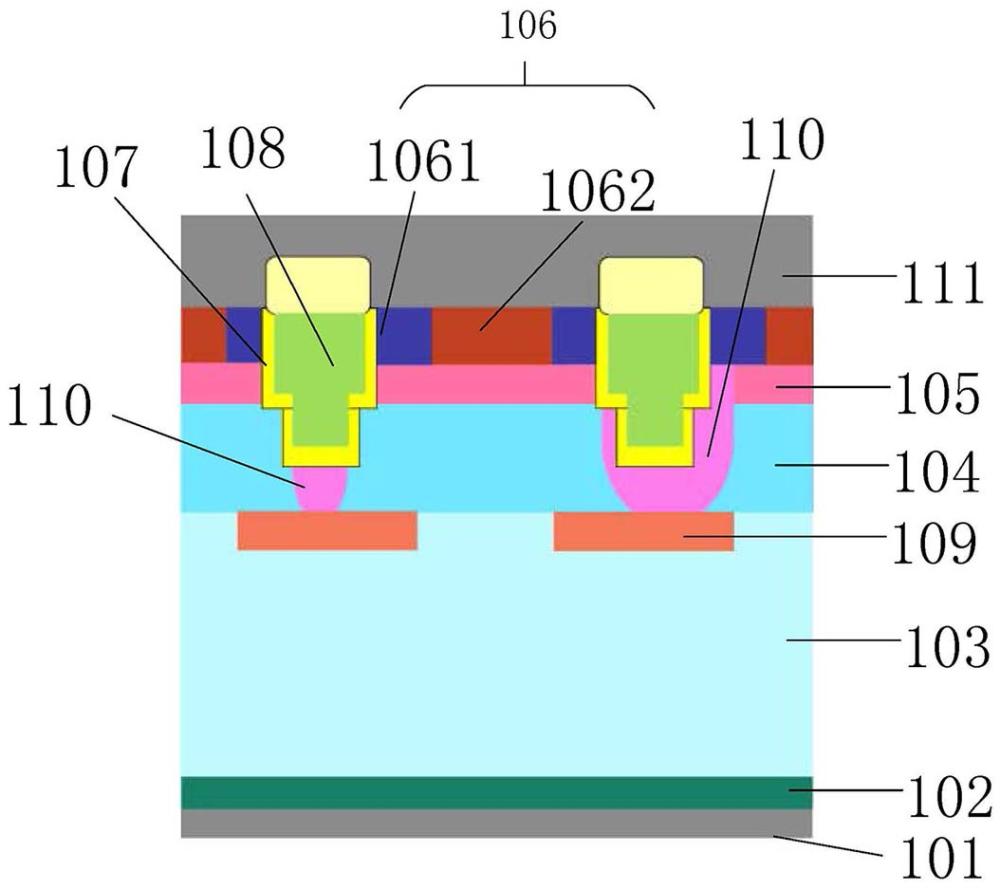

3、沿第一方向依次堆叠的漏极金属层、衬底层、外延层、电流扩展层、阱层、源区和源极金属层;所述衬底层、所述外延层和所述电流扩展层具有第一掺杂类型,所述阱层具有与所述第一掺杂类型相反的第二掺杂类型;

4、与所述电流扩展层、所述阱层、所述源区和所述源极金属层同层,且设置在沟槽内的栅极结构;所述源区包括具有所述第一掺杂类型的第一掺杂区,以及具有所述第二掺杂类型的第二掺杂区,所述第一掺杂区和所述栅极结构相邻;

5、位于所述外延层内的掩埋区,所述掩埋区具有所述第二掺杂类型;

6、与所述电流扩展层同层设置且具有所述第二掺杂类型的第三掺杂区,所述第三掺杂区与所述掩埋区相连;在相邻的沟槽mosfet器件中,相邻的所述第三掺杂区之间的距离大于相邻的所述掩埋区之间的距离。

7、可选地,所述第三掺杂区与所述沟槽的侧壁之间的距离小于预设距离,且所述第三掺杂区将所述掩埋区和所述阱层相连。

8、可选地,所述第三掺杂区至少与所述沟槽的一侧侧壁相接触。

9、可选地,所述第三掺杂区和所述第二掺杂区通过离子注入同时形成。

10、可选地,在第二方向上所述掩埋区的长度大于所述沟槽的长度,所述第二方向为与所述第一方向垂直的方向。

11、可选地,所述沟槽mosfet器件还包括具有所述第一掺杂类型的第四掺杂区,所述第四掺杂区位于所述掩埋区和所述电流扩展层内,所述第四掺杂区与所述沟槽的一侧侧壁和底部相接触。

12、可选地,所述掩埋区包括多个掩埋层,多个所述掩埋层位于所述外延层的不同深度位置处;

13、或,所述掩埋区的厚度大于预设厚度。

14、第二方面,本申请实施例还提供了一种沟槽mosfet器件阵列,包括多个所述的沟槽mosfet器件,多个所述沟槽mosfet器件在第一方向和第二方向上阵列排布。

15、可选的,多个所述沟槽mosfet器件包括第一沟槽mosfet器件,所述第一沟槽mosfet器件中的第三掺杂区与所述沟槽的侧壁之间的距离小于预设距离,且所述第三掺杂区将所述掩埋区和所述阱层相连。

16、可选的,多个所述沟槽mosfet器件还包括第二沟槽mosfet器件,所述第二沟槽mosfet器件中的第三掺杂区位于所述沟槽的底部和所述掩埋区之间,所述第一沟槽mosfet器件和所述第二沟槽mosfet器件在所述第一方向上交替排列。

17、本申请实施例提供了一种沟槽mosfet器件及沟槽mosfet器件阵列,沟槽mosfet器件包括沿第一方向依次堆叠的漏极金属层、衬底层、外延层、电流扩展层、阱层、源区和源极金属层,以及栅极结构、掩埋层和第三掺杂区。其中,衬底层、外延层和电流扩展层具有第一掺杂类型,阱层具有与第一掺杂类型相反的第二掺杂类型,栅极结构与电流扩展层、阱层、源区和源极金属层同层,且设置在沟槽内的栅极结构,源区包括具有第一掺杂类型的第一掺杂区,以及具有第二掺杂类型的第二掺杂区,第一掺杂区和栅极结构相邻。掩埋区位于外延层内部,且具有第二掺杂类型,第三掺杂区与电流扩展层同层设置且具有第二掺杂类型,第三掺杂区与掩埋区相连。

18、由此可见,通过分别形成掩埋区和第三掺杂区,可以精确控制掩埋区和第三掺杂区的宽度,进而,对于相邻的沟槽mosfet器件,可以精确控制掩埋区之间的距离,以及第三掺杂区之间的距离,由于相邻掩埋区之间以及相邻第三掺杂区之间会形成jfet区,通过设置相邻的第三掺杂区之间的距离大于相邻的掩埋区之间的距离,可以使得相邻的第三掺杂区之间的距离较大,进而使得相邻的第三掺杂区之间形成电阻更小的jfet区,降低了器件的导通电阻,且增加了电流扩展空间,增大器件导通电流,可以提升沟槽mosfet器件的导通特性,同时掩埋区可以很好的保护栅极槽角,提升沟槽mosfet的整体器件性能。

技术特征:

1.一种沟槽mosfet器件,其特征在于,包括:

2.根据权利要求1所述的沟槽mosfet器件,其特征在于,所述第三掺杂区与所述沟槽的侧壁之间的距离小于预设距离,且所述第三掺杂区将所述掩埋区和所述阱层相连。

3.根据权利要求2所述的沟槽mosfet器件,其特征在于,所述第三掺杂区至少与所述沟槽的一侧侧壁相接触。

4.根据权利要求2所述的沟槽mosfet器件,其特征在于,所述第三掺杂区和所述第二掺杂区通过离子注入同时形成。

5.根据权利要求1所述的沟槽mosfet器件,其特征在于,在第二方向上所述掩埋区的长度大于所述沟槽的长度,所述第二方向为与所述第一方向垂直的方向。

6.根据权利要求1所述的沟槽mosfet器件,其特征在于,所述沟槽mosfet器件还包括具有所述第一掺杂类型的第四掺杂区,所述第四掺杂区位于所述掩埋区和所述电流扩展层内,所述第四掺杂区与所述沟槽的一侧侧壁和底部相接触。

7.根据权利要求1所述的沟槽mosfet器件,其特征在于,所述掩埋区包括多个掩埋层,多个所述掩埋层位于所述外延层的不同深度位置处;

8.一种沟槽mosfet器件阵列,其特征在于,包括多个根据权利要求1-7任意一项所述的沟槽mosfet器件,多个所述沟槽mosfet器件在第一方向和第二方向上阵列排布。

9.根据权利要求8所述的沟槽mosfet器件阵列,其特征在于,多个所述沟槽mosfet器件包括第一沟槽mosfet器件,所述第一沟槽mosfet器件中的第三掺杂区与所述沟槽的侧壁之间的距离小于预设距离,且所述第三掺杂区将所述掩埋区和所述阱层相连。

10.根据权利要求9所述的沟槽mosfet器件阵列,其特征在于,多个所述沟槽mosfet器件还包括第二沟槽mosfet器件,所述第二沟槽mosfet器件中的第三掺杂区位于所述沟槽的底部和所述掩埋区之间,所述第一沟槽mosfet器件和所述第二沟槽mosfet器件在所述第一方向上交替排列。

技术总结

本申请提供一种沟槽MOSFET器件及沟槽MOSFET器件阵列,通过分别形成掩埋区和第三掺杂区,可以精确控制掩埋区和第三掺杂区的宽度,进而,对于相邻的沟槽MOSFET器件,可以精确控制掩埋区之间的距离,以及第三掺杂区之间的距离,由于相邻掩埋区之间以及相邻第三掺杂区之间会形成JFET区,通过设置相邻的第三掺杂区之间的距离大于相邻的掩埋区之间的距离,进而使得相邻的第三掺杂区之间形成电阻更小的JFET区,降低了器件的导通电阻,且增加了电流扩展空间,增大器件导通电流,可以提升沟槽MOSFET器件的导通特性,同时掩埋区可以很好的保护栅极槽角,提升沟槽MOSFET的整体器件性能。

技术研发人员:袁俊,成志杰,陈伟,郭飞,王宽,吴阳阳

受保护的技术使用者:湖北九峰山实验室

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!