晶体管测试方法及存储器监控方法与流程

本申请涉及集成电路,特别是涉及一种晶体管测试方法及存储器监控方法。

背景技术:

1、在芯片生产制造过程中,通常在芯片外围设计尺寸相同或相近的测试图形(testkey),采用线上晶圆接受测试(wafer acceptance test,简称wat)获取电性参数以监测芯片上晶体管的电学特性是否满足要求。

2、然而,目前线上晶体管电性量测无法全面地对待测晶体管是否存在缺陷进行检测,容易导致含缺陷晶体管的芯片流出,影响产品良率。

技术实现思路

1、基于此,本申请提供了一种晶体管测试方法及存储器监控方法,能够全面地对待测晶体管是否存在缺陷进行检测,防止含缺陷晶体管的芯片流出,以提升产品良率。

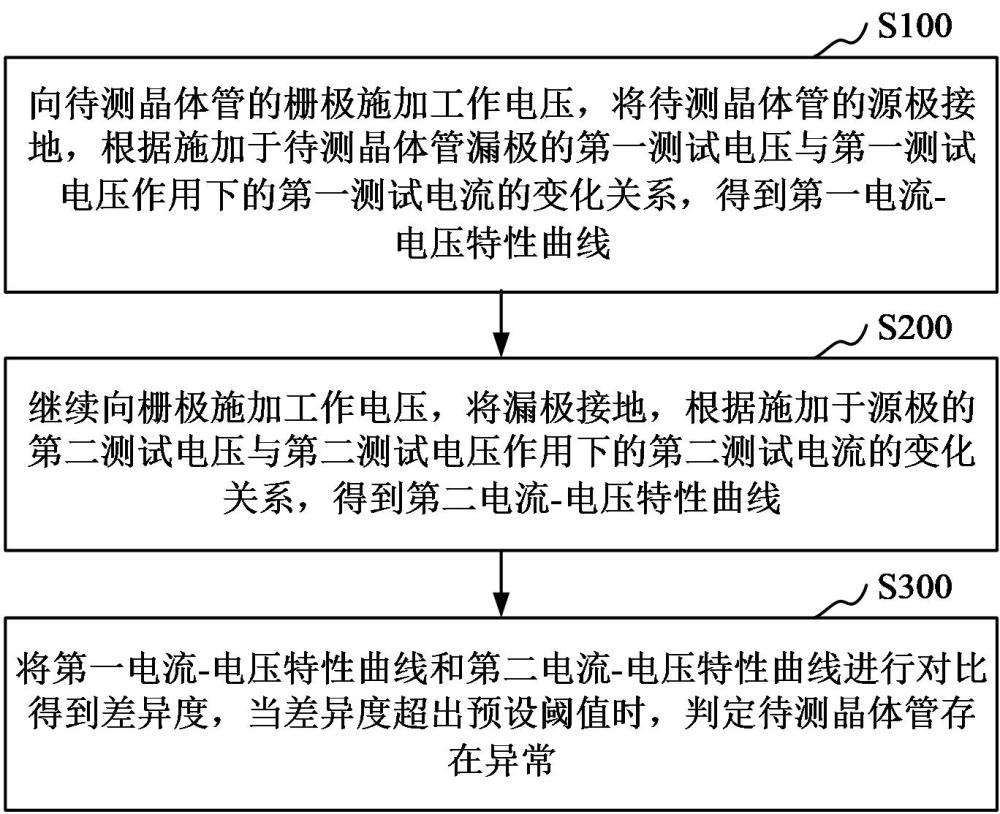

2、根据一些实施例,本申请一方面提供了一种晶体管测试方法,包括:

3、向待测晶体管的栅极施加工作电压,将所述待测晶体管的源极接地,根据施加于所述待测晶体管漏极的第一测试电压与所述第一测试电压作用下的第一测试电流的变化关系,得到第一电流-电压特性曲线;

4、继续向所述栅极施加所述工作电压,将所述漏极接地,根据施加于所述源极的第二测试电压与所述第二测试电压作用下的第二测试电流的变化关系,得到第二电流-电压特性曲线;

5、将所述第一电流-电压特性曲线和所述第二电流-电压特性曲线进行对比得到差异度,当所述差异度超出预设阈值时,判定所述待测晶体管存在异常。

6、在一些实施例中,所述第一测试电压包括动态变化的多个第一子电压,所述第一测试电流包括一一对应于多个所述第一子电压的多个第一子电流;所述第二测试电压包括动态变化的多个第二子电压,所述第二测试电流包括一一对应于多个所述第二子电压的多个第二子电流;

7、所述将所述第一电流-电压特性曲线和所述第二电流-电压特性曲线进行对比得到差异度,包括:

8、从所述第一电流-电压特性曲线和所述第二电流-电压特性曲线中分别确定第一采样点和第二采样点;对应于所述第一采样点的所述第一子电压和对应于所述第二采样点的所述第二子电压具有相同的电压值;

9、将对应于所述第一采样点的所述第一子电流和对应于所述第二采样点的所述第二子电流之间的差值作为所述差异度。

10、在一些实施例中,所述预设阈值包括电流的一个数量级。

11、在一些实施例中,所述当所述差异度超出预设阈值时,判定所述待测晶体管存在异常,包括:

12、若所述差异度超出预设阈值,且所述第一电流-电压特性曲线位于所述第二电流-电压特性曲线的下方,则判定所述源极存在异常。

13、在一些实施例中,所述当所述差异度超出预设阈值时,判定所述待测晶体管存在异常,包括:

14、若所述差异度超出预设阈值,且所述第二电流-电压特性曲线位于所述第一电流-电压特性曲线的下方,则判定所述漏极存在异常。

15、在一些实施例中,对应于所述第一采样点的所述第一子电压以及对应于所述第二采样点的所述第二子电压的电压值的取值范围为0.8v~1.5v。

16、在一些实施例中,对应于所述第一采样点的所述第一子电压以及对应于所述第二采样点的所述第二子电压的电压值,与所述工作电压的电压值相同。

17、在一些实施例中,所述待测晶体管位于衬底上;所述衬底包括第一类型阱区以及嵌入所述第一类型阱区且间隔排布的两个第二类型掺杂区;所述源极与其中一个所述第二类型掺杂区接触且所述漏极与另一个所述第二类型掺杂区接触;

18、所述将所述待测晶体管的源极接地,包括:将所述第一类型阱区接入参考电压;

19、所述将所述漏极接地,包括:继续将所述第一类型阱区接入所述参考电压。

20、在一些实施例中,所述将所述第一类型阱区接入参考电压,包括:将所述第一类型阱区接地;

21、所述继续将所述第一类型阱区接入所述参考电压,包括:继续将所述第一类型阱区接地。

22、根据一些实施例,本申请另一方面提供了一种存储器监控方法,用于对包括多个晶体管的存储器进行监控;所述存储器监控方法包括:

23、于多个所述晶体管中选取待测晶体管;采用如前述一些实施例所述的晶体管测试方法对所述待测晶体管进行测试。

24、本申请提供的晶体管测试方法及存储器监控方法,可以/至少具有以下意想不到的优点:

25、在本申请实施例中,先向待测晶体管的栅极施加工作电压,将待测晶体管的源极接地,从而可以根据施加于待测晶体管漏极的第一测试电压与第一测试电压作用下的第一测试电流的变化关系,得到第一电流-电压特性曲线;之后,继续向栅极施加工作电压,将漏极接地,从而可以根据施加于源极的第二测试电压与第二测试电压作用下的第二测试电流的变化关系,得到第二电流-电压特性曲线。通过对比第一电流-电压特性曲线与第二电流-电压特性曲线,得到二者的差异度;当差异度超出预设阈值时,表明当前待测晶体管的漏极或源极存在异常,则判定待测晶体管存在异常。采用本申请实施例,无论是在漏极存在异常还是在源极存在异常均可被及时发现,从而能够全面地对待测晶体管是否存在缺陷进行检测,防止含缺陷晶体管的芯片流出,提升产品良率。本申请实施例步骤简单易于实现,测试效率高,可便于应用于芯片生产制造过程中。

技术特征:

1.一种晶体管测试方法,其特征在于,包括:

2.根据权利要求1所述的晶体管测试方法,其特征在于,所述第一测试电压包括动态变化的多个第一子电压,所述第一测试电流包括一一对应于多个所述第一子电压的多个第一子电流;所述第二测试电压包括动态变化的多个第二子电压,所述第二测试电流包括一一对应于多个所述第二子电压的多个第二子电流;

3.根据权利要求2所述的晶体管测试方法,其特征在于,所述预设阈值包括电流的一个数量级。

4.根据权利要求3所述的晶体管测试方法,其特征在于,所述当所述差异度超出预设阈值时,判定所述待测晶体管存在异常,包括:

5.根据权利要求3所述的晶体管测试方法,其特征在于,所述当所述差异度超出预设阈值时,判定所述待测晶体管存在异常,包括:

6.根据权利要求2所述的晶体管测试方法,其特征在于,对应于所述第一采样点的所述第一子电压以及对应于所述第二采样点的所述第二子电压的电压值的取值范围为0.8v~1.5v。

7.根据权利要求2所述的晶体管测试方法,其特征在于,对应于所述第一采样点的所述第一子电压以及对应于所述第二采样点的所述第二子电压的电压值,与所述工作电压的电压值相同。

8.根据权利要求1所述的晶体管测试方法,其特征在于,所述待测晶体管位于衬底上;所述衬底包括第一类型阱区以及嵌入所述第一类型阱区且间隔排布的两个第二类型掺杂区;所述源极与其中一个所述第二类型掺杂区接触且所述漏极与另一个所述第二类型掺杂区接触;

9.根据权利要求8所述的晶体管测试方法,其特征在于,所述将所述第一类型阱区接入参考电压,包括:将所述第一类型阱区接地;

10.一种存储器监控方法,其特征在于,用于对包括多个晶体管的存储器进行监控;所述存储器监控方法包括:

技术总结

本申请涉及一种晶体管测试方法及存储器监控方法。该晶体管测试方法包括:向待测晶体管的栅极施加工作电压,将待测晶体管的源极接地,根据施加于待测晶体管漏极的第一测试电压与第一测试电压作用下的第一测试电流的变化关系,得到第一电流‑电压特性曲线;继续向栅极施加工作电压,将漏极接地,根据施加于源极的第二测试电压与第二测试电压作用下的第二测试电流的变化关系,得到第二电流‑电压特性曲线;将第一电流‑电压特性曲线和第二电流‑电压特性曲线进行对比得到差异度,当差异度超出预设阈值时,判定待测晶体管存在异常。该晶体管测试方法能够全面地对待测晶体管是否存在缺陷进行检测,防止含缺陷晶体管的芯片流出,以提升产品良率。

技术研发人员:马兰州,袁野,胡圆圆,韩冰

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!