一种芯片级联系统的制作方法

本发明涉及集成电路,尤其涉及一种芯片级联系统。

背景技术:

1、通过芯片级联可以支持更多串联的电芯系统,进行电池保护。传统级联芯片中,为了传递信号,相邻两个芯片中的上级芯片的两个输出管脚分别通过两条接线与相邻两个芯片中的下级芯片的两个输入管脚对应耦接,即为了实现通信上级芯片与下级芯片之间需要通过两条接线耦接,这样需要四个管脚,导致管脚数量较多,电路结构复杂,成本较高,并且由于上级芯片的两个输出管脚只有向外输出信息的能力,因此只能实现从上级芯片向下级芯片传输信息而不能实现下级芯片向上级芯片传输信息。

技术实现思路

1、本发明的目的是为了克服上述技术问题,提供一种芯片级联系统,在相邻级联的两个芯片之间进行通信时,使用的管脚的数量较少,简化了电路结构,有利于降低成本,且相邻芯片之间可以相互传输信息。

2、为了实现上述目的,本发明提供了一种芯片级联系统,所述芯片级联系统包括依次级联的至少两个芯片,相邻级联的两个芯片中:至少下级芯片包括上级通信管脚,至少上级芯片包括下级通信管脚;所述下级芯片的上级通信管脚与所述上级芯片的下级通信管脚耦接,所述上级芯片和所述下级芯片中的一者能够将数据信息转换为电流信号,并通过耦接的所述上级通信管脚和所述下级通信管脚发送给所述上级芯片和下级芯片中的另一者,所述上级芯片和所述下级芯片中的另一者能够根据所述电流信号获得所述数据信息。

3、可选地,当所述上级芯片向所述下级芯片传输所述数据信息时,所述数据信息包括第一数据信息,所述电流信号包括表征所述第一数据信息的第一电流信号;或,所述下级芯片向所述上级芯片传输所述数据信息时,所述数据信息包括第二数据信息,所述电流信号包括表征所述第二数据信息的第二电流信号;每个芯片包括通信模块,其中:所述通信模块包括下级通信单元,所述上级芯片中的所述下级通信单元能够将所述第一电流信号发送给所述下级芯片和/或接收所述下级芯片发送的所述第二电流信号并根据所述第二电流信号获得所述第二数据信息;和/或,所述通信模块包括上级通信单元,所述下级芯片中的所述上级通信单元能够将所述第二电流信号发送给所述上级芯片和/或接收所述上级芯片发送的所述第一电流信号并根据所述第一电流信号获得所述第一数据信息。

4、可选地,每个芯片包括电压管脚,其中:所述通信模块的下级通信单元包括第一开关和下级电流源,所述第一开关的一端耦接本级芯片的下级通信管脚,所述下级电流源的一端耦接所述第一开关的另一端,所述下级电流源的另一端与所述本级芯片的电压管脚耦接,所述第一开关用于接收表征所述第一数据信息的第一高低电平信号,并根据所述第一高低电平信号进行导通和闭合,使得所述下级电流源向所述本级芯片的下级通信管脚提供所述第一电流信号;和/或,所述通信模块的上级通信单元包括第一检测电路和第一电阻,所述第一电阻的一端与本级芯片的上级通信管脚耦接,另一端与所述本级芯片的电压管脚耦接,所述第一电阻能够通过所述本级芯片的上级通信管脚接收上一级芯片发送的所述第一电流信号,所述第一检测电路能够将所述第一电阻上由所述第一电流信号引起的电压波动转换为第一高低电平信号,所述第一高低电平信号能够表征所述第一数据信息。

5、可选地,所述通信模块的第一检测电路包括第一比较器,所述第一比较器的第一输入端与所述第一电阻的一端耦接,所述第一比较器的第二输入端与所述第一电阻的另一端耦接,所述第一比较器能够将其第一输入端和其第二输入端的电压差与第一偏差电压进行比较,以获得所述第一高低电平信号。

6、可选地,所述第一比较器包括第一pmos管、第二pmos管、第三pmos管、第一nmos管、第二nmos管、偏置电阻、第一电流源、第二电流源和第一反相器;所述第一pmos管、所述第二pmos管、所述第三pmos管各自的衬底与各自的源极耦接并与供电电压端耦接,所述第一pmos管、所述第二pmos管的栅极耦接并与所述第一pmos管的漏极及所述第一nmos管的漏极耦接;所述第二pmos管的漏极与所述第二nmos管的漏极耦接并与所述第三pmos管的栅极耦接;所述第一nmos管的栅极为所述第一比较器的第一输入端,所述第二nmos管的栅极为所述第一比较器的第二输入端,所述第一nmos管的衬底与所述第二nmos管的衬底耦接并与所述第一电流源和所述第二电流源各自的一端接地,所述偏置电阻的一端耦接所述第一nmos管的源极,另一端耦接所述第二nmos管的源极,所述第一电流源的另一端耦接所述偏置电阻的另一端;所述第三pmos管的漏极和所述第二电流源的另一端与所述第一反相器的输入端耦接,所述第一反相器的输出端为所述第一比较器的输出端。

7、可选地,每个芯片包括接地管脚,其中:所述通信模块的上级通信单元包括第二开关和上级电流源,所述第二开关的一端耦接本级芯片的上级通信管脚,所述上级电流源的一端耦接所述第二开关的另一端,所述上级电流源的另一端耦接所述本级芯片的下级通信管脚,所述第二开关能够接收表征所述第二数据信息的第二高低电平信号并根据所述第二高低电平信号进行导通和闭合,使得所述上级电流源向所述本级芯片的上级通信管脚提供所述第二电流信号;和/或,所述通信模块的下级通信单元包括第二检测电路和第二电阻,所述第二电阻的一端与本级芯片的下级通信管脚耦接,另一端与所述本级芯片的接地管脚耦接,所述第二电阻能够通过所述本级芯片的下级通信管脚接收下一级芯片发送的所述第二电流信号,所述第二检测电路能够将所述第二电阻上由所述第二电流信号引起的电压波动转换为第二高低电平信号,所述第二高低电平信号能够表征所述第二数据信息。

8、可选地,所述通信模块的第二检测电路包括第二比较器,所述第二比较器的第一输入端与所述第二电阻的一端耦接,所述第二比较器的第二输入端与所述第二电阻的另一端耦接,所述第二比较器能够将其第一输入端和其第二输入端的电压差与第二偏差电压进行比较,以获得所述第二高低电平信号。

9、可选地,所述第二比较器包括第一pmos管、第二pmos管、第一nmos管、第二nmos管、第三nmos管、偏置电阻、第一电流源、第二电流源和第一反相器;所述第一nmos管、所述第二nmos管、所述第三nmos管各自的衬底与各自的源极耦接并接地,所述第一nmos管的栅极和所述第二nmos管的栅极耦接并与所述第二nmos管的漏极及所述第一pmos管的漏极耦接,所述第一nmos管的漏极与所述第二pmos管的漏极耦接,并与所述第三nmos管的栅极耦接;所述第一pmos管的栅极为所述第二比较器的第一输入端,所述第二pmos管的栅极为所述第二比较器的第二输入端,所述第一pmos管的衬底与所述第二pmos管的衬底耦接并与所述第一电流源和所述第二电流源各自的一端耦接供电电压端,所述偏置电阻的一端耦接所述第一pmos管的源极,另一端耦接所述第二pmos管的源极,所述第一电流源的另一端耦接所述偏置电阻的一端,所述第二电流源的另一端与所述第三nmos管的漏极与所述第一反相器的输入端耦接,所述第一反相器的输出端为所述第二比较器的输出端。

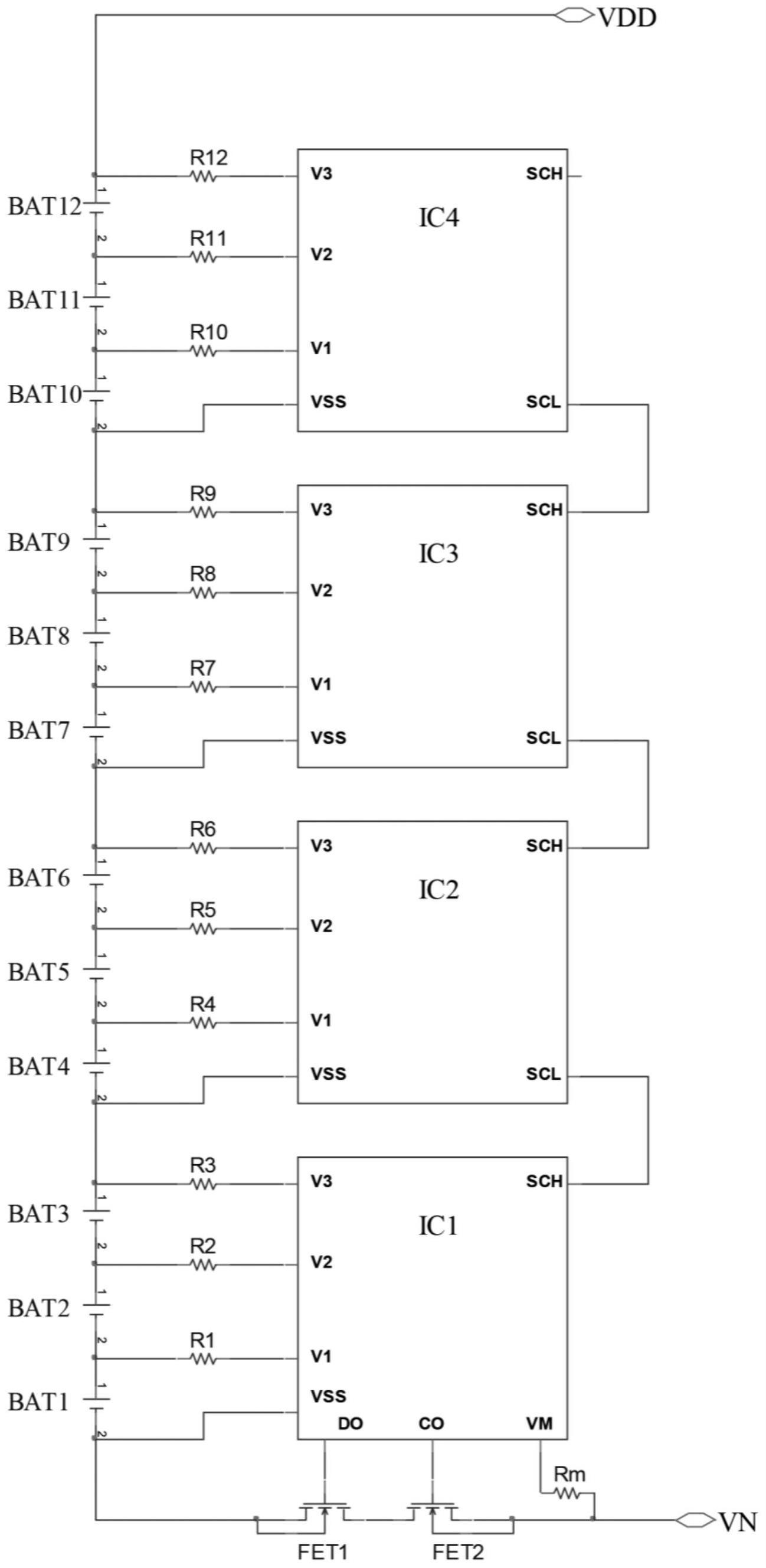

10、可选地,所述芯片级联系统包括多个电阻和串联的至少两个电池组,每个电池组包括一个或串联的两个以上电芯,所述电池组与所述芯片一一对应耦接,所述电池组的第一端与对应芯片的接地端耦接,所述电池组中每个电芯的远离所述电池组的第一端的端部通过所述多个电阻中的一个电阻与所述对应芯片的一个电压管脚耦接,相邻级联的两个芯片中所述下级芯片的电压管脚与所述上级芯片的接地管脚通过第三电阻耦接,所述下级芯片的第一电阻、所述第三电阻和所述上级芯片的第二电阻形成并联电路,所述第三电阻为所述多个电阻中的一个电阻。

11、可选地,每个所述芯片还包括检测模块和控制模块,所述检测模块用于检测对应耦接的所述电池组中的电芯的充电或放电参数信息;本级芯片的通信模块用于接收上一级芯片和下一级芯片中的一者发送的电流信号而获得所述上一级芯片和所述下一级芯片中的一者的数据信息;所述本级芯片的控制模块用于根据所述本级芯片的充电或放电参数信息和所述本级芯片的通信模块获得的所述数据信息形成表征本级芯片的数据信息的高低电平信号;所述本级芯片的通信模块还用于根据所述高低电平信号向所述上一级芯片和所述下一级芯片中的另一者发送表征所述本级芯片的数据信息的电流信号。

12、可选地,所述检测模块包括:电压检测模块,具有所述电压管脚、所述接地管脚以及与所述控制模块耦接的第一状态输出端和第二状态输出端,所述电压检测模块通过所述电压管脚检测对应耦接的电芯,其中:在检测到所述电芯出现充电过压时,将所述第一状态输出端的输出信号设置为高电平,并发送给所述控制模块;在检测到所述电芯出现放电过压时,将所述第二状态输出端的输出信号设置为高电平,并发送给所述控制模块;和/或,温度检测模块,用于检测本级芯片对应耦接的电芯的温度,并将检测结果发送给所述控制模块。

13、可选地,所述芯片级联系统还包括第一电压端、第二电压端、第一开关器件和第二开关器件,所述串联的至少两个电池组的第一端耦接所述第一电压端,所述第一开关器件和所述第二开关器件依次耦接于所述串联的至少两个电池组的第二端与所述第二电压端之间,依次级联的至少两个芯片中的第一级芯片的控制模块还包括第一输出管脚和第二输出管脚;所述第一开关器件的控制端与所述第一输出管脚耦接,所述第二开关器件的控制端与所述第二输出管脚耦接,其中:所述第一级芯片的控制模块还用于根据所述本级芯片的数据信息产生第一控制信号,并通过所述第一输出管脚输出,以控制所述第一开关器件截止实现禁止放电或控制所述第一开关器件导通实现恢复放电;和/或,所述第一级芯片的控制模块还用于根据所述本级芯片的数据信息产生第二控制信号,并通过所述第二输出管脚输出,以控制所述第二开关器件截止实现禁止充电或控制所述第二开关器件导通实现恢复充电。

14、可选地,所述第一级芯片的检测模块还包括电流检测模块,所述芯片级联系统还包括第四电阻,所述电流检测模块具有输入管脚,所述第四电阻的一端耦接所述输入管脚,另一端耦接所述第二电压端,所述电流检测模块还包括以下中的至少一者:第一输出端,当所述电流检测模块检测到所述输入管脚的电压大于第一设定电压时确定放电过流,将所述第一输出端的输出信号设置为高电平,并发送给所述控制模块;第二输出端,当所述电流检测模块检测到所述输入管脚的电压小于第二设定电压时确定充电过流,将所述第二输出端的输出信号设置为高电平,并发送给所述控制模块;第三输出端,当所述电流检测模块检测到所述输入管脚的电压大于第三设定电压时确定所述第二电压端耦接负载,将所述第三输出端的输出信号设置为高电平,并发送给所述控制模块;第四输出端,当所述电流检测模块检测到所述输入管脚的电压小于第四设定电压时确定所述第二电压端耦接充电器,将所述第四输出端的输出信号设置为高电平,并发送给所述控制模块。

15、在上述方案中,上级芯片和下级芯片中的一者能够将数据信息转换为电流信号,并通过耦接的上级通信管脚和下级通信管脚发送给上级芯片和下级芯片中的另一者,上级芯片和下级芯片中的另一者能够根据电流信号获得数据信息,这样在进行芯片级联时可减少管脚的数量,简化了电路结构,有利于降低成本,且相邻芯片之间可以相互传递信号,即上级芯片可向下级芯片传递信号,下级芯片也可向上级芯片传递信号。

16、本发明的其他特征和优点将在随后的具体实施方式部分予以详细说明。

- 还没有人留言评论。精彩留言会获得点赞!