具有时钟控制初始级和移位时钟控制附加级的多级电荷泵的制作方法

1.本发明涉及电荷泵(charge pump),更具体地,涉及提高可靠性和面积效率(area efficient)的电荷泵的实施例。

背景技术:

2.现代集成电路设计通常需要比可用的正和负供电电压更高的正或负电压(例如,分别为vdd和gnd)。通常,多级正电荷泵用于产生相对较高的正电压,尤其是大于vdd的正电压(例如,2*vdd、3*vdd等的正电压)。类似地,多级负电荷泵用于产生相对较高的负电压(例如,-1*vdd,-2*vdd等的负电压)。然而,在这种多级电荷泵中,每个较高(即下游)级需要比前一级更多的电容器(例如,更多串联电容器)或更高的电压电容器。此外,在下游级采用串联电容器的多级正和负电荷泵需要对内部电容器节点进行偏置。因此,此类多级正和负电荷泵相对复杂,并消耗大量芯片面积。

技术实现要素:

3.鉴于上述内容,本文公开了一种可靠性提高且面积效率高的多级电荷泵的实施例。在所公开的每个实施例中,电荷泵可以包括多个级(例如,第一级、第二级和可选的一个或多个附加级)。第一级可以是时钟控制的(例如,由第一时钟信号控制),并且可以响应于输入电压输出第一输出电压。第二级可以被移位时钟控制(例如,由已经相对于第一时钟信号移位的第二时钟信号控制)。具体地,第二时钟信号可以具有与第一时钟信号相同的振幅,但是第二时钟信号的高和低状态可以相对于第一时钟信号的高和低状态移位。例如,对于正电荷泵,第二时钟信号的高和低状态可以高于第一时钟信号的高和低状态,对于负电荷泵,反之亦然。在任何情况下,第二级可以响应于从第一级接收的第一输出电压输出第二输出电压。类似地,任何附加级可以被移位时钟控制(例如,由相对于控制前一级的时钟信号移位的附加时钟信号控制)。通过使多级电荷泵内控制下游级的时钟信号的高和低状态移位,而不是对所有级使用相同的时钟信号,这些实施例消除了在下游级中对串联或高压电容器的需求,从而降低了电路复杂性和芯片面积消耗,同时也提高了可靠性。

4.更具体地,本文公开了多级电荷泵的实施例。在每个实施例中,电荷泵可包括第一级。第一级可被配置为接收输入电压和具有第一高和低状态的第一时钟信号。第一级还可以被配置为响应于输入电压和第一时钟信号输出第一输出电压。第一输出电压的绝对值可以大于输入电压。在每个实施例中,电荷泵还可以包括时钟信号移位电路。时钟信号移位电路可被配置为接收输入电压和第一时钟信号。时钟信号移位电路还可以被配置为响应于输入电压和第一时钟信号,输出具有不同于第一高和低状态的第二高和低状态的第二时钟信号。如下文更详细地讨论的,在正电荷泵的情况下,第二时钟信号的第二高和低状态可移位到高于第一时钟信号的第一高和低状态的位置,而在负电荷泵的情况下,可移位到低于第一时钟信号的第一高和低状态的位置。在任何情况下,电荷泵可进一步包括第二级。第二级可被配置为接收来自第一级的第一输出电压和来自时钟信号移位电路的第二时钟信号。第

二级还可以被配置为响应于第一输出电压和第二时钟信号输出具有大于第一输出电压的绝对值的第二输出电压。

5.本文公开的一些实施例包括多级正电荷泵。多级正电荷泵可包括反相器。反相器可被配置为接收具有第一高和低状态的第一时钟信号。反相器还可以被配置为响应于第一时钟信号输出反相第一时钟信号。多级正电荷泵还可以包括第一级。第一级可被配置为接收正输入电压、第一时钟信号和反相第一时钟信号。第一级还可以被配置为响应于正输入电压、第一时钟信号和反相第一时钟信号,输出大于正输入电压的第一正输出电压。多级正电荷泵还可以包括时钟信号移位电路。时钟信号移位电路可被配置为接收正输入电压、第一时钟信号和反相第一时钟信号。时钟信号移位电路还可以被配置为响应于正输入电压、第一时钟信号和反相第一时钟信号输出第二时钟信号,该第二时钟信号具有不同于第一高和低状态的第二高和低状态,更具体地说,它们分别被移位到高于第一高和低状态的位置,以及输出反相第二时钟信号。多级正电荷泵还可以包括第二级。第二级可被配置为接收第一正输出电压、第二时钟信号和反相第二时钟信号。第二级还可以被配置为响应于第一正输出电压、第二时钟信号和反相第二时钟信号,输出大于第一正输出电压的第二正输出电压。

6.本文公开的一些实施例包括多级负电荷泵。多级负电荷泵可包括反相器。反相器可被配置为接收具有第一高和低状态的第一时钟信号。反相器还可以被配置为响应于第一时钟信号输出反相第一时钟信号。

7.多级负电荷泵还可以包括第一级。第一级可配置为接收0伏的输入电压、第一时钟信号和反相第一时钟信号。第一级还可以被配置为响应于输入电压、第一时钟信号和反相第一时钟信号输出第一负输出电压。多级负电荷泵还可以包括时钟信号移位电路。时钟信号移位电路可被配置为接收输入电压、第一时钟信号和反相第一时钟信号。时钟信号移位电路还可以被配置为响应于输入电压、第一时钟信号和反相第一时钟信号输出第二时钟信号,该第二时钟信号具有不同于第一高和低状态的第二高和低状态,更具体地,它们分别被移位到低于第一高和低状态的位置,以及输出反相第二时钟信号。多级负电荷泵还可以包括第二级。第二级可被配置为接收第一负输出电压、第二时钟信号和反相第二时钟信号。第二级还可以配置为响应于第一负输出电压、第二时钟信号和反相第二时钟信号,输出小于第一负输出电压的第二负输出电压。

附图说明

8.通过以下参考附图的详细说明,可以更好地理解本发明,这些附图不一定按比例绘制,其中:

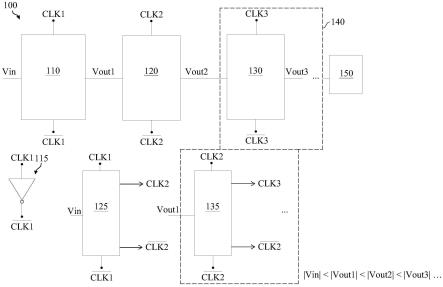

9.图1为多级电荷泵的公开实施例的示意图;

10.图1a为可生成并用于正电荷泵的clk1、clk1b、clk2、clk2b、clk3和clk3b的示例性波形的示意图;

11.图1b为可生成并用于负电荷泵的clk1、clk1b、clk2、clk2b、clk3和clk3b的示例性波形的示意图;

12.图2为多级正电荷泵的公开实施例的示意图;

13.图2a为说明当clk1处于高状态(例如,在vdd)时多级正电荷泵的操作的示意图;

14.图2b为说明当clk1处于低状态(例如,在0伏)时多级正电荷泵的操作的示意图;

15.图3为多级负电荷泵的公开实施例的示意图;

16.图3a为说明当clk1处于高状态(例如,在vdd)时多级负电荷泵的操作的示意图;以及

17.图3b为说明当clk1处于低状态(例如,在0伏)时多级负电荷泵的操作的示意图。

具体实施方式

18.如上所述,现代集成电路设计通常需要比可用的正和负供电电压更高的正或负电压(例如,分别为vdd和gnd)。通常,多级正电荷泵用于产生相对较高的正电压,尤其是大于vdd的正电压(例如,2*vdd、3*vdd等的正电压)。类似地,多级负电荷泵用于产生相对较高的负电压(例如,-1*vdd,-2*vdd等的负电压)。然而,在这种多级电荷泵中,每个较高(即下游)级需要比前一级更多的电容器(例如,更多串联电容器)或更高的电压电容器。此外,在下游级采用串联电容器的多级正和负电荷泵需要对内部电容器节点进行偏置。因此,此类多级正和负电荷泵相对复杂,并消耗大量芯片面积。

19.鉴于上述情况,本文公开了一种可靠性提高且面积效率高的多级电荷泵的实施例。在所公开的每个实施例中,电荷泵可以包括多个级(例如,第一级、第二级和可选的一个或多个附加级)。第一级可以是时钟控制的(例如,由第一时钟信号控制),并且可以响应于输入电压输出第一输出电压。第二级可以被移位时钟控制(例如,由已经相对于第一时钟信号移位的第二时钟信号控制)。具体地,第二时钟信号可以具有与第一时钟信号相同的振幅,但是第二时钟信号的高和低状态可以相对于第一时钟信号的高和低状态移位。例如,对于正电荷泵,第二时钟信号的高和低状态可以高于第一时钟信号的高和低状态,对于负电荷泵,反之亦然。在任何情况下,第二级可以响应于从第一级接收的第一输出电压输出第二输出电压。类似地,任何附加级可以被移位时钟控制(例如,由相对于控制前一级的时钟信号移位的附加时钟信号控制)。通过使多级电荷泵内控制下游级的时钟信号的高和低状态移位,而不是对所有级使用相同的时钟信号,这些实施例消除了在下游级中对串联或高压电容器的需要,从而降低了电路复杂性和芯片面积消耗,同时也提高了可靠性。

20.更具体地,参考图1,本文公开了多级电荷泵100的实施例。电荷泵100可以是正电荷泵,其产生相对较高的正电压,尤其是大于vdd的正电压(例如,2*vdd、3*vdd的正电压等)。或者,电荷泵100可以是产生相对高的负电压(例如,-1*vdd,-2*vdd的负电压等)的负电荷泵。

21.在任何情况下,电荷泵100可包括第一级110和反相器115。反相器115可以被配置为接收第一时钟信号(clk1)(例如,从传统时钟生成电路)。clk1可以在第一个高和低状态之间振荡。在一些实施例中,第一高状态可以处于正供电电压电平(例如,在vdd处),第一低状态可以处于接地(例如,在0伏处)。反相器115还可以被配置为将clk1反相,响应于第一时钟信号输出反相第一时钟信号(clk1b)。因此,当clk1处于第一高状态(例如,在vdd处)时,clk1b将处于第一低状态(例如0伏),反之亦然。第一级110可被配置为在电压输入节点处接收输入电压(vin)。例如,在正电荷泵的情况下,vin可以处于正供电电压电平(例如,在vdd处);而在负电荷泵的情况下,vin可能位于接地(例如,在0伏处)。第一级110还可以被配置为接收clk1和clk1b。第一级110还可以被配置为响应于vin、clk1和clk1b,在电压输出节点

处输出第一输出电压(vout1)。vout1的绝对值可能大于vin。例如,在vin为vdd的正电荷泵的情况下,vout1可以是正供电电压电平的两倍(即,2*vdd);而在vin为0伏的负电荷泵的情况下,vout1可能为正供电电压电平的负一倍(即-1*vdd)。

22.电荷泵100还可以包括第一时钟信号移位电路125和第二级120。第一时钟信号移位电路125可被配置为接收vin、clk1和clk1b。第一时钟信号移位电路125还可以被配置为响应于vin、clk1和clk1b输出第二时钟信号(clk2)和反相第二时钟信号(clk2bar)。具体地,第一时钟信号移位电路125可以被配置成生成clk2,其在分别不同于clk1的第一高和低状态的第二高和低状态之间振荡。在正电荷泵的情况下,clk2可以相对于clk1移位,使得第二高和低状态分别高于第一高和低状态(例如,使得第二高和低状态分别为2*vdd和vdd,而不是分别为vdd和0伏);而在负电荷泵的情况下,clk2可以相对于clk1移位,使得第二高和低状态分别低于第一高和低状态(例如,使得第二高和低状态分别为0伏和-1*vdd,而不是分别为vdd和0伏)。在任何情况下,可以配置第一时钟信号移位电路125,使得当clk2处于第二高状态时,clk2b将处于第二低状态,反之亦然。第二级120可被配置为在电压输入节点处从第一级110接收vout1。第二级120还可以被配置为从第一时钟信号移位电路125接收clk2和clk2b。第二级120还可以被配置为响应于vout1、clk2和clk2bar,在电压输出节点处输出第二输出电压(vout2)。vout2的绝对值可以大于vout1。例如,在vout1为2*vdd的正电荷泵的情况下,vout2可以处于正供电电压电平的三倍(即,处于3*vdd);而在vout1处于-1*vdd的负电荷泵的情况下,vout2可能处于正供电电压电平的负两倍(即-2*vdd)。

23.可选地,电荷泵100还可以包括一个或多个附加下游级和对应的时钟信号移位电路140。

24.例如,可选地,电荷泵100还可以包括第二时钟信号移位电路135和第三级130。第二时钟信号移位电路135可以被配置为接收vout1、clk2和clk2b。第二时钟信号移位电路135还可以被配置为响应于vout1、clk2和clk2b输出第三时钟信号(clk3)和反相第三时钟信号(clk3bar)。具体地,第二时钟信号移位电路135可以被配置成生成clk3,其在分别不同于clk1的第一高和低状态并且也分别不同于clk2的第二高和低状态的第三高和低状态之间振荡。具体地,在正电荷泵的情况下,clk3可以相对于clk2移位,使得第三高和低状态分别高于第二高和低状态(例如,使得第三高和低状态分别处于3*vdd和2*vdd);而在负电荷泵的情况下,clk3可以相对于clk2移位,使得第三高和低状态分别低于第二高和低状态(例如,使得第三高和低状态分别处于-1*vdd和-2*vdd)。在任何情况下,可以配置第二时钟信号移位电路135,使得当clk3处于第三高状态时,clk3b将处于第三低状态,反之亦然。第三级130可以被配置为在电压输入节点处从第二级120接收vout2,并且还从第二时钟信号移位电路135接收clk3和clk3b两者。第三级130还可以被配置为响应于vout2、clk3和clk3bar,在电压输出节点处输出第三输出电压(vout3)。vout3的绝对值可以大于vout2。例如,在vout2为3*vdd的正电荷泵的情况下,vout3可以处于正供电电压电平的四倍(即,处于4*vdd);而在vout2处于-2*vdd负电荷泵的情况下,vout3可以处于正供电电压电平的负三倍(即,处于-3*vdd)。

25.图1a为clk1、clk1b、clk2、clk2b、clk3和clk3b的示例性波形的示意图,如上文所述,所述示例性波形可被生成并用于正电荷泵。图1b为clk1、clk1b、clk2、clk2b、clk3和clk3b的示例性波形的示意图,如上文所述,所述示例性波形可被生成并用于负电荷泵中。

因此,如图所示,无论电荷泵是正电荷泵还是负电荷泵,在每一级使用的时钟信号(即clk1、clk2、clk3等)具有相等的峰值振幅。也就是说,在每个阶段使用的时钟信号基本上具有相同的峰值振幅,其作为高状态和低状态之间的距离进行测量,并等于vdd的绝对值。

26.可选地,电荷泵100还可包括第三时钟信号移位电路和第四级(未示出)。第三时钟信号移位电路可配置为接收vout2、clk3和clk3b。第三时钟信号移位电路还可被配置为响应于vout2、clk3和clk3b输出第四时钟信号(clk4)和反相第四时钟信号(clk4bar)。具体地,第三时钟信号移位电路可被配置为产生在第四高和低状态之间振荡的clk4。在正电荷泵的情况下,clk4可以相对于clk3移位,使得第四高和低状态分别高于第三高和低状态(例如,使得第四高和低状态分别处于4*vdd和3*vdd);而在负电荷泵的情况下,clk4可以相对于clk3移位,使得第四高和低状态分别低于第三高和低状态(例如,使得第四高和低状态分别位于-2*vdd和-3*vdd)。在任何情况下,可以配置第三时钟信号移位电路,以便当clk4处于第四高状态时,clk4b将处于第四低状态,反之亦然。第四级可配置为从第三级130接收vout3,并从第三时钟信号移位电路接收clk4和clk4b两者。第四级还可以被配置为响应于vout3、clk4和clk4bar,输出具有比vout3更大绝对值的第四输出电压(vout4)。例如,在vout3为4*vdd的正电荷泵的情况下,vout4可处于正供电电压电平的五倍(即,处于5*vdd);而在vout3处于-3*vdd的负电荷泵的情况下,vout4可能处于正供电电压电平的负四倍(即,处于-4*vdd)。

27.可选地,电荷泵100还可包括附加时钟信号移位电路和附加级,其配置方式基本上与上述相同,但未示出。

28.在任何情况下,最后一级的电压输出节点都可以连接到电气负载150。

29.应注意,在电荷泵100的每个级110、120、130等中,当控制clk信号在高和低状态之间振荡时,输出电压(例如,分别为vout1、vout2、vout3等)将基本保持恒定。本领域已知各种不同的电荷泵级配置,其中基于输入电压、时钟信号和反相时钟信号在每个级的输出节点处基本上不断地产生相对较高的正或负输出电压。这些电荷泵级配置中的任何一个都可用于本文公开的电荷泵100的级。然而,应当理解,在所公开的电荷泵100的实施例中,不是使用相同的时钟信号/反相时钟信号对(通常情况下)控制所有级,只有第一级110由来自时钟信号发生器的时钟信号控制,而来自反相器115和所有其他下游级120、130等的反相时钟信号由已相对于控制前一级的时钟信号/反相时钟信号对移位的不同的时钟信号/反相时钟信号对控制。通过使多级电荷泵内控制下游级的时钟信号的高和低状态移位,而不是对所有级使用相同的时钟信号,本实施例消除了在下游级中对串联或高压电容器的需要,从而降低了电路复杂性和芯片面积消耗。

30.为了说明的目的,图2为更详细地说明示例性正电荷泵200的示意图。图2a和图2b为分别进一步图示当clk1处于高状态和当clk1处于低状态时图2的正电荷泵200的操作的示意图。如上所述,图1a为可生成并用于这种正电荷泵的clk1、clk1b、clk2、clk2b、clk3和clk3b的示例性波形的示意图。

31.更具体地,参考图2,本文公开了多级正电荷泵200的实施例,其产生相对较高的正电压,尤其是高于vdd的正电压(例如,2*vdd、3*vdd等的正电压)。

32.正电荷泵200还可包括多个级,包括第一级210、第二级220和可选的一个或多个附加级(例如,第三级230、第四级等)。每个级210、220、230等可包括电压输入节点和电压输出

节点。每个级210、220、230还可以包括第一反相器以及第二反相器,第一反相器包括在电压输入节点和电压输出节点之间串联连接的p型场效应晶体管(pfet)211a、221a、231a和n型场效应晶体管(nfet)211b、221b、231b,第二反相器类似地包括在电压输入节点和电压输出节点之间串联连接的pfet212a、222a、232a和nfet 212b、222b、232b,使得第一和第二反相器并联连接。第一和第二反相器还可以交叉耦合。也就是说,第一反相器的pfet和nfet 211a-211b、221a-221b、231a-231b的栅极可以连接到第二反相器的pfet和nfet 212a-212b、222a-222b、232a-232b之间的结,反之亦然。每个级210、220、230等还可以包括第一电容器213、223、233和第二电容器214、224、234。第一电容器213、223、233可以包括由介电层隔开的第一电容器板,其中一个第一电容器板连接到第一反相器的pfet和nfet之间的结,另一个第一电容器板连接以接收时钟信号(如下文关于每个特定级更详细地讨论的)。类似地,第二电容器214、224、234可以包括由介电层隔开的第二电容器板,其中一个第二电容器板连接到第二反相器的pfet和nfet之间的结,另一个第二电容器板被连接以接收反相时钟信号(如下文关于每个特定级更详细地讨论的)。

33.正电荷泵200还可包括反相器215。反相器215可被配置为接收第一时钟信号(clk1)(例如,从传统时钟生成电路)。clk1可以在第一个高和低状态之间振荡。在一些实施例中,第一高状态可以处于正供电电压电平(例如,在vdd处),第一低状态可以处于接地(例如,在0伏处)。反相器215还可以被配置为将clk1反相,响应于第一时钟信号输出反相第一时钟信号(clk1b)。因此,当clk1处于第一高状态(例如vdd)时,clk1b将处于第一低状态(例如0伏),反之亦然。

34.第一级210可在电压输入节点处接收正输入电压(vin)。vin可以处于正供电电压电平(例如vdd)。另外,clk1可以应用于第一电容器213,clk1b可以应用于第二电容器214。因此,第一级210的电压输出节点处的第一输出电压(vout1)将为正供电电压电平的两倍(即,在2*vdd处),并且无论clk1处于高状态还是低状态,它都将保持基本恒定。

35.正电荷泵200还可包括第一时钟信号移位电路225。第一时钟信号移位电路225可以包括一对pfet 226和227,其中一个pfet 226连接在电压输入节点和第二时钟信号输出节点之间,另一个pfet 227连接在电压输入节点和反相第二时钟信号输出节点之间。pfet 226和227的栅极可分别连接到反相第二时钟信号输出节点和第二时钟信号输出节点。第一时钟信号移位电路225还可以包括一对电容器228和229,其中一个电容器228连接在第一时钟信号输入节点和第二时钟信号输出节点之间,另一个电容器229连接在反相第一时钟信号输入节点和反相第二时钟信号输出节点之间。通过这种配置,第一时钟信号移位电路225可以在电压输入节点处接收vin,在第一时钟信号输入节点处接收clk1,在反相第一时钟信号输入节点处接收clk1b,并且响应于vin、clk1和clk1b,可以在第二时钟信号输出节点处输出第二时钟信号(clk2),以及在反相第二时钟信号输出节点处输出反相第二时钟信号(clk2bar)。clk2将在分别高于clk1的第一高和低状态的第二高和低状态之间振荡(例如,将分别在2*vdd和vdd之间振荡,而不是分别在vdd和0伏之间振荡),当clk2处于第二高状态时,clk2b将处于第二低状态,反之亦然。

36.第二级220可在电压输入节点处从第一级210接收vout1(例如,在2*vdd处)。另外,clk2可以应用于第一电容器223,clk2b可以应用于第二电容器224。因此,第二级220的电压输出节点处的第二输出电压(vout2)将为正供电电压电平的三倍(即,在3*vdd处),并且无

论clk2处于高状态还是低状态,它都将保持基本恒定。

37.可选地,正电荷泵200还可以包括一个或多个附加下游级和对应的时钟信号移位电路240。

38.例如,可选地,正电荷泵200还可以包括第二时钟信号移位电路235和第三级230。第二时钟信号移位电路235可以包括一对pfet 236和237,其中一个pfet 236连接在输入节点和第三时钟信号输出节点之间,另一个pfet 237连接在输入节点和反相第三时钟信号输出节点之间。pfet 236和237的栅极可分别连接到反相第三时钟信号输出节点和第三时钟信号输出节点。第二时钟信号移位电路235还可以包括一对电容器238和239,其中一个电容器238连接在第二时钟信号输入节点和第三时钟信号输出节点之间,另一个电容器239连接在反相第二时钟信号输入节点和反相第三时钟信号输出节点之间。利用此配置,第二时钟信号移位电路235可以在电压输入节点处接收vout1,在第二时钟信号输入节点处接收clk2,在反相第二时钟信号输入节点处接收clk2b,并且响应于vout1、clk2和clk2b,可以在第三时钟信号输出节点处输出第三时钟信号(clk3)和在反相第三时钟信号输出节点处输出反相第三时钟信号(clk3bar)。clk3将在分别高于clk2的第二高和低状态的第三高和低状态之间振荡(例如,将分别在3*vdd和2*vdd之间振荡),并且当clk3处于第三高状态时,clk3b将处于第三低状态,反之亦然。

39.可选地,正电荷泵200还可以包括第三时钟信号移位电路和第四级(未示出)。第三时钟信号移位电路可以包括一对pfet,其中一个pfet连接在输入节点和第四时钟信号输出节点之间,另一个pfet连接在输入节点和反相第四时钟信号输出节点之间。pfet的栅极可分别连接到反相第四时钟信号输出节点和第四时钟信号输出节点。第三时钟信号移位电路还可以包括一对电容器,其中一个电容器连接在第三时钟信号输入节点和第四时钟信号输出节点之间,另一个电容器连接在反相第三时钟信号输入节点和反相第四时钟信号输出节点之间。通过这种配置,第三时钟信号移位电路可以在电压输入节点处接收vout2,在第三时钟信号输入节点处接收clk3,在反相第三时钟信号输入节点处接收clk3b,并且响应于vout2、clk3和clk3b,可以在第四时钟信号输出节点处输出第四时钟信号(clk4)和在反相第四时钟信号输出节点处输出反相第四时钟信号(clk4bar)。clk4将在分别高于clk3的第三高和低状态的第四高和低状态之间振荡(例如,将分别在4*vdd和3*vdd之间振荡),并且当clk4处于第四高状态时,clk4b将处于第四低状态,反之亦然。

40.可选地,正电荷泵200还可包括附加时钟信号移位电路和附加级,其配置方式与上述方式基本相同,但未示出。在任何情况下,最后级的电压输出节点可以连接到电气负载250。例如,电气负载250可以是在最后级的电压输出节点和接地之间并联连接的电阻器和电容器。或者,电气负载250可以是消耗功率或能量的任何其他合适的电气负载。

41.应注意,在现有技术的正电荷泵中,所有级均由相同的时钟信号/反相时钟信号对控制,每个下游级中的每个电容器必须是更高的电压电容器,或者必须包括比前一级中的对应电容器更大的电容器串联组合,以实现所需的电压输出。例如,在没有时钟信号移位电路的情况下,第二级220的电容器223和224必须是比第一级210的电容器213和214更高的电压电容器或必须是更大的电容器串联组合;否则,第三级230的电容器233和234必须是比第二级220的电容器223和224更高的电压电容器,或者必须是更大的电容器串联组合,并以此类推。然而,通过使正电荷泵200内控制下游级的时钟信号的高和低状态移位,而不是对所

有级使用相同的时钟信号,图2所示的结构消除了在下游级中对串联或高压电容器的需要,从而降低了电路复杂性和芯片面积消耗。

42.为了说明的目的,图3为更详细地说明示例性负电荷泵300的示意图。图3a和图3b是分别进一步图示当clk1处于高状态和当clk1处于低状态时图3的负电荷泵300的操作的示意图。如上所述,图1b为可生成并用于这种负电荷泵的clk1、clk1b、clk2、clk2b、clk3和clk3b的示例性波形的示意图。

43.更具体地,参考图3,本文公开了多级负电荷泵300的实施例,其产生相对较高的负电压(例如,-1*vdd,-2*vdd的负电压等)。

44.负电荷泵300还可以包括多个级,包括第一级310、第二级320和可选的一个或多个附加级(例如,第三级330、第四级等)。每个级310、320、330等可包括电压输入节点和电压输出节点。每级310、220、330还可以包括第一反相器以及第二反相器,第一反相器包括串联在电压输入节点和电压输出节点之间的nfet 311a、321a、331a和pfet311b、321b、331b,第二反相器类似地包括串联连接在电压输入节点和电压输出节点之间的nfet 312a、322a、332a和pfet 312b、322b,332b,使得第一和第二反相器并联连接。第一和第二反相器还可以交叉耦合。即,第一反相器的nfet和pfet 311a-311b、321a-321b、331a-231b的栅极可连接到第二反相器的nfet和pfet 312a-312b、

45.322a-322b、332a-332b之间的结处,反之亦然。每个级310、320、330等还可以包括第一电容器313、323、333和第二电容器314、324、334。第一电容器313、323、333可以包括由介电层隔开的第一电容器板,其中一个第一电容器板连接到第一反相器的nfet和pfet之间的结,另一个第一电容器板连接以接收时钟信号(如下文关于每个特定级的更详细讨论)。类似地,第二电容器314、324、334可以包括由介电层隔开的第二电容器板,其中一个第二电容器板连接到第二反相器的nfet和pfet之间的结,另一个第二电容器板连接以接收反相时钟信号(如下文关于每个特定级的更详细讨论)。

46.负电荷泵300还可包括反相器315。反相器315可被配置为接收第一时钟信号(clk1)(例如,从传统时钟生成电路)。clk1可以在第一高和低状态之间振荡。在一些实施例中,第一高状态可以处于正供电电压电平(例如,在vdd处),第一低状态可以处于接地(例如,在0伏处)。反相器315还可以被配置为将clk1反相,响应于第一时钟信号输出反相第一时钟信号(clk1b)。因此,当clk1处于第一高状态(例如vdd)时,clk1b将处于第一低状态(例如0伏),反之亦然。

47.第一级310可在电压输入节点处接收例如0伏的输入电压(vin)。另外,clk1可以应用于第一电容器313,clk1b可以应用于第二电容器314。因此,第一级310的电压输出节点处的第一输出电压(vout1)将处于正供电电压电平的负一倍(即,处于-1*vdd),并且无论clk1处于高状态还是低状态,它都将保持基本恒定。

48.负电荷泵300还可以包括第一时钟信号移位电路325。第一时钟信号移位电路325可以包括一对nfet 326和327,其中一个nfet 326连接在电压输入节点和第二时钟信号输出节点之间,另一个nfet 327连接在电压输入节点和反相第二时钟信号输出节点之间。neft 326和327的栅极可分别连接到反相第二时钟信号输出节点和第二时钟信号输出节点。第一时钟信号移位电路325还可以包括一对电容器328和329,其中一个电容器328连接在第一时钟信号输入节点和第二时钟信号输出节点之间,另一个电容器329连接在反相第

一时钟信号输入节点和反相第二时钟信号输出节点之间。通过这种配置,第一时钟信号移位电路325可以在电压输入节点处接收vin,在第一时钟信号输入节点处接收clk1,在反相第一时钟信号输入节点处接收clk1b,并且响应于vin、clk1和clk1b,可以在第二时钟信号输出节点处输出第二时钟信号(clk2),以及在反相第二时钟信号输出节点处输出反相第二时钟信号(clk2bar)。clk2将在分别低于clk1的第一高和低状态的第二高和低状态之间振荡(例如,将分别在0伏和-1*vdd之间振荡,而不是分别在vdd和0伏处振荡),并且当clk2处于第二高状态时,clk2b将处于第二低状态,反之亦然。

49.第二级320可在电压输入节点处从第一级310接收vout1(例如,在-1*vdd)。另外,clk2可以应用于第一电容器323,clk2b可以应用于第二电容器324。因此,第二级320的电压输出节点处的第二输出电压(vout2)将处于正供电电压电平的负两倍(即,处于-2*vdd),并且无论clk2处于高状态还是低状态,它都将保持基本恒定。

50.可选地,负电荷泵300还可以包括一个或多个附加下游级和对应的时钟信号移位电路340。

51.例如,可选地,负电荷泵300还可以包括第二时钟信号移位电路335和第三级330。第二时钟信号移位电路335可以包括一对nfet 336和337,其中一个nfet 336连接在输入节点和第三时钟信号输出节点之间,另一个nfet 337连接在输入节点和反相第三时钟信号输出节点之间。nfet 336和337的栅极可分别连接到反相第三时钟信号输出节点和第三时钟信号输出节点。第二时钟信号移位电路335还可以包括一对电容器338和339,其中一个电容器338连接在第二时钟信号输入节点和第三时钟信号输出节点之间,另一个电容器339连接在反相第二时钟信号输入节点和反相第三时钟信号输出节点之间。通过该配置,第二时钟信号移位电路335可以在电压输入节点处接收vout1,在第二时钟信号输入节点处接收clk2,在反相第二时钟信号输入节点处接收clk2b,并且响应于vout1、clk2和clk2b,可以输出在第三时钟信号输出节点处输出第三时钟信号(clk3)和在反相第三时钟信号输出节点处输出反相第三时钟信号(clk3bar)。clk3将在分别低于clk2第二高和低状态的第三高和低状态之间振荡(例如,可分别在-1*vdd和-2*vdd之间振荡),并且当clk3处于第三高状态时,clk3b将处于第三低状态,反之亦然。

52.可选地,负电荷泵300还可以包括第三时钟信号移位电路和第四级(未示出)。第三时钟信号移位电路可以包括一对nfet,其中一个nfet连接在输入节点和第四时钟信号输出节点之间,另一个nfet连接在输入节点和反相第四时钟信号输出节点之间。nfet的栅极可分别连接到反相第四时钟信号输出节点和第四时钟信号输出节点。第三时钟信号移位电路还可以包括一对电容器,其中一个电容器连接在第三时钟信号输入节点和第四时钟信号输出节点之间,另一个电容器连接在反相第三时钟信号输入节点和反相第四时钟信号输出节点之间。通过这种配置,第三时钟信号移位电路可以在电压输入节点处接收vout2,在第三时钟信号输入节点处接收clk3,在反相第三时钟信号输入节点处接收clk3b,并且响应于vout2、clk3和clk3b,可以在第四时钟信号输出节点处输出第四时钟信号(clk4)和在反相第四时钟信号输出节点处输出反相第四时钟信号(clk4bar)。clk4将在分别高于clk3的第三高和低状态的第四高和低状态之间振荡(例如,将分别在-2*vdd和-3*vdd之间振荡),并且当clk4处于第四高状态时,clk4b将处于第四低状态,反之亦然。

53.可选地,负电荷泵300还可以包括附加时钟信号移位电路和附加级,其配置方式基

本上与上述相同,但未示出。在任何情况下,最后级的电压输出节点可以连接到电气负载350。例如,电气负载350可以是在最后级的电压输出节点和接地之间并联连接的电阻器和电容器。或者,电气负载350可以是消耗功率或能量的任何其他合适的电气负载。

54.应注意,在现有技术的负电荷泵中,所有级均由相同的时钟信号/反相时钟信号对控制,每个下游级中的每个电容器必须是更高的电压电容器,或者必须包括比前一级中的对应电容器更大的电容器串联组合,以实现所需的电压输出。例如,在没有时钟信号移位电路的情况下,第二级320的电容器323和324否则必须是比第一级310的电容器313和314更高的电压电容器或必须是更大的电容器串联组合;否则,第三级330的电容器333和334必须是比第二级320的电容器323和324更高的电压电容器,或者必须是更大的电容器串联组合;等等。然而,通过使负电荷泵300内控制下游级的时钟信号的高和低状态移位,而不是对所有级使用相同的时钟信号,图3所示的结构消除了在下游级中对串联或高压电容器的需要,从而降低了电路复杂性和芯片面积消耗。

55.在上述多级电荷泵实施例中,电容器的总数,包括级内和时钟信号移位电路内的电容器(但不包括负载电容),可使用以下等式计算:

56.电容器总数=2(2n-1),其中n等于多级电荷泵内的总级数。这明显少于现有技术中的电容器总数,其中,例如,两级电荷泵可能需要10个电容器,三级电荷泵可能需要28个电容器,四级电荷泵可能需要60个电容器,依此类推。综上所述,与上述和图中所示的上述公开的多级电荷泵实施例中的每一个相关联的优点包括但不限于使用低压电容器和/或晶体管的实施、在每级中仅使用两个低电压电容器(而不是两个高压电容器或两个串联电容器组合)以减少面积消耗的实施、无需偏置每级中的电容器串联组合的内部电容器节点以提高可靠性的实施、以及通过安全工作区(soa)规范。

57.应当理解,本文使用的术语是为了描述所公开的结构和方法,并不打算限制。例如,如本文所使用的,除非上下文另有明确指示,否则单数形式“一”、“一个”和“该”也意在包括复数形式。此外,如本文所用,术语“包括”、“包括”和/或“包括”指定所述特征、整数、步骤、操作、元件和/或组件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元件、组件和/或其群组的存在或添加。此外,如本文所用,诸如“右”、“左”、“垂直”、“水平”、“顶部”、“底部”、“上”、“下方”、“之下”、“下方的”、“上方”、“上方的”、“平行”、“垂直”等,旨在描述它们在图中的相对位置(除非另有说明),而诸如“碰触”、“直接接触”、“邻接”、“直接相邻”、“紧邻”等之类的术语旨在表示至少一个元件与另一个元件物理接触(没有其他元件分隔所描述的元件)。术语“横向”在本文中用于描述元件的相对位置,更具体地,表示一个元件位于另一个元件的一侧,而不是在另一个元件的上方或下方,因为这些元件是定向和图示在图纸中。例如,与另一个元件横向相邻的元件将在另一个元件旁边,与另一个元件横向紧邻的元件将直接在另一个元件旁边,而横向围绕另一个元件的元件将是与另一个元件的外侧壁相邻并与之接壤。以下权利要求中的所有装置或步骤加上功能元件的相应结构、材料、动作和等同物旨在包括用于与如具体要求保护的其他要求保护的元件组合来执行功能的任何结构、材料或动作。

58.本发明的各种实施例的描述是出于说明的目的而呈现的,但并不旨在穷举或限于所公开的实施例。在不脱离所描述实施例的范围和精神的情况下,许多修改和变化对于本领域普通技术人员来说将是显而易见的。选择此处使用的术语以最好地解释实施例的原

理、实际应用或对市场中发现的技术的技术改进,或者使本领域普通技术人员能够理解此处公开的实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1