一种基于谐波阻抗匹配的线性高效多合体功率放大器的制作方法

[0001]

本发明属于射频功率放大器领域,具体涉及一种适用于5g通信系统的线性高效对称型多合体(doherty)功率放大器。

背景技术:

[0002]

近年来,无线通信技术的迅速发展极大地推动了例如长期演进(long term evolution, lte)和全球微波互联接入(worldwide interoperability for microwave access, wimax)等调制信号的部署,这些信号一方面具有大容量信息传输能力,另一方面具有很高的峰值平均功率比(peak to average power ratio, papr),可达6-12db。而传统的a类或者ab类功率放大器输出功率达到饱和时,漏极效率也达到最大值,功率回退6db甚至更多时,功率放大器漏极效率大幅度降低,大部分都转化为热能散失,不仅造成能量的浪费,而且对整个通信系统的散热带来极大的负担,影响系统的性能,所以传统a类或者ab类功率放大器已经无法满足现代通信系统的要求。

[0003]

为了提高功率放大器在输出功率回退区内的效率,相关研究人员做了大量的工作,比如包络跟踪(envelope tracking,et)技术[1]-[6]、非线性元件实现线性放大(linear amplification with nonlinear components,linc)技术[7]-[12]和doherty 功率放大器技术[13]-[22]等,其中包络跟踪和非线性元件实现线性放大这两种技术需要额外的包络检波器、信号调制器等电路,成本以及设计难度都比较大,而doherty功率放大器结构简单、成本较低,被学术界和工业界认为是提高功率放大器在输出功率回退区域内效率的最有前景的方式,在即将到来的第五代通信技术(5g)中,doherty功率放大器有望成为最有价值的功放类型。

[0004]

对于功率放大器来说,其效率一直是研究者所关注并极力提升的指标,而国内外研究人员也在不断探索提升doherty功率放大器的峰值效率以及回退效率的技术,他们将高阶谐波控制的功放作为载波和峰值功率放大器,进一步提升doherty功率放大器的效率,通常是将载波功放和峰值功放设计为f类或者f-1

类来提升doherty功放的回退效率和峰值效率[23]-[25]。但f类/f-1

类功放设计复杂,线性度不高,严重影响doherty功放在低功率区域的线性度;另外,doherty功放结构中峰值功放偏置在c类,其固有缺点为饱和输出电流低,增益小,因此大多数高效doherty功放的负载调制较差,最终导致doherty功放性能不能达到最优。

[0005]

综上所述,要想进一步提高doherty功放的效率和线性度,就必须采用新型的线性高效子功放(即构成doherty功放的峰值/载波功放)进行doherty功放的设计,其中新型峰值功放和载波功放要求具有一致的饱和输出功率和饱和输出电流。

[0006]

参考文献[1] kim j., kim d., cho y., et al. highly efficient rf transmitter over broad average power range using multilevel envelope-tracking power amplifier[j]. ieee transactions on circuits and systems i, 2015, 62(6):1648

–

1657.

[2] jin q., ruan x., ren x., et al. step-wave switch capacitor converter for compact design of envelope tracking power supply[j]. ieee transactions on industrial electronics, 2017, 64(12):9587

–

9591.[3] tsai w. t., liou c. y., peng z. n., et al. wide-bandwidth and high-linearity envelope-tracking front-end module for lte-a carrier aggregation applications[j]. ieee transactions on microwave theory and techniques, 2017, 65(11):4657

–

4668.[4] ho c. y., lin s. m., meng c. h., et al. an 87.1% efficiency rf-pa envelope-tracking modulator for 80mhz lte-advanced transmitter and 31d bm pa output power for hpue in 0.153μm cmos [c]. ieee international solid-state circuits conference,2018: 432-434.[5] nomiyama t., youn y., choo y., et al. a 2tx supply modulatorfor envelope-tracking power amplifier supporting intra

-ꢀ

and inter-band uplink carrier aggregation and power class-2 high-power user equipment[c].ieee international solid-state circuits conference,2018: 434-436.[6] jing y., bakkaloglu b., a high slew-rate adaptive biasing hybrid envelope tracking supply modulator for lte applications[j]. ieee transactions on microwave theory and techniques, 2017, 65(9):3245

–

3256.[7] wang y., xie l. l., qiao s. s., a highly-linearity and high resolution all-digital phase modulatou with calibration algorithm for linc transmitters[c]. ieee international conference on solid-state and integrated circuit technolog, 2016: 120-122.[8] simoes a., castanheira m., gomes m., et al. ring-typemagnitude modulation for linc: a pragmatic approach to the efficiency challenge[j]. ieee transactions on communnications, 2017, 65(8): 3302-3315.[9] ryan l., jakabosky j., blunt s. d., et al. optimizing polyphase-coded fm waveforms within a linc transmit architectuer[c], ieee radar conference ,2014:0835-0839.[10] amiri o. t., koukab a., a 10w modified linc power amplifierwith a reduced-size chireixpower combiner[c]. ieee topical conference on power amplifier for wirelessand radio applications, 2014: 25-27.[11] hur j., kim h., woo s., et al. multi-level linc transmitter with nonisolated power combiner[j].electronics letters, 2013, 49(25):1624

–

1625.[12] mustafa a. k., ahmed s., faulkner m. bandwidth limitation for the constant envelope components of an ofdm signal in a linc architecture[j]. ieee transactions on circuits and systems i, 2013, 60(9):2502

–

2510.[13] hu y., boumziza s., doherty power amplifier distortion correction using an rf linearization amplifier[j]. ieee transactions on microwave theory and techniques, 2018, 66(5):2246

–

2257.

[14] nguyen d. p., pham t., pham a. v., a 28-ghz symmetrical doherty power amplifier using stacked-fet cells[j]. ieee transactions on microwave theory and techniques, 2018, 34(14):1

–

10.[15] yin y., xiong l., zhu y. t., et al. a compact dual-band digital doherty power amplifier using parallel combining transformer for cellular nb-lot applications[c]. ieee international solid-state circuits conference,2018: 408-410.[16] nguyen h. t., chi t. y., li s. s., et al. a 62-to-68ghz linear 6gb/s 64qam cmos doherty radiator with 27.5%/20.1% pae at peak/6d b-back-off output power leveraginghigh efficiency multi-feed antenna-based active load modulation[j]. ieee international solid-state circuits conference,2018: 402-404.[17] fang x. h., liu y. h., cheng k., two-way doherty power amplifier efficiency enhancement by incorporating transistors

’ꢀ

nonlinear phase distortion[j], ieee microwave and wireless components letters, 2018, 28(2):168-170.[18] zhou x. y., zheng s. y., chan w. s., et al. postmatching doherty power amplifier with extended back-off range based on self-generated harmonic injection [j]. ieee transactions on microwave theory and techniques, 2018, 66(4):1951-1963.[19] khan m. s., zhang h. y., wang x. l., et al. a novel two-stage broadband doherty power amplifier for wireless applications[j], ieee microwave and wireless components letters, 2018, 28(1):40-42.[20] rostomyan n., jayamon j. a., asbeck p. m., 15 ghz doherty power amplifier with rf predistortion linearizer in cmos soi[j], ieee transactions on microwave theory and techniques,2018,66(3):1339-1348.[21] rubio j., camarchia v., quaglia r., design of an 87% fractional bandwidth doherty power amplifier supported by a simplified bandwidth estimation method[j]. ieee transactions on microwave theory and techniques, 2018, 66(3):1319-1327.[22] lee h., lim w., bae j., et al. highly efficient fully integrated ga n-hemt doherty power amplifierbased on compact load network[j]. ieee transactions on microwave theory and techniques,2017,65(12):5203-5211.[23] joonhyung k . highly efficient asymmetric class-f/1/f gan doherty amplifier[j]. ieee transactions on microwave theory and techniques, 2018:1-8.[24] a. barakat, m. thian, and v. fusco,

ꢀ“

a high-efficiency gan doherty power amplifier with blended class-ef mode and load-pull technique,

”ꢀ

ieee trans. circuits syst., ii, exp. briefs, vol. 65, no. 2, pp. 151

–

155, feb. 2018.

[25] kim j . 2.4 ghz class-f-¹ꢀ

gan doherty amplifier with efficiency enhancement technique[j]. ieee microwave & wireless components letters, 2017, pp(99):1-3.[26] qi t , he s , you f , et al. canceling intermodulation products: a high-efficiency and linear-asymmetric doherty pa[j]. ieee microwave magazine, 2019, 20(1):98-103。

技术实现要素:

[0007]

针对现有技术存在的问题,本发明一种基于谐波阻抗匹配的线性高效多合体功率放大器,在传统doherty功放结构的基础上,通过利用简单的电路结构来匹配其子功放的输入/出基波电阻和谐波电阻,提高子功放的效率;并首次通过匹配峰值功放的输入/出基波阻抗、二次谐波阻抗以及三次谐波阻抗,提高峰值功放的饱和输出功率以及饱和输出电流,从而使得doherty功率放大器具有更优的负载调制;最后通过将载波功放偏置在ab类,保证doherty功放在低功率区域的线性度,同时选择合适的峰值功放栅极偏置电压,利用载波功放和峰值功放相互影响的作用,最终保证了doherty功放在高功率区域的线性度。

[0008]

一种基于谐波阻抗匹配的线性高效多合体功率放大器,功分器部分采用传统wilkinson功分器,结构简单。功分器两个输出端口一个连接主功放,另一个通过特性阻抗为50欧的1/4波长相位补偿传输线连接到辅功放。其中主功放偏置在ab类,保证doherty功放在低功率区域的线性度;辅功放偏置在c类,可以保证主/辅功放的相互调制;主/辅功放输出/入匹配网络中添加双l型谐波匹配结构,来匹配晶体管漏极输出/栅极输入端的二次谐波阻抗和三次谐波阻抗,之后采用一般的l型匹配电路匹配输出/入基波阻抗。主/辅功放输出匹配网络后添加相位偏移线,主功放后的相位偏移线用来调节主功放一路信号的相位,辅功放后的相位偏移线用来调节辅功放一路信号的相位,还能防止在低功率区域载波功放功率泄露到峰值功放的作用。主功放一路在偏移线后串接一条特性阻抗为50欧的1/4波长阻抗逆变传输线,起到阻抗逆变的作用,之后,主/辅功放两路连接到一点,在此称作合路点。最后,合路点后串接一条特性阻抗为35欧的1/4波长传输线的阻抗变换线,用来将50负载阻抗变换到25欧。

[0009]

一种基于谐波阻抗匹配的线性高效多合体功率放大器,具有以下几个优点:第一,采用基波阻抗、二次谐波阻抗以及三次谐波阻抗匹配的方法设计doherty功率放大器的子功放,电路设计简单,电路调试简便,且设计出的子功放效率高,载波功放线性度较好。

[0010]

第二,峰值功放采用基波阻抗、二次谐波阻抗以及三次谐波阻抗匹配的方法,提高其饱和输出功率以及饱和输出电流,较好的解决了doherty功放中峰值功放偏置在c类所产生的饱和输出电流以及饱和输出功率小的问题,解决了传统doherty功放负载调制不理想导致的峰值效率低,回退效率低以及回退范围小于理论6db的问题,提高了doherty功放的峰值效率、回退效率,扩大了回退范围。

[0011]

第三,本发明设计的doherty功放中载波功放为ab类,峰值功放为c类,通过采用本发明的输入/出网络,其在达到高效率同时,可以实现更好的线性度。

附图说明

[0012]

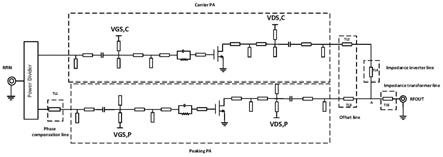

图1是(a)载波功放pae仿真结果图(b)载波功放de仿真结果图(c)载波功放imd3仿真结果图(d)载波功放imd5仿真结果图 ;图2是(a)峰值功放pae仿真结果图(b)峰值功放de仿真结果图;图3是(a)载波功放和峰值功放输出电流仿真结果图(b)dpa的de仿真结果图;图4是(a)dpa imd3仿真结果图(b)dpa imd5仿真结果图(c)峰值功放偏置在-4.5v情况下的dpa的de仿真结果图(d)峰值功放偏置在-4.5v情况下的dpa的pae仿真结果图;图5 是doherty功率放大器子功放电路原理图;图6 是doherty功率放大器整体电路原理图。

具体实施方式

[0013]

本专利提供了一种基于谐波匹配的线性高效doherty功率放大器电路结构。为了更清楚地阐述本发明的电路结构,下面结合电路原理图来进行详细说明。

[0014]

图5为doherty功放中载波功放和峰值功放所使用的电路原理图,在此说明载波功放和峰值功放采用相同的电路结构,故采用一个电路原理图同时阐述载波功放和峰值功放原理以及最佳实施方式。对于载波功放,其工作在ab类,通过匹配输入/出端的基波阻抗、二次谐波阻抗以及三次谐波阻抗,可以提升效率,且具有一定的线性度;对于峰值功放,其工作在c类,通过匹配输入/出端的基波阻抗、二次谐波阻抗以及三次谐波阻抗,可以提升效率,解决因偏置太低而带来饱和输出功率以及饱和输出电流低的问题。

[0015]

根据本发明的电路原理图,在设计载波功放和峰值功放时,只需调节如图5所示中传输线tl5、tl7、tl9、tl11就可进行栅极输入/漏极出端二次谐波以及三次谐波阻抗匹配。在如图5所示晶体管栅极输入端前的输入匹配网络中,传输线tl8用于焊接晶体管;电容c2和电阻r1组成用于稳定载波/峰值功放的稳定网络;传输线tl7和tl6组成输入二次谐波阻抗的匹配网络,其中tl7电长度为λ0/8,使得输入端的二次谐波在点b处形成短路,避免输入端二次谐波阻抗匹配网络影响其他阻抗匹配;传输线tl5和tl3组成输入三次谐波阻抗匹配网络,其中tl3电长度为λ0/12,使得输入端三次谐波在点a处形成短路,避免输入三次谐波阻抗匹配网络影响其他阻抗匹配;传输线tl4为偏置传输线,电长度为λ0/4;电容c1、传输线tl2和传输线tl1组成l型输入基波阻抗匹配网络,根据最优输入基波阻抗来调节它们的具体数值,达到最佳匹配效果。在如图1所示晶体管漏极输出端后的输出匹配网络中,传输线tl9用于焊接晶体管,同时和传输线tl10组成输出二次谐波阻抗的匹配网络,其中tl10电长度为λ0/8,使得输出二次谐波在点c处形成短路,避免输出二次谐波阻抗匹配网络影响其他阻抗匹配;传输线tl11和tl12组成输出三次谐波阻抗匹配网络,其中tl12电长度为λ0/12,使得输出三次谐波在点d处形成短路,避免三次谐波阻抗匹配网络影响其他阻抗匹配;传输

线tl13为偏置传输线,电长度为λ0/4;电容c3、传输线tl14和传输线tl15组成l型输出基波阻抗匹配网络,根据输出基波阻抗来调节它们的具体数值,达到最佳匹配效果。

[0016]

图6为doherty功放的整体电路原理图。本发明设计的doherty功放输入功率分配端采用均匀功率分配,可采用传统的wilkinson功分器。在本发明的doherty功放中,载波功放工作在ab类,峰值功放工作在c类,由于对两者的输入/出端进行基波阻抗、二次谐波阻抗以及三次谐波阻抗匹配,工作在c类的峰值功放与工作在ab类的载波功放的饱和输出功率以及饱和输出电流可达到一致,这使得doherty功放的负载调制更优,峰值效率以及回退效率更高,同时具有较高的线性度。在此需说明,载波功放与峰值功放偏置不同,其输入/出最优基波阻抗、二次谐波阻抗以及三次谐波阻抗会有所不同,因此载波功放与峰值功放的输出入/出匹配网络中的传输线长度需进行适当调节,以达到载波功放与峰值功放的最优性能。

[0017]

在图6中,doherty电路原理图上半部分为载波功放电路原理图,下半部分为峰值功放原理图,两者具体电路原理图最佳实施方式已通过图1进行详细介绍,在此不再赘述,只对doherty整体电路结构进行详细介绍。

[0018]

在图6doherty整体电路原理图中,输入端采用均匀功率分配,可采用传统的wilkinson功分器进行设计。在输出端,载波功放与峰值功放分别附有传输线tl2和传输线tl3,由于它们主要起到调节相位的作用,又可以称它们为偏移线。载波功放中输出端的偏移线tl2起到调节载波功放输出信号相位的作用,峰值功放中的偏移线tl3除了起到调节峰值功放输出信号相位的作用之外,还用于防止在低功率区域载波功放功率泄露到峰值功放。在图6中,载波/峰值功放合路点a处,载波功放偏移线tl2后,为传统doherty功放中使用的阻抗逆变线tl4,其电长度为λ0/4,特性阻抗为50欧,起到调节载波功放负载电阻的作用。载波功放合路点a与负载之间的传输线tl5为阻抗变换线,它将负载阻抗50欧变换为25欧,其电长度为λ0/4,特性阻抗为35欧。由于载波功放输出端使用了λ0/4阻抗逆变线,载波功放与峰值功放两路的相位产生了较大偏差,因此在峰值功放一路的输入端需增加一条电长度为λ0/4的传输线tl1,用于峰值功放一路的相位补偿,但本发明载波功放和峰值功放输入输出端不仅对基波阻抗进行匹配,还对二次谐波阻抗以及三次谐波阻抗进行匹配,且载波功放与峰值功放的输入/出匹配网络传输线总电长度不相同,载波功放与峰值功放上下两路并不是准确的90

°

相位差,所以这条相位补偿线tl1需要进行合适的调节,以达峰值功放一路的合适相位补偿,使得上下两路在合路点a处的相位一致。

[0019]

为了清楚的表明本专利结构的有益效果,针对5g所用频段3.5ghz设计了一款doherty功放,现使用此3.5ghz的doherty功放仿真结果进行说明所述有益效果:第一,图1(a)为偏置在ab类情况下的载波功放的pae仿真结果图,(b)为偏置在ab类情况下的载波功放的de仿真结果图。从仿真结果图中可以看出该载波功放的pae和de达到了和f类几乎一致的效果,pae和de分别为81.532%/85.813%。图1中(c)为偏置在ab类的载波功放在频率间隔为10mhz的情况下的imd3仿真结果图,(d)为相同情况下的imd5仿真结果图。图2(a)为偏置在c类的峰值功放的pae仿真结果图,(b)为偏置在c类的峰值功放的de仿真结果图。从仿真结果图中可以看出峰值功放的pae和de达到了和f类几乎一致的效果,pae和de分别为78.079%/85.391%。

[0020]

第二,从图1(a)和图2的(a)中可以看出载波功放的输出功率为39.836dbm,峰值功

放的输出功率为39.835dbm,两者的输出功率几乎一致。图3中的(a)为载波功放和峰值功放在合路点处的电流曲线图,可以看出,在输入功率为35dbm时,两者的饱和输出电流相等。图3(b)为doherty的效率曲线图,可以看出第一个峰值效率点在输出功率为36.5dbm时,de为75.32%;第二个峰值效率点在输出功率为43dbm时,de效率为86.15%;从图3中的(b)仿真结果可以看出,本设计发明的dpa回退范围为36.5dbm-43dbm,回退大约6.5db,明显优于传统dpa不大于6db的回退。

[0021]

第三,图4(a)和(b)分别为整体dpa在频率间隔为10mhz情况下的imd3和imd5的仿真结果,其中峰值功放栅极偏置调节为-4.5v。从仿真结果图中可以看出在输出功率小于37.969dbm,imd3在-30dbc以下;在输出功率小于41.112dbm时,imd4在-31.5dbc以下的;当满足imd3和imd4均小于-30dbc的情况下,即输出功率小于37.969dbm时,从图4(c)中可以看出doherty功放的de大约为66.191%,从图3(d)中可以看出doherty功放的pae大约为63.061%。根据参考文献[26]中所提及的综合衡量功放效率与线性度的因子fom计算公式(表示在imd3为-30dbc时,最大pae与中心频率的0.25次方的乘积)计算本设计fom=63.061*3.5^0.25=86.25,超出参考文献[26]中所给值75,以此来看本设计为高效线性doherty功放。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1