半导体设备的制作方法

半导体设备

1.相关申请的交叉引用

2.本申请要求于2019年10月15日提交的日本专利申请号2019-188734的优先权,其内容在此通过引用并入本申请。

技术领域

3.本发明涉及半导体系统。例如,本发明涉及一种半导体系统,其中数据在存储器和片上系统设备之间传输,存储器和片上系统设备中的每个由硅的单个芯片制成。

背景技术:

4.用在认知应用中的ai(人工智能)和片上系统设备(soc)需要在其上安装神经网络兼容功能(诸如大规模乘法累加(加法)计算电路),以同时处理大量数据。出于对大量数据重复写入/读取的必要性,需要高速的诸如神经网络的权重的信息、在宽带中具有大容量的存储器配置。此外,操作中的功率增加已经成为问题。因此,减少在存储器芯片或soc芯片中占用大量消耗电流的信号总线操作电流更加重要。

5.日本专利申请公开号2007-208616(专利文献1)描述了一种半导体系统,该半导体系统在使用多相时钟信号的情况下接收数据并且锁存该数据。

技术实现要素:

6.但是,在信号总线上流动的操作电流的减小和大量数据在数据传输时的正确获取方面,专利文献1中描述的半导体系统具有改进空间。

7.实施例的一个目的是通过减少半导体系统的消耗电流,来增强高速数据传输操作的可靠性。根据本说明书的描述和附图,其他目的和新颖特性将变得明显。

8.根据一个实施例的半导体系统包括:半导体设备,其具有形成在一个半导体芯片上的中央处理器单元和逻辑电路;以及形成在一个半导体芯片上的存储器设备,并且半导体设备和存储器设备中的每个包括驱动器电路和接收器电路。从驱动器电路输出:数据(其具有比被施加到驱动器电路的电源电压的振幅低的振幅)、第一时钟信号和第二时钟信号,第二时钟信号的相位从第一时钟信号移位预先确定量,并且,接收器电路与第一时钟信号的上升沿和第二时钟信号的上升沿同步地进行数据的输入。

9.在根据一个实施例的半导体系统中,可以减小信号总线上的操作电流,并且可以改进高速数据传输操作的可靠性。

附图说明

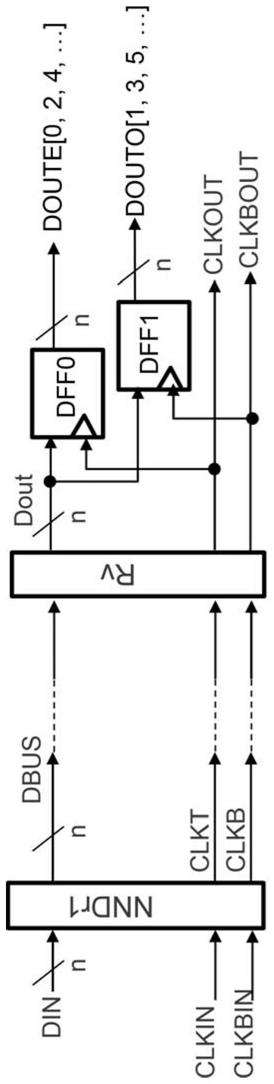

10.图1是第一实施例的数据传输图;

11.图2是通过利用第一实施例生成的信号的波形图;

12.图3是第二实施例的数据传输图;

13.图4是示出在使用四相时钟信号时所生成的数据传输波形的图;

14.图5是示出在第三实施例中通过使用低电压电源电路以低振幅进行信号传输的数据传输图;

15.图6是被施加低电压的低振幅驱动器电路的电路图;

16.图7是图6的低振幅驱动器电路的操作波形图;

17.图8是在第四实施例中将p型mosfet用于输出电路时所生成的数据传输图;

18.图9是使用p型mosfet的低振幅驱动器电路的输出电路图;

19.图10是图9的低振幅驱动器电路的操作波形图;

20.图11是第五实施例中图6和图9的驱动器电路的组合使用中的低振幅数据总线的图;

21.图12是示出在图11的低振幅数据总线中进行数据传输时的操作波形的图;

22.图13是低振幅驱动器电路nndr与ppdr之间的共用电源的配置图;

23.图14是示出低振幅驱动器电路nndr/低振幅接收器电路rv以及低振幅驱动器电路ppdr/低振幅接收器电路rv的组合使用的另一修改示例的图;

24.图15是示出低振幅驱动器电路nndr/低振幅接收器电路rv以及低振幅驱动器电路ppdr/低振幅接收器电路rv的组合使用的又一修改示例的图;

25.图16是示出低振幅驱动器电路nndr/低振幅接收器电路rv以及低振幅驱动器电路ppdr/低振幅接收器电路rv的组合使用的又一修改示例的图;

26.图17是示出低振幅驱动器电路nndr/低振幅接收器电路rv和低振幅驱动器电路ppdr/低振幅接收器电路rv的组合使用的又一修改示例的图;

27.图18是低振幅接收器电路的电路图;

28.图19是低振幅接收器电路的电路图;

29.图20是低振幅接收器电路的电路图;

30.图21是通过使用穿通电极被层叠的soc芯片的平面布局图;

31.图22是通过使用穿通电极被层叠的存储器芯片的平面布局图;

32.图23是通过使用导线被层叠的soc芯片的平面布局图;

33.图24是通过使用导线被层叠的存储器芯片的平面布局图;

34.图25是通过使用穿通电极被层叠的soc芯片和存储器芯片的层截面图;

35.图26是通过使用导线被层叠的soc芯片和存储器芯片的层截面图;

36.图27是使用低振幅驱动器电路进行数据传输的示意图;

37.图28是低振幅驱动器电路的电路图;

38.图29是示出低振幅驱动器电路与接收器电路之间的信号延迟的频率特性的图;

39.图30是示出低振幅驱动器电路中的操作波形对频率的依赖性的图;以及

40.图31是示出使用低振幅驱动器电路通过数据总线被输入到接收器电路的每个信号的波形的图。

具体实施例

41.在下文中,将参考附图详细说明根据一个实施例的半导体系统。注意,贯穿说明书和附图,相同的部件或对应的部件由相同的附图标记表示,并且将省略其重复说明。在附图中,为了便于说明,可以省略或简化配置。实施例和修改示例中的至少一些可以适当地彼此

组合。

42.(第一实施例)

43.《半导体系统的配置》

44.图25是使用穿通电极tsv(硅穿孔)的soc芯片和存储器芯片的层截面图。

45.附图标记“1”指示印刷板,附图标记“2”指示soc芯片,附图标记“3”指示存储器芯片,附图标记“4”指示用于连接每个芯片的电极和印制板的布线。如图25中所见,被定位在底层中的板1与顶层中的存储器芯片之间的soc芯片2和存储器芯片3通过竖直穿透芯片的布线4彼此连接。

46.图26是使用导线的soc芯片和存储器芯片的层截面图。

47.图26与图25的不同之处在于,板1、soc芯片2和存储器芯片3通过导线5彼此连接。

48.图21是通过使用穿通电极层叠的soc芯片的平面布局图。

49.soc芯片2包括中央处理器单元cpu、计算单元eu、输入/输出端口iou、布线区域“tsv”(其通过布线4连接到顶层中的存储器芯片和底层中的板)以及驱动器电路单元dru。

50.驱动器电路单元dru将从布线4接收的信号提供给中央处理器单元cpu、计算单元eu或输入/输出端口iou,并且将从中央处理器cpu、计算单元eu或输入/输出端口iou接收的信号提供给布线4。这里描述的信号是包括数据和地址和时钟信号的控制信号。

51.图22是通过使用穿通电极层叠的存储器芯片的平面布局图。

52.存储器芯片3包括存储器阵列ma、控制电路mcont(控制存储器阵列)、布线区域“tsv”(其通过布线4连接到顶层或底层中的芯片)以及驱动器电路单元dru。

53.驱动器电路单元dru将从布线4接收的信号提供给控制电路mcont,或者将从控制电路mcont接收的信号提供给布线4。这里描述的信号是包括数据和地址和时钟信号的控制信号。

54.控制电路mcont通过全局总线gbus连接到存储器阵列ma内部的局部总线lbus。

55.例如,图25和图26的存储器芯片3是同步dram,其与从soc芯片2提供的时钟信号同步地写入和读取数据。

56.图23是通过使用导线层叠的soc芯片的平面布局图。

57.soc芯片2包括导线键合区域“wpd1”和“wpd2”。soc芯片2和存储器芯片3在导线键合区域wpd1中通过导线彼此连接。soc芯片2在导线键合区域wpd1中通过导线连接到板1。

58.图24是通过使用导线层叠的存储器芯片的平面布局图。

59.存储器芯片3包括导线键合区域“wpd”。存储器芯片3在导线键合区域wpd中通过导线连接到顶层、底层或板。

60.<<驱动器电路单元的细节(比较示例)>>

61.图27是使用低振幅驱动器电路的数据传输的示意图。

62.低振幅驱动器电路nndr、低振幅接收器电路rv、锁存器电路dff0和dff1以及反相器电路inv被包括在图21、图22、图23和图24中所示的驱动器电路单元dru中。在一个示例中,图21中的soc芯片2通过穿通电极(布线区域tsv)将信号发送到图22的存储器芯片3,低振幅驱动器电路nndr被包括在soc芯片2内部的驱动器电路单元dru中,并且低振幅接收器电路rv等被包括在存储器芯片3内部的驱动器电路单元dru中。

63.在另一个示例中,图27中所示的配置不仅可适用于在芯片之间传输数据的这样的

电路,而且还可适用于在soc芯片2内部传输数据的电路或在存储器芯片3内部传输数据的电路。

64.低振幅驱动器电路nndr具有由n型mosfet制成的输出电路,接受n位(n位宽度)数据“din”的并行输入,并且将具有比数据din的电压振幅低的振幅的数据输出到n位数据总线dbus。低振幅驱动器电路nndr还接受时钟信号clkin的输入,并且将具有比时钟信号clkin的电压振幅低的振幅的时钟信号输出到时钟信号线clkt。

65.低振幅接收器电路rv接收从低振幅驱动器电路nndr输出的均具有较低振幅的时钟信号和数据。布置n位锁存器电路dff0和dff1,并且将由低振幅接收器电路rv接收的非反相时钟信号和n位数据dout并行地提供给锁存器电路dff0,同时将由反相器电路inv反相的反相时钟信号和n位dout并行地提供给锁存器电路dff1。

66.锁存器电路dff0与非反相时钟信号同步地锁存n位数据dout的偶数编号的数据“doute”(0、2、4

…

),并且并行地输出所锁存的n位数据。锁存器电路dff1与反相时钟信号同步地锁存n位数据dout的奇数编号的数据“douto”(1、3、5

…

),并且并行地输出所锁存的n位数据。

67.在以下附图中示出的符号“/n”意指存在与“n”位的数目相对应的信号线,使得n位数据被并行地传输。为了简化附图,图示的锁存n位数据的偶数编号的数据或奇数编号的数据的锁存器电路的数目仅为一个。然而,锁存器电路被布置成对应于“n”位的数目。

68.图28是低振幅驱动器电路的电路图。

69.用作操作电源的电源电压vdd和地电位vss被提供给低振幅驱动器电路nndr,并且低振幅驱动器电路从输入端子tin输入接受输入信号in的输入,并且从输出端子tout输出输出信号out。n型mosfet 1和2串联连接,电源电压vdd(例如,1.0v)被施加到n型mosfet 1的漏极,从中间端子tin将输入信号in提供给n型mosfet 1的栅极,并且n型mosfet 1的源极连接到输出端子tout。地电位vss(例如,0v)被施加到n型mosfet 2的源极,从输入端子tin将输入信号in的反相信号提供给n型mosfet 2的栅极,并且n型mosfet 2的漏极连接到输出端子tout。

70.当具有高电平的输入信号in被提供时,n型mosfet 1导通以输出,并且具有比电源电压vdd低n型mosfet 1的vth的电压的信号被输出,作为到输出端子tout的输出信号out。因此,当n型mosfet 1和mosfet 2被用于低振幅驱动器电路nndr时,要被输出的信号的振幅被减小,并且去往/来自负载电容的充电/放电电流被减小,充电/放电电流随着数据总线dbus的布线越长而越大,并且用于数据总线dbus的驱动电流可以被减小。

71.注意,输入信号in是图27中所示的数据din或时钟信号clkin。接收数据din的低振幅驱动器电路nndr被布置成对应于“n”位的数目。

72.图29是示出低振幅驱动器电路与接收器电路之间的信号延迟的频率特性的图。

73.横轴指示频率,并且纵轴指示延迟“tpd”。符号字符“re”指示关于信号的上升沿的频率的上升延迟的特性,并且符号字符“fe”指示关于信号的下降沿的频率的下降延迟的特性。尽管信号的上升沿的延迟时间是与频率无关的常数,但是信号的下降沿的下降延迟时间随着频率的升高而延迟更多。将参考图30进一步解释该现象。

74.图30是示出了低振幅驱动器电路的操作波形对频率的依赖性的图。

75.符号字符“vrcv”指示阈值,在该阈值处,低振幅驱动器电路的输出电压从低电平

改变为高电平(或从高电平改变为低电平)。当输出电位变高时,图28中所示的输出电路的n型mosfet 1的栅极-源极电压vg变小,并且输出电压的增加的性能在vdd-vth附近迅速降低。因此,当输出电压的输出处于高电平的时间较短时,高电平电压倾向于低,并且当输出电压的输出处于高电平的时间较长时,高电平电压倾向于高。因此,使输出电压下降的动作的开始电压不同,因此,从高电平到低电平改变所花费的时间的延迟改变(tpdf1<tpdf2<tpdf3)。

76.图31是示出使用低振幅驱动器电路通过数据总线输入到接收器电路的每个信号的波形的图。

77.低振幅驱动器电路nndr将时钟信号clkin输出到时钟信号线clkt,并且将n位数据din的偶数编号的数据和奇数编号的数据串行地输出到数据总线dbus,以使得首先输出偶数编号的数据,然后输出奇数编号的数据。根据从低振幅驱动器电路输出的数据和时钟信号,时钟信号线clkt和数据总线dbus的电位从地电位vss改变为vdd-vth,并且从vdd-vth改变为地电位vss。在这种情况下,在从低振幅驱动器电路输出的时钟信号(其引起从低振幅接收器电路rv输出的时钟信号clkout)中,上升沿延迟时间tpdr稳定,下降沿延迟时间tpdf改变(如图29中所示)。

78.在根据时钟信号写入和读取数据的系统中,当使用由长布线制成的总线来传输数据时,时钟信号的边沿延迟的改变会不利地缩小数据窗口,数据窗口用于正确地在数据接收侧(即锁存器电路dff0和dff1)获取数据。此外,数据获取时间变化,并且因此,高速操作性能不利地显著劣化。

79.<<(第一实施例的)驱动器电路单元的细节>>

80.图1是第一实施例的数据传输图。在图1中,使用了输出两相时钟信号的低振幅驱动器电路。与图28的情况类似,n型mosfet用于低振幅驱动器电路的输出电路。

81.低振幅驱动器电路nndr1被布置成接受n位数据din的并行输入,并且将具有比数据din的电压振幅低的振幅的数据并行地输出到数据总线dbus。此外,低振幅驱动器电路nndr1接受非反相时钟信号clkin和反相时钟信号clkbin的输入,并且将具有比非反相时钟信号clkin的电压振幅低的振幅的时钟信号输出到时钟信号线clkt,并且将具有比反相时钟信号clkbin的电压振幅低的振幅的时钟信号输出到非反相时钟信号线clkb。

82.低振幅接收器电路rv并行地接收n位数据,n位数据具有从低振幅驱动器电路nndr1输出的低振幅,并且接收非反相时钟信号和反相时钟信号。由低振幅接收器电路rv接收的非反相时钟信号和数据dout被提供给锁存器电路dff0,并且由低振幅接收器电路rv接收的反相时钟信号和数据dout被提供给锁存器电路dff1。

83.锁存器电路dff0与非反相时钟信号的上升沿同步地锁存数据dout的偶数编号的数据doute(0、2、4

…

),并且输出所锁存的数据。锁存器电路dff1与反相时钟信号的上升沿同步地锁存数据dout的奇数编号的数据douto(1、3、5

…

),并且输出所锁存的数据。

84.低振幅驱动器电路nndr1和低振幅接收器电路rv被包括在图21、图22、图23和图24中所示的驱动器电路单元dru中。

85.图2是使用第一实施例的信号的波形图。

86.由锁存器电路dff0锁存由低振幅接收器电路rv已经首先接收的偶数编号的数据dout(0),以便与由低振幅接收器电路rv已经接收的非反相时钟信号clkout的上升沿同步。

接下来,由锁存器电路dff1锁存由低振幅接收器电路rv已经首先接收的奇数编号的数据dout(1),以便与由低振幅接收器电路rv已经接收的反相时钟信号clkbout的上升沿同步。如上所述,随后,偶数编号的数据dout在被锁存器电路dff0锁存之后被输出,以便与非反相时钟信号clkout的上升沿同步,并且奇数编号的数据dout在被锁存器电路dff1锁存之后被输出,以便与反相时钟信号clkbout的上升沿同步。

87.通过使用这种方法,锁存器电路dff0和dff1都可以与时钟信号(clkout和clkbout)的上升沿同步地锁存数据,这与图27的情况不同。以该方式,与图27的情况相比,用于正确地获取数据的数据窗口可以被扩展。此外,可以抑制数据获取时间的变化。结果,可以改善高速数据传输操作的可靠性。更进一步地,由于使用了具有低振幅的信号,所以可以减小信号总线上的操作电流。

88.(第二实施例)

89.<<(第二实施例的)驱动器电路单元的细节>>

90.图3是第二实施例的数据传输图。在图3中,在使用四相时钟信号的情况下传输数据。

91.输出接口电路oif包括数据锁存器电路dlt0、四相时钟生成电路cgen和低振幅驱动器电路nndr2,并且n位数据din和时钟信号clkin被提供给该电路。

92.数据锁存器电路dlt0包括锁存器电路dff00和dff01。四相时钟生成电路cgen包括锁存器电路dff02至dff05。低振幅驱动器电路nndr2包括输出电路oc0至oc5,并且输出电路oc0和oc1被布置成对应于“n”位的数目,以便并行地输入和输出n位数据。

93.输出电路oc0至oc5中的每个具有图28中所示的电路配置,并且输出具有比输入信号的电压振幅低n型mosfet 1的vth的振幅的信号。

94.非反相时钟信号被提供给锁存器电路dff00、dff02和dff04,并且反相时钟信号被提供给锁存器电路dff01、dff03和dff05。

95.锁存器电路dff00与非反相时钟信号同步地锁存偶数编号的数据din(0、2、4

…

),并且将所锁存的数据输出到输出电路oc0。锁存器电路dff01与反相时钟信号同步地锁存奇数编号的数据din(1、3、5

…

),并且将所锁存的数据输出到输出电路oc1。

96.锁存器电路dff02和dff03的输出信号被反馈到这些相应的锁存器电路的输入,此外,由反相器电路反相的信号被输入到这些锁存器电路。锁存器电路dff02的输出信号被反馈到锁存器电路dff04,作为其输入信号。锁存器电路dff03的输出信号被反馈到锁存器电路dff05,作为其输入信号。

97.锁存器电路dff02输出时钟信号clk0,并且锁存器电路dff03输出时钟信号clk1,时钟信号clk1的相位从时钟信号clk0的相位移位90

°

。锁存器电路dff04输出时钟信号clk2,时钟信号clk2的相位从时钟信号clk0的相位移动180

°

,并且锁存器电路dff05输出时钟信号clk3,时钟信号clk3的相位从时钟信号clk0的相位移动270

°

。

98.低振幅驱动器电路nndr2将偶数编号的数据de(0、2、4

…

)输出到具有“n”位宽度的偶数编号的数据总线bbuse,并且将奇数编号的数据do(1、3、5

…

)输出到具有“n”位宽度的奇数编号的数据总线bbuso。低振幅驱动器电路nndr2将时钟信号clk0至clk3输出到时钟信号线clkl。

99.输入接口电路iif包括数据锁存器电路dlt1、时钟恢复电路crc和低振幅接收器电

路rv,并且来自偶数编号的数据总线bbuse、奇数编号的数据总线bbuso和时钟信号线clkl的每个信号被提供给该输入接口电路。

100.低振幅接收器电路rv包括输入电路ic0至ic5。输入电路ic0将偶数编号的数据输出到数据锁存器电路dlt1,并且输入电路ic1将奇数编号的数据输出到数据锁存器电路dlt1。输入电路ic2至ic5中的每个将每个时钟信号输出到时钟恢复电路crc。

101.输入电路ic0和ic1被布置成对应于“n”位的数目,以便并行地输入和输出n位数据。

102.时钟恢复电路crc由多个nand逻辑电路制成,并且从输入的四相时钟信号生成两相时钟信号,该两相时钟信号由时钟信号clkout和时钟信号clkbout制成,时钟信号clkbout是时钟信号clkout的反相信号,并且将该两相时钟信号输出。

103.数据锁存器电路dlt1包括锁存器电路dff10和dff11。锁存器电路dff10与时钟信号clkout的上升沿同步地锁存偶数编号的数据,并且输出所锁存的数据。锁存器电路dff11与时钟信号clkbout的上升沿同步地锁存奇数编号的数据,并且输出所锁存的数据。

104.图3中所示的每个电路被包括在图21、图22、图23和图24中所示的驱动器电路单元dru中。

105.图4是示出当使用四相时钟信号时获得的数据传输的波形的图。

106.通过四相时钟生成电路cgen,从时钟信号clkin生成四相时钟信号clk0至clk3。

107.通过偶数编号的数据总线bbuse将偶数编号的数据de提供给输入接口电路iif,并且通过奇数编号的数据总线bbuso将奇数编号的数据do提供给输入接口电路iif。

108.已经通过偶数编号的数据总线bbuse和奇数编号的数据总线bbuso提供的数据de和数据do,由锁存器电路dff10和dff11与两相时钟信号clkout和clkbout的相应的上升沿同步地顺序锁存,该两相时钟信号clkout和clkbout已经从四相时钟信号clk0至clk3恢复。

109.在该数据传输方法中,分配了在总线驱动中的峰值电流,并且减小了电源噪声,并且因此,改善了由于电源噪声引起的高频传输特性的劣化。

110.(第三实施例)

111.<<(第三实施例的)驱动器电路单元的细节>>

112.图5是示出在第三实施例中使用低电压电源电路以低振幅进行信号传输的数据传输图。电源电压vdd(例如1.0v)被施加到低电压电源电路vddg_gen,以便生成低电压vddg(例如0.5v)。低电压vddg被提供给低振幅驱动器电路nndr3和低振幅接收器电路rv1。

113.低振幅驱动器电路nndr3、低振幅接收器电路rv1和低电压电源电路vdd_gen被包括在图21、图22、图23和图24中所示的驱动器电路单元dru中。

114.图6示出了向其施加了低电压的低振幅驱动器电路的电路图。已经从低电压电源vddg_gen生成的低电压vddg被提供给n型mosfet 1的漏极。当从输入端子tin提供具有高电平的输入信号in时,n型mosfet 1的栅极节点a的电平变为高电平,并且n型mosfet 2的栅极节点b的电平变为低电平。在该情况下,n型mosfet 1导通,因此,比图28的情况下的电压低的低电压vddg(诸如,比电源电压vdd低n型mosfet 1的vth的电压)被输出到输出端子tout。

115.输入信号in是图5中所示的数据din或时钟信号clkin和clkbin。

116.图7是示出图6的低振幅驱动器电路的操作波形的图。

117.当低振幅驱动器电路nndr3的输入信号in的电平从低电平(vss)变为高电平(vdd)

时,n型mosfet 1的栅极电位a的电平变为高电平(vdd),以将n型mosfet 1导通,并且n型mosfet 2的栅极电位b的电平变为低电平(vss),以将n型mosfet 2关断。在该情况下,低电压vddg通过n型mosfet 1被输出到输出端子tout,作为输出信号out。

118.当低振幅驱动器电路nndr3的输入信号in的电平从高电平(vdd)变为低电平(vss)时,n型mosfet 1的栅极电位a的电平变为低电平(vss),以将n型mosfet 1关断,并且n型mosfet2的栅极电位b的电平变为高电平(vdd),以将n型mosfet 2导通。在该情况下,地电位vss被输出到输出端子tout,作为输出信号out。

119.如上所述,当低振幅驱动器电路nndr3输出高电平信号时,输出信号out的电平变为低于“vdd-vth”的低电压vddg。以该方式,可以防止输出信号out的电压增加,直到低振幅驱动器电路nndr3(n型mosfet 1)几乎关断为止,并且因此,低振幅驱动器电路nndr3的高电平对输出速率的依赖性(诸如,循环依赖性)的变化的原因可以减少。

120.此外,可以通过低电压vddg来降低总线信号系统的信号振幅,并且因此,可以获得更大的功率降低效果。

121.(第四实施例)

122.<<(第四实施例的)驱动器电路单元的细节>>

123.图8是在第四实施例中,当将p型mosfet用于输出电路时获得的数据传输图。

124.向低振幅驱动器电路ppdr和低振幅接收器电路rv施加电源电压vdd和低电压vddg(0.5v),作为相应的操作电压。低电压vddg由连接到地电位vss的低电压生成电路vddg2_gen生成。

125.低振幅驱动器电路ppdr、低振幅接收器电路rv和低电压电源电路vdd2_gen被包括在图21、图22、图23和图24中所示的驱动器电路单元dru中。

126.图9是使用p型mosfet的低振幅驱动器电路的输出电路图。

127.在电源电压vdd和低电压vddg被提供给其作为操作电源时,低振幅驱动器电路ppdr从输入端子tin接受输入信号in的输入,并且从输出端子tout输出输出信号out。

128.p型mosfet 1和2彼此串联连接,电源电压vdd(1.0v)被施加到p型mosfet 1的源极,来自输入端子tin的输入信号in被提供给其栅极,并且其漏极连接到输出端子tout。vddg被施加到p型mosfet 2的漏极,来自输入端子tin的输入信号in的反相信号被提供给其栅极,并且其源极连接到输出端子tout。

129.当提供具有高电平的输入信号in时,p型mosfet 1导通,以使得低电压vdd的信号被输出到输出端子tout,作为输出信号out。

130.当提供具有低电平的输入信号in时,p型mosfet 2导通,以使得低电压vddg被输出到输出端子tout,作为输出信号out。

131.换句话说,由p型mosfet制成的输出电路的输出电压具有在电源电压vdd和低电压vddg之间摆动的振幅。以该方式,与使用n型mosfet的低振幅驱动器电路的输出电路类似,减小了要被输出的信号振幅。因此,随着数据总线dbus的布线变长,负载电容上的增加的充电/放电电流变低,以使得可以减小数据总线dbus的驱动电流。

132.输入信号in是数据din或时钟信号clkin和clkbin。

133.图10是图9的低振幅驱动器电路的操作波形图。

134.输入信号in的电平从低电平(vss)变为高电平(vdd),p型mosfet 1的栅极的电位a

的电平变为低电平(vss),以将p型mosfet 1导通,并且p型mosfet 2的栅极的电位b的电平变为高电平(vdd),以将p型mosfet 2关断。这时,通过p型mosfet1,输出端子tout的输出信号out的电压从低电压vddg变为电源电压vdd。

135.输入信号in的电平从高电平(vdd)变为低电平(vss),p型mosfet 1的栅极的电位a的电平变为高电平(vdd),以将p型mosfet 1关断,并且p型mosfet 2的栅极的电位b的电平变为低电平(vss),以将p型mosfet 2导通。这时,低电压vddg被输出到输出端子tout,作为输出信号out。

136.如上所述,当输出电压的低电平增加pmos的vth时,要在长布线上传输的信号的振幅降低。

137.使用p型mosfet的低振幅驱动器电路的输出电路的操作波形是通过将使用n型mosfet的低振幅驱动器电路的输出电路的高电平和低电平之间的电压关系反转而获得的波形。换句话说,在使用p型mosfet的低振幅驱动器电路中,时钟信号的下降沿的使用是用于改进高速操作的准确性的对策。

138.当低电压vddg高于p型mosfet的阈值vth时,可以用作低功率数据传输电路,该电路例如可以有效防止噪声从公共gnd电源传播到邻近的模拟电路等。

139.(第五实施例)

140.图11是在第五实施例中图6和图9的驱动器电路的组合使用中的低振幅数据总线的图。

141.图11示出了在长布线上传输具有低振幅的信号的情况下的配置,该配置在低振幅驱动器电路nndr3(使用n型mosfet)和低振幅驱动器电路ppdr(使用p型mosfet)的组合使用中,其用作中继器(被布置在布线的中间)之前和之后的低振幅驱动系统。

142.低振幅驱动器电路nndr3的操作电源是低电压vddg和地电压vss,并且低振幅驱动器电路ppdr的操作电源是电源电压vdd和低电压vddg。低电压vddg由内部电源生成电路生成,并且被设置成电源电压vdd的约1/2倍,作为低振幅驱动器电路nndr3和ppdr之间的公共电源电位。

143.图11中所示的每个电路被包括在图21、图22、图23和图24中所示的驱动器电路单元dru中。

144.图12是示出在图11的低振幅数据总线中进行数据传输时的操作波形的图。

145.从图12可以看出,非反相时钟信号clkt_nn的上升沿和反相时钟信号clkb_nn的上升沿在低振幅驱动器电路nndr3中被同步,并且非反相时钟信号clkt_pp的下降沿和反相时钟信号clkb_pp的下降沿在低振幅驱动器电路ppdr中被同步。因此,与时钟信号同步的信号的传输和锁存的准确度被改善。

146.图13是低振幅驱动器电路nndr3和ppdr之间的公共电源的配置图。

147.由于低电压vddg通过电源线vddgl被共同提供给低振幅驱动器电路nndr3和ppdr作为其操作电源(如图11中所示),因此低振幅驱动器电路ppdr的放电电流(iout0)流到电源线vddgl中,但同时也作为充电电流(iout1)在低振幅驱动器电路nndr3的驱动器电路侧上流出,并且因此,产生了电荷再使用效果。因此,可以预期将消耗功率显著降低至第一至第四实施例的约1/2倍的效果。

148.低振幅驱动器电路nndr3、低振幅驱动器电路ppdr和低电压电源电路vdd_gen被包

括在图21、图22、图23和图24中所示的驱动器电路单元dru中。

149.图14至图17中的每个是示出了低振幅驱动器电路nndr/低振幅接收器电路nnrv以及低振幅驱动器电路ppdr/低振幅接收器电路pprv的组合使用中的另一个修改示例的图。

150.图14至图16的低振幅驱动器电路nndr、低振幅接收器电路nnrv、低振幅驱动器电路ppdr和低振幅接收器电路pprv被包括在图21、图22、图23和图24中的驱动器电路单元dru中。图17的低振幅驱动器电路nndr被包括在图22和图24中所示的驱动器电路单元dru中,并且低振幅驱动器电路ppdr被包括在存储器阵列ma中。

151.图14示出了第一修改示例。图14示出了将n位数据划分为奇数编号的数据和偶数编号的数据的两组的情况的示例。

152.奇数编号的数据din1和奇数编号的数据的时钟信号clk1被低振幅驱动器电路ppdr(包括由p型mosfet制成的输出电路)输出到奇数编号的数据的总线obus上,并且被带到低振幅接收器电路pprv(包括由p型mosfet制成的输出电路)中。

153.偶数编号的数据din0和偶数编号的数据的时钟信号clk0被低振幅驱动器电路nndr(包括由n型mosfet制成的输出电路)输出到偶数编号的数据的总线ebus上,并且被带到低振幅接收器电路nnrv(包括由n型mosfet制成的输出电路)中。

154.图15示出了第二修改示例。图15示出了基于信号传输方向(目的)将n位数据划分为两组的情况的示例。

155.写入数据wdin和写入数据时钟信号wclk被低振幅驱动器电路ppdr(包括由p型mosfet制成的输出电路)输出到写入数据总线wbus上,并且被带到低振幅接收器电路pprv(包括由p型mosfet制成的输出电路)中。

156.读取数据rdout和读取数据时钟信号rclk被低振幅驱动器电路nndr(包括由n型mosfet制成的输出电路)输出到读取数据总线rbus上,并且被带到低振幅接收器电路nnrv(包括由n型mosfet制成的输出电路)中。

157.图16示出了第三修改示例。图16示出了基于操作频率将n位数据划分为两组的情况的示例。

158.低频时钟信号lclk和指令inst被低振幅驱动器电路ppdr(包括由p型mosfet制成的输出电路)接收,并且被输出到指令总线ibus。

159.高频时钟信号hclk和数据data被低振幅驱动器电路nndr(包括由n型mosfet制成的输出电路)接收,并且被输出到数据总线dbus。

160.低频时钟信号的频率是几百mhz(例如200mhz),并且高频时钟信号的频率是几ghz(例如1ghz以上)。

161.图17示出了第四修改示例。图17示出了基于例如存储器中的分层总线系统将n位数据划分为两组的情况的示例。

162.已经通过全局总线gbus被输入的数据din被低振幅驱动器电路nndr(包括由n型mosfet制成的输出电路)接收,并且被输出到局部总线lbus。

163.已经通过局部总线lbus被输入的数据din被低振幅驱动器电路ppdr(包括由p型mosfet制成的输出电路)接收,并且被输出到局部总线lbus。

164.例如,全局总线gbus由诸如铝的金属材料制成,并且局部总线lbus由与金属材料不同的材料的硅制成。

165.图18至图20中的每个是低振幅接收器电路的电路图。

166.图18示出了普通的电平移位器电路。该电路被提供有电源电压vdd和地电位vss作为其操作电压,并且接收低电压vddg作为低于电源电压vdd的输入信号in。输入信号in是数据或时钟信号,并且具有比输入信号in的电压振幅大的电压振幅的数据和时钟信号被输出,作为输出信号out。

167.图19示出具有图18的进一步改进的性能的第一接收器电路,并且图20示出了具有图18的进一步改进的性能的第二接收器电路。

168.当高速接收器电路(在低振幅接收器电路nnrv或pprv的内部连接点c或d处,均具有积极改进的pmos或nmos的性能比)被用作低振幅接收器电路nnrv和pprv时,由于低振幅引起的信号传播延迟得到改进。这也意味着接收器电路的输出波形变得更尖锐,这引起接收器电路中所生成的h/l数据差异的改善。因此,可以全面改进控制时钟传输的变化准确性和数据传输中的数据获取准确性。

169.对实施例的说明已经描述了数据和时钟信号以低振幅被传输。然而,不仅数据和时钟信号,而且未说明的地址信号和控制信号(诸如ras和cas)也以低振幅被传输。

170.以上,基于实施例描述了本发明。然而,无需多言,本发明不限于前述实施例的配置,并且包括可以由本领域技术人员在本发明的范围内进行的各种修改和改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1