电路装置和实时时钟装置的制作方法

1.本发明涉及电路装置和实时时钟装置等。

背景技术:

2.已知有在电路接通电源时或电源电压下降时,产生电路的内部复位信号的上电复位电路。在专利文献1中,公开了在具有非接触接口和接触接口的组合型ic卡中,根据从外部供给的外部复位信号使内部复位信号的阈值变化的上电复位电路。

3.专利文献1:日本特开2009-123168号公报

4.专利文献1中记载的上电复位电路通过比较将电源电压分压后的电压和由调节器生成的基准电压,生成内部复位信号。

5.在初始电源接通时,存在例如基准电压的上升沿不追随电源电压等、生成基准电压的调节器的性能不稳定的情况。起因于这样的调节器的不稳定的性能,上电复位电路有可能以不希望的电压解除了复位。

技术实现要素:

6.本公开的一个方式涉及一种电路装置,其包含:比较器,其对根据电源电压生成的监视对象电压和基准电压进行比较,由此输出上电复位信号;基准电压生成电路,其生成所述基准电压,并将所述基准电压输出到基准电压节点;以及连接控制电路,其连接在被供给所述电源电压的电源电压节点与所述基准电压节点之间,所述连接控制电路在接通所述电源电压后的规定期间,将所述基准电压节点和所述电源电压节点连接。

7.另外,本发明的另一方式涉及一种实时时钟装置,其包含:以上记载的电路装置;以及振子,所述电路装置包含:调节器,其在将所述电源电压设为第一电源电压时,根据所述第一电源电压生成作为所述监视对象电压的第二电源电压;处理电路,其根据所述第二电源电压进行动作,通过所述上电复位信号进行复位和复位解除;以及振荡电路,其使所述振子进行振荡,由此生成时钟信号,所述处理电路包含计时电路,该计时电路根据所述时钟信号进行计时处理。

附图说明

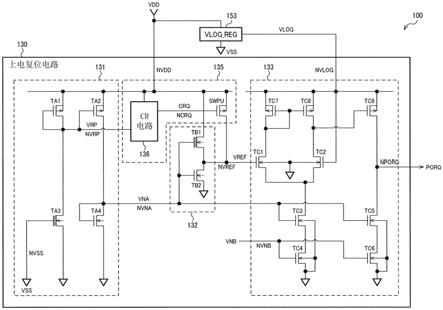

8.图1是上电复位电路和电路装置的基本结构例。

9.图2是说明基本结构例中的上电复位电路的第一动作的波形图。

10.图3是说明基本结构例中的上电复位电路的第二动作的波形图。

11.图4是上电复位电路和电路装置的结构例。

12.图5是cr电路的详细结构例。

13.图6是说明cr电路和开关的动作的波形图。

14.图7是说明上电复位电路的动作的波形图。

15.图8是实时时钟装置的结构例、以及实时时钟装置所包含的电路装置的结构例。

16.图9是电源电路的详细结构例。

17.标号说明

18.10:振子;100:电路装置;110:电源电路;114:开关控制电路;115:第一检测电路;116:第二检测电路;120:处理电路;121:计时电路;122:温度补偿电路;130:上电复位电路;131:偏置电路;132:基准电压生成电路;133:比较器;135:连接控制电路;136:cr电路;150:振荡电路;151~153:调节器;160:温度检测电路;170:接口电路;200:实时时钟装置;ce:电容器;crq:控制信号;ie1:第一反相器;ie2:第二反相器;nvdd:电源电压节点;nvref:基准电压节点;nvss:地节点;porq:上电复位信号;swpu:开关;tb1:耗尽型的n型晶体管;tb2:增强型的n型晶体管;te1:第一p型晶体管;te2:第二p型晶体管;te3:n型晶体管;vbat:电池电压;vdd:电源电压;vlog:电源电压;vref:基准电压;vss:地电压;vof:偏移电压。

具体实施方式

19.下面,对本公开的优选实施方式进行详细说明。另外,以下说明的本实施方式并非对权利要求书中记载的内容进行不当的限定,在本实施方式中说明的结构不一定全部是必需结构要件。

20.1.基本结构例

21.首先,说明上电复位电路130的基本结构例及其课题,然后,在图4以后说明本实施方式的上电复位电路130的结构例。但是,基本结构例具有与图4的结构例相同的结构要素,关于该结构要素,起到与图4的结构例同样的作用效果。关于这一点,在图4以后进行说明。

22.图1是上电复位电路130和电路装置100的基本结构例。电路装置100包含上电复位电路130和调节器153。上电复位电路130包含偏置电路131、基准电压生成电路132和比较器133。

23.电源电压vdd被提供给偏置电路131。偏置电路131基于电源电压vdd生成偏置电压vna,并将该偏置电压vna输出到基准电压生成电路132和比较器133。从电路装置100的外部供给电源电压vdd。

24.电源电压vlog被提供给基准电压生成电路132。基准电压生成电路132基于电源电压vlog生成基准电压vref,并将基准电压vref输出到比较器133。电源电压vlog是电路装置100的内部电源电压,调节器153根据电源电压vdd生成电源电压vlog。

25.电源电压vlog被提供给比较器133。比较器133比较作为监视对象电压的电源电压vlog和基准电压vref,并将其结果作为上电复位信号porq输出。监视对象电压是指上电复位电路130为了判断复位和复位解除的切换而作为监视对象的电压。比较器133在电源电压vlog比判定电压vref+vof低时,输出表示复位的上电复位信号porq,在监视对象电压比判定电压vref+vof高时,输出表示复位解除的上电复位信号porq。vof是比较器133的输入偏移。即,vof是输入监视对象电压和基准电压vref的差动对的偏移电压。另外以下,设表示复位的上电复位信号porq为低电平,表示复位解除的上电复位信号porq为高电平。

26.图2是说明图1的上电复位电路130的第一动作的波形图。在图2中,假设电源电压vdd以比较缓慢的时间变化上升的情况。

27.vtlg是被输入上电复位信号porq的逻辑电路的逻辑阈值电压。即,当比较器133的电源电压vlog比逻辑阈值电压vtlg低时,对逻辑电路而言,上电复位信号porq的逻辑电平

是不确定的。在电源电压vlog为逻辑阈值电压vtlg以上时,对于逻辑电路而言,上电复位信号porq的逻辑电平确定为低电平或高电平。

28.设定基准电压vref和偏移电压vof,使得基准电压vref收敛到规定电压后的判定电压vref+vof比阈值电压vtlg高。

29.在电路装置100被接通电源电压vdd后,调节器153生成的电源电压vlog追随电源电压vdd而上升。在电源电压vdd以相对缓和的时间变化上升的情况下,基准电压vref追随电源电压vlog而上升。因此,电源电压vlog和基准电压vref成为大致相同的电压并上升,在电源电压vlog比判定电压vref+vof低的状态下超过逻辑阈值电压vtlg。设该时刻为t1,在时刻t1之前,上电复位信号porq的逻辑电平不确定,在时刻t1,上电复位信号porq的逻辑电平确定为低电平。另外,在图2中用“x”表示不确定。

30.基准电压vref收敛到规定电压,然后电源电压vlog超过判定电压vref+vof。设该时刻为t2,在时刻t2,上电复位信号porq的电压从地电压vss变化为电源电压vlog,其逻辑电平从低电平变化为高电平。即,在时刻t2,上电复位电路130输出表示复位解除的上电复位信号porq。

31.在以上的第一动作中,在从时刻t1到t2的期间,输出表示复位的上电复位信号porq后,在时刻t2输出表示复位解除的上电复位信号porq。由此,被输入上电复位信号porq的电路被正常地被复位和解除复位。

32.图3是说明图1的上电复位电路130的第二动作的波形图。在图3中,假设电源电压vdd以比较急剧的时间变化上升的情况。

33.在电路装置100被接通电源电压vdd后,调节器153生成的电源电压vlog追随电源电压vdd而上升。在电源电压vdd以比较急剧的时间变化上升的情况下,基准电压vref不追随电源电压vlog。基准电压vref上升的速度由流过基准电压生成电路132的电流等决定。当电源电压vdd的上升速度比基准电压vref的上升速度快时,基准电压vref不追随电源电压vlog。例如,当减小流向基准电压生成电路132的电流以降低功耗时,容易产生基准电压vref不追随电源电压vlog的状态。

34.由于电源电压vlog追随电源电压vdd,而基准电压vref不追随电源电压vdd,所以在电源电压vlog超过逻辑阈值电压vtlg之前,电源电压vlog超过判定电压vref+vof。在电源电压vlog超过逻辑阈值电压vtlg的时刻t1,上电复位信号porq的逻辑电平确定,但在之前的时刻t2,电源电压vlog超过判定电压vref+vof,所以在时刻t1,上电复位信号porq的逻辑电平确定为高电平。

35.第二动作中,在时刻t2,在上电复位电路130的内部判定为复位解除,但此时的基准电压vref不收敛于规定电压,判定电压vref+vof没有成为本来希望的电压。因此,未输出表示复位的上电复位信号porq,而在时刻t1输出表示复位解除的上电复位信号porq,被输入上电复位信号porq的电路不能正常复位。

36.如上所述,根据接通电源电压时的电源电压vdd、电源电压vlog以及基准电压vref的上升波形、时间变化的特性或者电压条件,有可能尽管监视对象电压没有超过希望的判定电压,上电复位电路130也解除复位。如上所述,在专利文献1等现有技术中也产生同样的问题。

37.2.结构例

38.图4是本实施方式中的上电复位电路130和电路装置100的结构例。图4的上电复位电路130包含偏置电路131、基准电压生成电路132、比较器133和连接控制电路135。另外,对与在图1中说明的结构要素相同的结构要素赋予相同的标号,对于关于该结构要素已经说明的内容,适当省略其说明。

39.比较器133通过比较根据电源电压vdd生成的监视对象电压和基准电压vref,输出上电复位信号porq。基准电压生成电路132生成基准电压vref,并将该基准电压vref输出到基准电压节点nvref。连接控制电路135连接在输入电源电压vdd的电源电压节点nvdd和基准电压节点nvref之间。连接控制电路135在电源电压vdd接通后的规定期间,将基准电压节点nvref和电源电压节点nvdd连接。

40.在图4中,监控对象电压是由调节器153根据电源电压vdd生成的电源电压vlog。但是,监视对象电压不限于电源电压vlog,只要是通过某些电压生成电路根据电源电压vdd生成的电压即可。另外,规定期间的长度可以是任意的,例如只要规定期间比接通电源电压vdd后基准电压vref收敛到规定电压的时间长即可。或者,规定期间比在接通电源电压vdd后监视对象电压超过逻辑阈值电压vtlg的时间长即可。在接通电源电压vdd后,基准电压vref收敛到规定电压的时间、以及监视对象电压超过逻辑阈值电压vtlg的时间根据电源电压vdd的上升波形等而变动,因此,例如只要设定针对该变动具有余量的长度的规定期间即可。

41.根据本实施方式,在电路装置100接通电源电压vdd后的规定期间,连接控制电路135将基准电压节点nvref和电源电压节点nvdd连接,所以在该规定期间,监视对象电压不会超过判定电压vref+vof。然后,在经过规定期间之后,连接控制电路135使基准电压节点nvref和电源电压节点nvdd的连接断开,由此基准电压vref收敛到希望的规定电压。由此,在基准电压vref收敛到希望的规定电压之后,比较器133能够对监视对象电压和基准电压vref进行比较。即,根据本实施方式,在监视对象电压超过希望的判定电压vref+vof之前,上电复位电路130不判定为复位解除。

42.此外,在规定期间内不判定为复位解除,由此能够在电源电压vlog和基准电压vref稳定之后解除复位。由此,如上述图3所示,即使在基准电压vref不追随电源电压vdd的情况下,在本实施方式中,也在监视对象电压超过希望的判定电压后,判定为复位解除。此外,在电源电压vdd上升时,电路装置100的内部电源电压即电源电压vlog有可能成为过冲等不稳定的性能。在本实施方式中,由于在规定期间内不判定为复位解除,所以在电源电压vlog稳定后才解除被供给电源电压vlog的电路的复位。

43.以下,详细说明图4的结构例。

44.偏置电路131包含p型晶体管ta1、ta2、耗尽型的n型晶体管ta3和n型晶体管ta4。另外,未被称为耗尽型的晶体管是增强型的。

45.p型晶体管ta1、ta2的源极与被供给电源电压vdd的电源电压节点nvdd连接。p型晶体管ta1的漏极与p型晶体管ta1、ta2的栅极、n型晶体管ta3的漏极以及偏置节点nvrp连接。n型晶体管ta3的源极以及栅极与被供给地电压vss的地节点nvss连接。p型晶体管ta2的漏极与n型晶体管ta4的漏极和栅极、以及偏置节点nvna连接。n型晶体管ta4的源极与地节点nvss连接。另外,地电压vss只要是比电源电压vdd、以及作为监视对象电压的电源电压vlog低的电源电压即可。

46.n型晶体管ta3的漏电流流过p型晶体管ta1,由此产生偏置电压vrp。偏置电路131将偏置电压vrp从偏置节点nvrp输出到连接控制电路135和比较器133。n型晶体管ta3的漏电流被p型晶体管ta2镜像,该p型晶体管ta2的漏电流流过n型晶体管ta4,由此产生偏置电压vna。偏置电路131将偏置电压vna从偏置节点nvna输出到基准电压生成电路132和比较器133。

47.基准电压生成电路132包含耗尽型的n型晶体管tb1和n型晶体管tb2。

48.n型晶体管tb1的漏极与电源电压节点nvdd连接,源极与n型晶体管tb2的漏极和基准电压节点nvref连接。n型晶体管tb2的源极与地节点nvss连接。n型晶体管tb1、tb2的栅极与偏置节点nvna连接。

49.通过将偏置电压vna输入到n型晶体管tb1、tb2的栅极,在n型晶体管tb1、tb2中流过电流。根据该电流和n型晶体管tb1、tb2的尺寸决定基准电压vref。这里的基准电压vref是收敛为规定电压后的基准电压。例如,通过改变n型晶体管ta4、tb2的镜像比,流过n型晶体管tb1的电流改变,所以能够调整基准电压vref。或者,通过改变n型晶体管tb1的尺寸,n型晶体管tb1的源-漏间电压改变,所以能够调整基准电压vref。晶体管的尺寸例如是栅极长度、栅极宽度或这两者。

50.比较器133包含n型晶体管tc1~tc6和p型晶体管tc7~tc9。

51.p型晶体管tc7、tc8的源极与被供给监视对象电压的监视对象节点nvlog连接。p型晶体管tc7的栅极及源极与p型晶体管tc8的栅极和n型晶体管tc1的漏极连接。p型晶体管tc8的漏极与n型晶体管tc2的漏极和p型晶体管tc9的栅极连接。n型晶体管tc1、tc2的源极与n型晶体管tc3的漏极连接。n型晶体管tc1的栅极与基准电压节点nvref连接,n型晶体管tc2的栅极与监视对象节点nvlog连接。n型晶体管tc3的源极与n型晶体管tc4的漏极连接,栅极与偏置节点nvna连接。n型晶体管tc4的源极与地节点nvss连接,栅极与偏置节点nvnb连接。从未图示的偏置电路向偏置节点nvnb输出偏置电压vnb。

52.p型晶体管tc9的源极与监视对象节点nvlog连接,源极与n型晶体管tc5的漏极和上电复位电路130的输出节点nporq连接。n型晶体管tc5的源极与n型晶体管tc7的漏极连接,栅极与偏置节点nvna连接。n型晶体管tc6的源极与地节点nvss连接,栅极与偏置节点nvnb连接。

53.n型晶体管tc1、tc2构成差动对,n型晶体管tc1的栅极对应于比较器133的负极输入节点,n型晶体管tc2的栅极对应于比较器133的正极输入节点。向负极输入节点输入基准电压vref,向正极输入节点输入电源电压vlog。比较器133在vlog》vref时,将电源电压vlog的上电复位信号porq输出到输出节点nporq,在vlog《vref时,将地电压vss的上电复位信号porq输出到输出节点nporq。

54.连接控制电路135包含cr电路136和开关swpu。开关swpu由晶体管构成,这里假设是p型晶体管。

55.构成开关swpu的p型晶体管的源极与电源电压节点nvdd连接,漏极与基准电压节点nvref连接,栅极与控制信号节点ncrq连接。

56.cr电路136基于电源电压vdd向控制信号节点ncrq输出用于将开关swpu控制为接通或断开的控制信号crq。cr电路136在电源电压vdd接通后的规定期间,将控制信号crq维持在低电平,由此将开关swpu维持成接通。cr电路136在经过了规定期间时使控制信号crq

从低电平变为高电平,从而使开关swpu从接通变为断开。

57.在以上的本实施方式中,连接控制电路135包含开关swpu和cr电路136。开关swpu被设置在电源电压节点nvdd和基准电压节点nvref之间。cr电路136向开关swpu输出控制信号crq,在电源电压vdd接通后经过了规定期间时,该控制信号crq将开关swpu从接通控制为断开。

58.根据本实施方式,在电源电压vdd接通后的规定期间,开关swpu接通,所以基准电压节点nvref与电源电压节点nvdd连接。

59.由此,在电源电压vdd接通后的规定期间,输入到比较器133的基准电压vref成为电源电压vdd。并且,在经过了规定期间时,开关swpu从接通变为断开,所以比较器133能够对基准电压vref和监视对象电压进行比较。

60.此外,在本实施方式中,基准电压生成电路132基于电源电压vdd生成基准电压vref。

61.当开关swpu对基准电压节点nvref和电源电压节点nvdd进行了连接时,电源电压节点nvdd和n型晶体管tb2的源极经由开关swpu和n型晶体管tb1连接。电源电压vdd和vlog等不同的电源电压优选不被连接,而根据本实施方式,n型晶体管tb2的源极与电源电压节点nvdd连接。

62.另外,在本实施方式中,基准电压生成电路132包含耗尽型的n型晶体管tb1和增强型的n型晶体管tb2。耗尽型的n型晶体管tb1设置在电源电压节点nvdd与基准电压节点nvref之间,其栅极被输入偏置电压vna。增强型的n型晶体管tb2设置在基准电压节点nvref与地节点nvss之间,其栅极被输入偏置电压vna。

63.根据本实施方式,能够降低比较器133正常工作的电源电压vdd的最小值。比较器133的正常工作是指比较器133所含的晶体管在饱和区域工作。

64.例如,可以考虑不设置本实施方式的基准电压生成电路132,而使比较器133的n型晶体管tc1为耗尽型,将其栅极连接于地节点nvss的结构。当设该结构中的差动对的偏移电压为vof'时,复位解除的判定电压为vof'。考虑由于工艺变动,例如p型晶体管的阈值电压上升、n型晶体管的阈值电压下降的情况。在该情况下,在电源电压vlog下降到判定电压vof'之前,p型晶体管tc8不能维持饱和区域,p型晶体管tc9导通,上电复位信号porq成为高电平,有可能解除复位。因此,需要使本来应该在判定电压vof'附近的电源电压vlog的最小值比判定电压vof'高。由于电源电压vdd至少需要比电源电压vlog的最小值高,所以也需要提高电源电压vdd的最小值。

65.关于这一点,根据本实施方式,通过设置上述结构的基准电压生成电路132,能够使差动对的n型晶体管tc1为增强型,并且能够减小差动对的偏移电压。如上所述,通过调整构成基准电压生成电路132的n型晶体管tb1、tb2的尺寸,能够调整基准电压vref。通过差动对的偏移电压减小、以及能够调整基准电压vref,能够降低比较器133正常工作的电源电压vdd的最小值。

66.如之后利用图8中叙述的那样,例如,在实时时钟装置200的电路装置100中使用上电复位电路130。在包含实时时钟装置200和cpu或微型计算机等处理器的系统中,电源电压vdd是提供给处理器和实时时钟装置200的系统电源电压。在这样的系统中,即使在处理器不工作时,实时时钟装置200也进行计时,因此要求在处理器不工作那样的低电源电压vdd

下,实时时钟装置200也工作。因此,电源电压vdd的最小值越低越好,而根据本实施方式,能够尽量降低电源电压vdd的最小值。

67.另外,在图1中,电源电压vlog被提供给基准电压生成电路132,但晶体管tb1、tb2的结构与图4相同。因此,能够降低比较器133正常工作的电源电压vdd的最小值这一作用效果,在图1的基本结构例中也同样成立。

68.图5是cr电路136的详细结构例。cr电路136包含第一p型晶体管te1、第二p型晶体管ta2、n型晶体管te3、电容器ce、第一反相器ie1和第二反相器ie2。

69.cr电路向开关swpu输出控制信号crq,在经过了由电容器ce的电容值决定的规定期间时,该控制信号crq从有效转变为无效。当控制信号crq从有效变为无效时,开关swpu从接通变为断开。另外,有效是使开关swpu接通的逻辑电平,这里是低电平。无效是使开关swpu断开的逻辑电平,这里是高电平。

70.根据本实施方式,根据电容器ce的电容值设定规定期间,输出在经过了该规定期间时从有效变为无效的控制信号crq。具体而言,在将电容器ce的一端的电压设为crout时,根据电压crout的时间变化的速度来决定规定期间的长度。该电压crout的时间变化的速度由电容器ce的电容值和流过电容器ce的一端的电流决定。

71.第一p型晶体管te1设置在电源电压节点nvdd与电容器ce的一端之间。第一p型晶体管te1的栅极被输入偏置电压vrp。具体而言,第一p型晶体管te1的源极与电源电压节点nvdd连接,漏极与电容器ce的一端连接,栅极与偏置节点nvrp连接。电容器ce的另一端与地节点nvss连接。

72.根据本实施方式,第一p型晶体管te1成为恒流源,通过向电容器ce的一端输入恒流而对电容器ce进行充电。根据该恒流的电流值和电容器ce的电容值,决定规定期间的长度。

73.n型晶体管te3的漏极与电容器ce的一端连接,源极以及栅极与地节点连接。

74.第一p型晶体管te1具有以从电容器ce的一端朝向电源电压节点nvdd的方向为正向的寄生二极管,n型晶体管te3具有以从电容器ce的一端朝向地节点nvss的方向为正向的寄生二极管。将这些寄生二极管的正向电压设为vdiode。在电源电压vdd接通之前为地电压附近时,通过上述寄生二极管,电容器ce的一端电压crout处于-vdiode~+vdiode的范围。由此,在接通了电源电压vdd时,电容器ce的一端电压crout从大致确定的电压上升,能够使规定期间大致恒定。

75.对第一反相器ie1输入电容器ce的一端电压crout。对第二反相器ie2输入第一反相器ie1的输出信号ie1q,第二反相器ie2输出控制信号crq。第二p型晶体管te2设置在电源电压节点nvdd与电容器ce的一端之间,栅极被输入第一反相器ie1的输出信号ie1q。具体地,第二p型晶体管te2的源极与电源电压节点nvdd连接,漏极与电容器ce的一端连接,栅极与第一反相器ie1的输出节点连接。

76.根据本实施方式,第一反相器ie1在电容器ce的一端电压crout超过逻辑阈值电压时,使输出信号ie1q从高电平变为低电平。第二反相器ie2将输出信号ie1q的逻辑反转信号作为控制信号crq输出,因此在输出信号ie1q从高电平变为低电平时,使控制信号crq从低电平变为高电平。这样,从接通电源电压vdd到电容器ce的一端电压crout超过逻辑阈值电压为止的期间成为规定期间。

77.此外,根据本实施方式,在第一反相器ie1的输出信号ie1q从高电平变为低电平时,第二p型晶体管te2从截止变为导通,将电容器ce的一端和电源电压节点nvdd连接。由此,由于电容器ce的一端电压crout被固定为电源电压vdd,所以控制信号crq被固定在高电平。即,第二p型晶体管te2作为用于在复位被解除后维持复位解除状态的锁存机构发挥功能。

78.图6是说明cr电路136和开关swpu的动作的波形图。当接通电源电压vdd时,电容器ce的充电开始,电容器ce的一端电压crout逐渐上升。在电压crout达到第一反相器ie1的逻辑阈值电压的时刻tcr,第一反相器ie1的输出信号ie1q从电源电压vdd变成地电压vss。即,输出信号ie1q从高电平变为低电平。由此,第二p型晶体管te2从截止变为导通,电容器ce的一端电压crout成为电源电压vdd。

79.在时刻tcr之前,第二反相器ie2的输出信号即控制信号crq为低电平。因此,在时刻tcr之前,开关swpu接通,基准电压vref成为电源电压vdd。在时刻tcr,第二反相器ie2的输出信号即控制信号crq从低电平变为高电平。由此,开关swpu从接通变为断开,基准电压节点nvref和电源电压节点nvdd的连接断开,基准电压生成电路132生成的基准电压vref被输入到比较器133。从接通电源电压vdd到时刻tcr的期间对应于规定期间。即,根据电容器ce的一端电压crout达到第一反相器ie1的逻辑阈值电压为止的时间,决定规定期间的长度。

80.图7是说明图4的上电复位电路130的动作的波形图。接通电源电压vdd时,由调节器153生成的电源电压vlog追随电源电压vdd上升,然后收敛于稳定的电压。图7表示电源电压vlog过冲之后稳定的例子。

81.从接通电源电压vdd到时刻tcr,开关swpu接通,因此基准电压vref成为与电源电压vdd相同的电压。因此,比较器133的判定电压vref+vof被保持在高于电源电压vlog的状态,并且不被判定为复位解除。

82.在电源电压vlog超过逻辑阈值电压vtlg的时刻tlg,上电复位信号porq的逻辑电平从不确定x确定为高电平或低电平。通过预先设定电容器ce的电容值等使得时刻tcr比时刻tlg靠后,能够在时刻tlg将上电复位信号porq确定为低电平。即,能够将输入了上电复位信号porq的电路可靠地复位。

83.在时刻tcr,由于开关swpu从接通变为断开,所以基准电压vref从电源电压vdd下降到规定电压。在基准电压vref变成满足vref+vof《vlog的时刻tpor,上电复位信号porq从低电平变成高电平。由此,被输入上电复位信号porq的电路被解除复位。

84.如上所述,基准电压vref临时成为电源电压vdd,在经过规定期间后,基准电压vref下降到规定电压。由此,不会在不希望的电压下判定为复位解除。

85.此外,通过以在电源电压vlog稳定之后成为时刻tcr的方式预先设定电容器ce的电容值等,能够在电源电压vlog稳定之后对通过电源电压vlog进行动作的电路进行复位解除。如果在电源电压vlog保持不稳定的状态下对电路进行复位解除,则有可能发生电路误动作等不良情况,但是根据本实施方式,能够降低这种不良情况的可能性。

86.3.实时时钟装置

87.作为包含上电复位电路130的电路装置100的例子,对实时时钟装置200的电路装置100进行说明。但是,上述的上电复位电路130能够内置于各种用途的电路装置。

88.图8是实时时钟装置200的结构例和电路装置100的第三结构实例。实时时钟装置200包含振子10和电路装置100。电路装置100包含电源电路110、处理电路120、上电复位电路130、振荡电路150、温度检测电路160、接口电路170、端子tvdd、tvbat、tvout、tif、xi、xq。图8的上电复位电路130对应于图1或图4的上电复位电路130。

89.向端子tvdd提供包含实时时钟装置200的系统的电源电压vdd。该系统包含作为实时时钟装置200的主机装置的处理器,该处理器通过电源电压vdd进行动作。在端子tvbat上连接电池,从该电池供给电池电压vbat。电池是二次电池或一次电池,是实时时钟装置200的备用电源。即,当不提供电源电压vdd并且处理器不工作时,实时时钟装置200通过电池电压vbat工作。

90.电源电路110监视电源电压vdd和电池电压vbat,根据其监视结果切换电源电压vdd和电池电压vbat,并将该选择的电压作为电压vout输出。在端子tvout上连接用于使电压vout稳定化的稳定化电容器。电源电路110由电压vout生成作为电路装置100的内部电源电压的电源电压vosc、vdda、vlog。

91.处理电路120是利用电源电压vlog进行动作的逻辑电路,进行包含计时处理的各种处理以及电路装置100的各部分的控制。处理电路120经由接口电路170与处理器进行通信。接口电路170经由端子tif与处理器连接。在图8中将端子tif省略为了一个,但实际上设置了接口用的多个端子。对处理电路120输入上电复位信号porq,处理电路120根据上电复位信号porq被复位及解除复位。处理电路120包含计时电路121和温度补偿电路122。

92.计时电路121根据振荡电路150生成的时钟信号进行计时处理,生成计时信息。计时电路121具有根据时钟信号进行计数动作的计数器,将该计数器的计数值作为计时信息输出。通过该计数动作生成计时信息的处理相当于计时处理。计时信息是表示系统的当前时间的信息,例如表示实时时钟装置200启动并初始化后的经过时间。计时信息能够经由接口电路170从处理器读出。

93.温度补偿电路122根据温度检测电路160输出的温度检测数据,输出用于使振荡电路150的振荡频率与温度无关地保持恒定的温度补偿数据。

94.温度补偿电路122从将振荡频率的温度特性表格化的查找表中提取与温度对应的温度补偿数据,或者通过将温度代入到对振荡频率的温度特性进行了近似的多项式函数中,由此输出温度补偿数据。

95.温度检测电路160包含温度传感器和a/d转换电路,以电源电压vdda进行动作。温度传感器利用二极管的正向电压的温度依赖性,输出依赖于温度的温度检测电压。a/d转换电路对温度检测电压进行a/d转换,输出温度检测数据。

96.振荡电路150的输入节点和输出节点与端子xi、xq连接,振荡电路150通过驱动与端子xi、xq连接的振子而振荡,通过该振荡生成时钟信号。振子10是通过电信号产生机械振动的元件。振子10可以是石英振动片、压电振动片、saw谐振器或mems振子等各种振子。saw为表面声波(surface acoustic wave)的缩写,mems为微机电系统(micro electro mechanical systems)的缩写。振荡电路150以与温度补偿数据对应的振荡频率进行振荡。例如,振荡电路150包含对温度补偿数据进行d/a转换的d/a转换电路、以及通过该d/a转换输出来可变地控制电容值的可变电容式电容器。可变电容式电容器的一端与振荡电路150的输入节点或输出节点连接。

97.图9是电源电路110的详细结构例。电源电路110包含p型晶体管111~113、开关控制电路114、第一检测电路115、第二检测电路116和调节器151~153。

98.第一检测电路115检测电源电压节点nvdd的电源电压vdd是否低于第一检测电压,并将结果作为第一检测信号det1输出到开关控制电路114。第一检测电路115包含:对电源电压vdd进行分压的电阻分压电路;以及对该分压电压与第一检测电压进行比较的比较器。第二检测电路116检测电池电压节点nvbat的电池电压vbat是否低于第二检测电压,并将其结果作为第二检测信号det2输出到开关控制电路114。第二检测电路116包含:对电池电压vbat进行分压的电阻分压电路;以及对该分压电压与第二检测电压进行比较的比较器。第一检测电压以及第二检测电压例如由未图示的电压生成电路生成。

99.p型晶体管111的源极和漏极中的一个与电源电压节点nvdd连接,源极和漏极中的另一个以及背栅与节点nvout连接。p型晶体管112的源极和漏极中的一个与节点na连接,源极和漏极中的另一个以及背栅与节点nvout连接。p型晶体管113的源极和漏极中的一个与节点na连接,源极和漏极中的另一个以及背栅与电池电压节点nvbat连接。在图9中用虚线表示的二极管是在源极和漏极中的一个与背栅之间产生的寄生二极管。

100.开关控制电路114根据第一检测信号det1和第二检测信号det2将p型晶体管111~113控制为导通或截止。具体地,当检测到电源电压vdd高于第一检测电压时,开关控制电路114使p型晶体管111导通,使p型晶体管112、113截止。由此,向节点nvout输出电压vout=vdd。当检测到电源电压vdd低于第一检测电压、且电池电压vbat高于第二检测电压时,开关控制电路114使p型晶体管111截止,使p型晶体管112、113导通。由此,向节点nvout输出电压vout=vbat。

101.调节器151通过调节电压vout来生成电源电压vosc,并将该电源电压vosc输出到振荡电路150。调节器152通过调节电压vout来生成电源电压vdda,并将该电源电压vdda输出到温度检测电路160。调节器153调节电压vout来生成电源电压vlog,并将该电源电压vlog输出到处理电路120。调节器151~153例如是由运算放大器和电阻等构成的线性调节器。

102.在以上的本实施方式中,电路装置100包含调节器153和处理电路120。调节器153根据第一电源电压,生成作为监视对象电压的第二电源电压。在图8和图9中,电源电压vdd是第一电源电压,电源电压vlog是第二电源电压。处理电路120根据第二电源电压进行动作,通过上电复位信号porq进行复位和复位解除。

103.例如,在对电路装置100最初接通电源电压vdd或电池电压vbat时,或者因电源电压vdd等的下降而使得电压vout临时下降时等,进行处理电路120的复位及复位解除。在上电复位未正常进行的情况下,需要经由接口电路170执行软复位等替代手段。通过在图8中应用图4的上电复位电路130,不会以不希望的电压进行复位解除,因此能够进行可靠的复位和复位解除。此外,当电源电压vdd下降时,电源电路110切换到电池电压vbat,但需要在下降到进行上电复位的电压之前进行切换。若将进行该上电复位的电源电压vdd设为最小值,则优选该最小值比处理器的可工作电压低。即,优选在处理器不能工作的电源电压下切换为备用电源。通过在图8中应用图1及图4的上电复位电路130,成为上述的基准电压生成电路132和比较器133的结构,能够尽可能地降低在电源电压vdd的下降时不进行复位的最小值。

104.以上说明的本实施方式的电路装置包含比较器、基准电压生成电路和连接控制电路。比较器对根据电源电压生成的监视对象电压和基准电压进行比较,由此输出上电复位信号。基准电压生成电路生成基准电压,并将基准电压输出到基准电压节点。连接控制电路连接在被供给电源电压的电源电压节点和基准电压节点之间。连接控制电路在接通电源电压后的规定期间,将基准电压节点和电源电压节点连接。

105.根据本实施方式,在向电路装置接通电源电压后的规定期间,连接控制电路将基准电压节点和电源电压节点连接,所以在该规定期间,监视对象电压不会超过比较器的判定电压。判定电压是收敛为规定电压后的基准电压与比较器的偏移电压之和。然后,在经过规定期间后,连接控制电路使基准电压节点和电源电压节点的连接断开,由此基准电压收敛到希望的规定电压。由此,在基准电压收敛到希望的规定电压之后,比较器能够对监视对象电压和基准电压进行比较。

106.另外,在本实施方式中,连接控制电路也可以包含:开关,其设置在电源电压节点与基准电压节点之间;以及cr电路,其向开关输出控制信号,在电源电压接通后经过了规定期间时,该控制信号将开关从接通控制为断开。

107.根据本实施方式,在接通电源电压后的规定期间,开关接通,所以基准电压节点与电源电压节点连接。由此,在接通电源电压后的规定期间,输入到比较器的基准电压成为电源电压。而且,在经过了规定期间时,开关从接通变为断开,所以比较器能够对基准电压与监视对象电压进行比较。

108.此外,在本实施方式中,cr电路也可以具有电容器,将控制信号输出到开关,在经过了由电容器的电容值决定的规定期间时,该控制信号从有效转变为无效。开关可以在控制信号从有效变为无效时,从接通变为断开。

109.根据本实施方式,根据电容器的电容值设定规定期间。并且,cr电路能够输出在经过了该规定期间时从有效变为无效的控制信号。

110.此外,在本实施方式中,电路装置也可以包含生成偏置电压的偏置电路。cr电路可以包含第一p型晶体管,该第一p型晶体管设置在电源电压节点与电容器的一端之间,栅极被输入偏置电压。

111.根据本实施方式,第一p型晶体管成为恒流源,通过向电容器的一端输入恒流来对电容器进行充电。根据该恒流的电流值和电容器的电容值,决定规定期间的长度。

112.另外,在本实施方式中,cr电路也可以包含n型晶体管,该n型晶体管的漏极与电容器的一端连接,源极以及栅极与地节点连接。

113.第一p型晶体管具有以从电容器的一端向电源电压节点的方向为正向的寄生二极管,n型晶体管具有以从电容器的一端向地节点的方向为正向的寄生二极管。由此,在接通了电源电压时,电容器的一端电压从大致确定的电压上升,能够使规定期间大致恒定。

114.另外,在本实施方式中,cr电路也可以包含:第一反相器,其被输入电容器的一端电压;第二反相器,其被输入第一反相器的输出信号,输出控制信号;以及第二p型晶体管,其设置在电源电压节点与电容器的一端之间,栅极被输入第一反相器的输出信号。

115.根据本实施方式,第一反相器在电容器的一端电压超过了逻辑阈值电压时,使输出信号从高电平成为低电平。由此,从接通电源电压起到电容器的一端电压超过逻辑阈值电压为止的期间成为规定期间。并且根据本实施方式,当第一反相器的输出信号从高电平

变成低电平时,第二p型晶体管从截止变为导通,将电容器的一端和电源电压节点连接。由此,第二p型晶体管作为用于在复位被解除后维持复位解除状态的锁存机构发挥功能。

116.另外,在本实施方式中,基准电压生成电路也可以基于电源电压生成基准电压。

117.当开关将基准电压节点和电源电压节点连接时,电源电压节点和基准电压生成电路内的晶体管的源极经由开关和基准电压生成电路内的晶体管连接。电源电压和内部电源电压等不同的电源电压优选不被连接,而根据本实施方式,基准电压生成电路内的晶体管的源极与电源电压节点连接。

118.此外,在本实施方式中,电路装置也可以包含生成偏置电压的偏置电路。基准电压生成电路可以包含耗尽型的n型晶体管和增强型的n型晶体管。耗尽型的n型晶体管设置在电源电压节点与基准电压节点之间,其栅极被输入偏置电压。增强型的n型晶体管可以设置在基准电压节点与地节点之间,其栅极被输入偏置电压。

119.根据本实施方式,由于能够减小比较器的偏移电压、以及能够调整基准电压,所以能够降低比较器正常工作的电源电压的最小值。

120.此外,在本实施方式中,电路装置也可以包含调节器和处理电路。调节器可以在将电源电压设为第一电源电压时,根据第一电源电压生成作为监视对象电压的第二电源电压。处理电路可以基于第二电源电压进行动作,并通过上电复位信号进行复位和复位解除。

121.通过使用本实施方式的上电复位电路对处理电路进行复位和复位解除,不会以不希望的电压进行复位解除,因此能够可靠地对处理电路进行复位和复位解除。

122.此外,本实施方式的实时时钟装置包含上述任意一项所述的电路装置和振子。电路装置包含调节器、处理电路和振荡电路。调节器在将电源电压设为第一电源电压时,根据第一电源电压生成作为监视对象电压的第二电源电压。处理电路基于第二电源电压进行动作,并通过上电复位信号进行复位和复位解除。振荡电路通过使振子振荡来生成时钟信号。处理电路包含根据时钟信号进行计时处理的计时电路。

123.这样,本实施方式的电路装置可以应用于实时时钟装置。而且,通过使用本实施方式的上电复位电路对处理电路进行复位和复位解除,不会以不希望的电压进行复位解除,所以能够可靠地对实时时钟装置的处理电路进行复位和复位解除。

124.另外,虽然如上那样对本实施方式进行了详细说明,但本领域技术人员能够容易理解到,可以在实质上不脱离本公开的新颖事项及效果的情况下实现多种变形。因此,本公开的范围包含所有这样的变形例。例如,在说明书或附图中,对于至少一次地与更广义或同义的不同用语一起记载的用语,在说明书或附图的任何位置处,都可以将其置换为该不同的用语。此外,本实施方式和变形例的所有组合也包含在本公开的范围内。此外,上电复位电路、电路装置和实时时钟装置的结构和动作等也不限于本实施方式中说明的内容,可以实施各种变形。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1