用于发光二极管的具有短路保护的电路的制作方法

1.本公开涉及用于控制通过发光二极管的电流的电路。

背景技术:

2.驱动器通常被用于控制负载处的电压、电流或功率。例如,发光二极管(led)驱动器可以控制供应给发光二极管串的功率。一些驱动器可以包括dc至dc功率转换器,诸如降压-升压转换器、降压转换器、升压转换器或另一个dc至dc转换器。这种dc至dc功率转换器可以被用于基于负载的特性来控制并且可能改变负载处的功率。dc至dc功率转换器对于控制供应给一个或多个led串的电流可能特别有用。

3.通常需要控制或限制到led串的电流。为此,可以在dc至dc功率转换器与led串之间放置电阻器,以限制供应给led串的电流。

技术实现要素:

4.一般而言,本公开描述了用于控制从电压源到一个或多个发光二极管的电压的电路,以便在一个或多个发光二极管发生短路的情况下提供短路保护。该电路可以包括第一晶体管,第一晶体管包括功率开关,该功率开关被配置为限定从电压源到一个或多个发光二极管的负载电流路径。该电路还可以包括第二晶体管,可以基于发光二极管来控制第二晶体管,其中第二晶体管被配置为当发光二极管中的一个或多个发光二极管表现出电短路时关断。第一晶体管可以被配置为响应于第二晶体管关断而关断,从而提供用于电路的短路保护。

5.在一个示例中,本公开描述了一种被配置为控制从电压源到一个或多个发光二极管的电压的电路。该电路包括:第一电引脚,被配置为被电气地连接到电压源;第二电引脚,被配置为被电气地连接到一个或多个发光二极管;第一晶体管,被电气地耦合到第一电引脚和第二电引脚,其中第一晶体管包括功率开关,功率开关被配置为限定从电压源到一个或多个发光二极管的负载电流路径;第一电阻器被电气地耦合到第一电引脚和第二电引脚,并且与负载电流路径并联地放置。此外,该电路还包括第二晶体管,被电气地耦合到参考节点和第一晶体管的控制节点,其中第二晶体管的控制节点被电气地耦合到第二电引脚,并且第二电阻器被放置在第一电引脚与第一晶体管的控制节点之间。第二晶体管被配置为响应于一个或多个发光二极管中的短路事件而关断,以及第一晶体管被配置为响应于第二晶体管的关断而关断。

6.在另一个示例中,本公开描述了一种被配置为控制从电压源到发光二极管串的电压的电路,并且该电路可以被配置为在与发光二极管串内的单个发光二极管相关联的短路的情况下提供短路保护。该电路可以包括:第一电引脚,被配置为被电气地连接到电压源;第二电引脚,被配置为被电气地连接到发光二极管串;第一晶体管,被电气地耦合到第一电引脚和第二电引脚,其中第一晶体管包括功率开关和第一电阻器,功率开关被配置为限定从电压源到一个或多个发光二极管的负载电流路径,并且第一电阻器被电气地耦合到第一

电引脚和第二电引脚,并且与负载电流路径并联地放置。此外,该电路还可以包括第二晶体管,被电气地耦合到参考节点和第一晶体管的控制节点,其中第二晶体管的控制节点被电气地耦合到第二电引脚,第二电阻器被放置在第一电引脚与第一晶体管的控制节点之间,齐纳二极管被放置在第二电引脚与第二晶体管的控制节点之间,使得二极管的正向传导路径被限定为从第二晶体管的控制节点到第二电引脚,并且第三电阻器被放置在参考节点与第二晶体管的控制节点之间。第二晶体管被配置为响应于与发光二极管串内的单个发光二极管相关联的短路事件而关断,以及第一晶体管被配置为响应于第二晶体管的关断而关断。

7.在另一个示例中,本公开描述了一种方法,该方法包括:经由电路控制从电压源到一个或多个发光二极管的电压,该电路包括第一晶体管,第一晶体管包括功率开关,该功率开关被配置为限定从电压源到一个或多个发光二极管的负载电流路径;基于发光二极管控制第二晶体管的控制节点,其中第二晶体管被配置为当发光二极管中的一个或多个发光二极管表现出电短路时关断;以及控制第一晶体管的控制节点,使得第一晶体管被配置为响应于第二晶体管的关断而关断。

8.在附图和以下描述中阐述了这些示例和其它示例的细节。其它特征、目的和优点将从描述和附图以及权利要求中显而易见。

附图说明

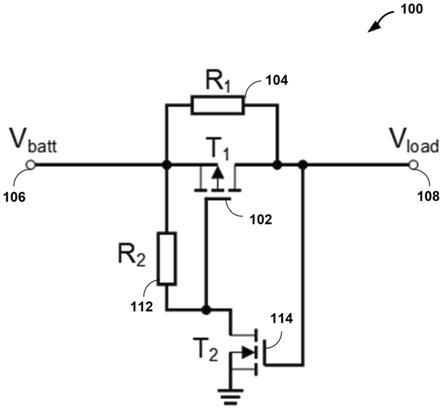

9.图1是可以被用于控制从电压源到一个或多个发光二极管(led)的电压的示例电路的电路图。

10.图2是示出与图1的电路类似的电路的电路图,并且包括附加的引脚以提供电路的状态信息。

11.图3是示出与图2的电路类似的电路的图,并且包括另一个附加的引脚以促进电路的附加的控制。

12.图4是包括可以被用于控制从电压源到led串的电压的另一个示例电路的装置的示例电路图。

13.图5是示出与图4的布置类似的装置的电路图,并且包括具有附加的引脚的电路以提供电路的状态信息。

14.图6是示出与图5的布置类似的装置的图,其中电路包括又一个附加的引脚和一些附加的电气元件以促进电路的附加的控制。

15.图7是与由本公开的电路执行的技术一致的流程图。

具体实施方式

16.本公开描述了用于控制从电压源到一个或多个发光二极管(led)的电压,以便在一个或多个led发生短路的情况下提供短路保护的电路。所描述的电路可以被用在多种led应用中,并且在需要识别短路事件的设置中尤其有用,诸如用于在机动车辆或电动车辆中使用的led。该电路在两个或多个led(或者两个或多个led串)并联连接的情况下也可以是非常有用的,其中led中的一个led(或者串中的一个串)可以显著地影响传输到另一个led(或另一个led串)的电压。

17.在一些示例中,该电路包括第一晶体管(例如,pmos),第一晶体管包括功率开关,该功率开关被配置为限定从电压源到一个或多个发光二极管的负载电流路径。该电路还包括第二晶体管(例如,nmos),第二晶体管可以基于发光二极管而被控制,其中第二晶体管被配置为当发光二极管中的一个或多个发光二极管表现出电短路时关断。第一晶体管被配置为响应于第二晶体管的关断而关断,从而提供用于电路的短路保护。换句话说,当电路的输出端出现短路时,第一晶体管可以从负载断开。第二晶体管类似于传感器,基本上感测第一晶体管的输出电压并且响应短路事件。在一些实施例中,可以将齐纳二极管添加到电路以使得能够检测和防止led串内的单个led短路的能力。

18.图1是可以被用于控制从电压源到一个或多个led的电压的示例电路100的电路图。电路100可以是具有包括高侧功率开关的第一晶体管102的所谓的“高侧”电路,并且电路100可以提供高侧短路保护。

19.如图1所示,电路100包括:第一电引脚106(也称为“输入引脚”),被配置为被电气地连接到电压源;以及第二电引脚108(也称为“输出引脚”),被配置为被电气地连接到一个或多个led。例如,电压源可以包括dc到dc功率转换器或通常被用于驱动led的另一个电压源。术语“vbatt”通常表示与第一电引脚106相关联的节点上的输入电压。术语“vload”通常表示与第二电引脚108相关联的节点上的输出电压,第二引脚可以被电气地耦合到一个或多个led。一个或多个led可以被布置在单独的电路上(例如,与电路100分开),并且具有led的单独的电路可以包括放置在led与电路100的第二电引脚108之间的限流电阻器。在一些示例中,led可以包括并联连接的两个或多个led(或者并联连接的两个或多个led串),这对于使用单个驱动器来驱动多个led或多个led集合的低成本应用可以是期望的。

20.电路100包括第一晶体管102,该第一晶体管102被电气地耦合到第一电引脚106和第二电引脚108。第一晶体管102在图1中也被标记为t1。第一晶体管102可以包括功率开关,该功率开关被配置为限定从耦合到第一电引脚106的电压源到耦合到输出引脚108的一个或多个发光二极管的负载电流路径。在一些示例中,第一晶体管102可以包括pmos晶体管,这对于负载电流路径来说可以是具有成本效益的功率开关设计。然而,在其它示例中,其它类型的晶体管也可以被用于第一晶体管102。

21.电路100还包括第一电阻器104,该第一电阻器104被电气地耦合到第一电引脚106和第二电引脚108,并且与第一晶体管102并联放置。换句话说,第一电阻器104和通过第一晶体管102的负载电流路径是并联的电气路径。第一电阻器104限定了从第一电引脚106到第二电引脚108的高阻抗路径,当第一晶体管102导通时,该高阻抗路径远高于通过第一晶体管102的负载电流路径。在一些示例中,电阻器104限定了在50千欧(kohms)至100kohm之间的电阻,尽管在其它示例中也可以使用另一个大小的电阻器。

22.如图1所示,第二晶体管114被电气地耦合到第一晶体管102的控制节点(例如,栅极)和参考节点(例如,接地节点)。第二晶体管114在图1中也被标记为t2。在一些示例中,第二晶体管114可以包括nmos晶体管,这对于电路100来说可以是具有成本效益的设计。然而,在其它示例中,其它类型的晶体管也可以被用于第二晶体管114。

23.第二晶体管114的控制节点(例如,栅极)被电气地耦合到第二电引脚108。此外,第二电阻器112被放置在第一电引脚106与第一晶体管102的控制节点(例如,栅极)之间。在一些示例中,第二电阻器112限定了在10kohms至47kohms之间的电阻,尽管在其它示例中可以

使用另一个大小的电阻器。第二晶体管114被配置为响应于在连接到第二电引脚的一个或多个led中的短路事件而关断。以这种方式,基于连接到第二电引脚108的led上是否存在短路来控制第二晶体管114。如果连接到第二电引脚108的led中没有短路,则第二晶体管114保持导通。如果连接到第二电引脚108的一个或多个led中出现短路事件,则第二晶体管114关断。

24.根据本公开,第一晶体管102被配置为响应于第二晶体管114的关断而关断。以这种方式,可以响应于一个或多个led上的短路事件而禁用通过第一晶体管102的负载电流路径。一个或多个led上的短路事件导致第二晶体管114关断,这转而导致第一晶体管102关断。以这种方式,电路100包括针对一个或多个led中的短路事件的短路保护,这对于一些应用而言可能是期望的。当第一晶体管102关断时,从输入引脚106到输出引脚108的低阻抗路径被禁用,并且从输入引脚106到输出引脚108的唯一电流路径是通过第一电阻器104的高阻抗路径。这可以在一个或多个led中发生短路的情况下,保护电路100和更大系统的其它元件免受损坏或电气故障。

25.如上所述,在一些情况下,第一晶体管102可以包括pmos晶体管并且第二晶体管114可以包括nmos晶体管,这是有成本效益的实现。然而,更一般地,第一晶体管102和第二晶体管114均可以被实现为场效应晶体管(fet)、双极结型晶体管(bjt)、氮化镓(gan)开关或可能的可控硅整流器(scr)。fet的示例可以包括但不限于,结型场效应晶体管(jfet)、金属氧化物半导体fet(mosfet)、双栅极mosfet、绝缘栅双极晶体管(igbt)、任何其它类型的fet或它们的任何组合。mosfet的示例可以包括但不限于:pmos、nmos、dmos或任何其它类型的mosfet或它们的任何组合。bjt的示例可以包括但不限于,pnp、npn、异质结或任何其它类型的bjt或它们的任何组合。

26.在一个具体实现中,根据本公开的电路100可以利用两个mosfet(例如,对应于第一晶体管102的一个pmos以及对应于第二晶体管104的一个nmos)来感测短路事件并且对其作出反应。输入电压(v

batt

)被施加到pmos的源极(例如,第一晶体管102)和偏置电阻器104,而负载(例如,一个或多个led)被连接到pmos的漏极和接地。当施加输入电压v

batt

时,电阻器104将nmos(例如,第二晶体管114)的栅极偏置超过阈值,这意味着nmos导通,对pmos施加v

gs

=v

batt

。在这种情况下,pmos(例如,第一晶体管102)进入低欧姆状态。第二电阻器112可以限制进入nmos的电流并且上拉栅极以确保当负载中没有短路时nmos处于关断状态。如果负载被短路到接地,则nmos的v

gs

低于阈值,然后nmos晶体管转换为关断状态。如果nmos(例如,第二晶体管114)处于关断状态,则pmos(例如,第一晶体管102)被关断。以这种方式,可以通过感测nmos的漏极来检测负载中的对地短路。

27.图2是示出与图1的电路类似的电路的电路图,并且包括附加的引脚(例如,状态引脚216)以提供电路的状态信息。与图1类似,图2是可以被用于控制从电压源到一个或多个led的电压的示例电路(例如,电路200)的电路图。如图2所示,电路200包括:第一电引脚206(也称为“输入引脚”),被配置为被电气地连接到电压源;以及第二电引脚208(也称为“输出引脚”),被配置为被电气地连接到一个或多个led。与图1一样,在图2中,术语“vbatt”通常表示与第一电引脚206相关联的节点上的输入电压。术语“vload”通常表示与第二电引脚208相关联的节点上的输出电压,其可以被电气地耦合到一个或多个led。一个或多个led可以被布置在单独的电路(例如,与电路200分开)上,并且具有led的单独的电路可以包括被

放置在led与电路200的第二电引脚208之间的限流电阻器。

28.与图1的电路100类似,图2的电路200包括第一晶体管202,该第一晶体管202被电气地耦合到第一电引脚206和第二电引脚208。第一晶体管202在图2中也被标记为t1。第一晶体管202可以包括功率开关,该功率开关被配置为限定从耦合到第一电引脚206的电压源到耦合到输出引脚208的一个或多个发光二极管的负载电流路径。在一些示例中,第一晶体管202可以包括pmos晶体管,这对于负载电流路径来说可以是具有成本效益的功率开关设计。然而,在其它示例中,其它类型的晶体管也可以被用于第一晶体管202。

29.电路200还包括第一电阻器204,该第一电阻器204被电气地耦合到第一电引脚206和第二电引脚208并且与第一晶体管202并联放置。换句话说,第一电阻器204和通过第一晶体管202的负载电流路径是并联的电气路径。第一电阻器204限定了从第一电引脚206到第二电引脚208的高阻抗路径,当第一晶体管202导通时,该高阻抗路径远高于通过第一晶体管202的负载电流路径。在一些示例中,第一电阻器204限定了在50kohms至100kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。

30.如图2所示,第二晶体管214被电气地耦合到第一晶体管202的控制节点(例如,栅极)和参考节点(例如,接地节点)。第二晶体管214在图2中被标记为t2(其与图1的标记类似)。在一些示例中,第二晶体管214可以包括nmos晶体管,这对于电路200来说是具有成本效益的设计。然而,在其它示例中,其它类型的晶体管也可以被用于第二晶体管214。

31.第二晶体管214的控制节点(例如,栅极)被电气地耦合到第二电引脚208。此外,第二电阻器212被放置在第一电引脚206与第一晶体管202的控制节点(例如,栅极)之间。在一些示例中,第二晶体管212限定了10kohms至47kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。类似于图1的示例,在图2中,第二晶体管214被配置为响应于连接到第二电引脚208的一个或多个led中发生的短路时间而关断。以这种方式,基于连接到第二电引脚208的led上是否存在短路来控制第二晶体管214。如果连接到第二电引脚208的led中没有短路,则第二晶体管214保持导通。如果连接到第二电引脚208的一个或多个led中发生短路事件,则第二晶体管214关断。

32.第一晶体管202被配置为响应于第二晶体管214的关断而关断。以这种方式,可以响应于一个或多个led上的短路事件而禁用通过第一晶体管202的负载电流路径。一个或多个led上的短路事件导致第二晶体管214关断,这转而导致第一晶体管202关断。以这种方式,电路200包括针对一个或多个led中的短路事件的短路保护,这对于led控制而言可能是期望的。当第一晶体管202关断时,从输入引脚206到输出引脚208的低阻抗路径被禁用,并且从输入引脚206到输出引脚208的唯一电流路径是通过第一晶体管204的高阻抗路径。这可以在一个或多个led中发生短路的情况下,保护电路200和更大系统的其它元件免受损坏或电气故障。与图1的示例一样,对于图2的示例,led可以包括并联连接的两个或多个led(或并联连接的两个或多个led串),这对于单个驱动器被用于驱动多个led或多个led集合的低成本应用可能是期望的。

33.与图1的示例不同,图2中所示的电路200还包括状态引脚216,该状态引脚216被电气地耦合到第一晶体管202的控制节点(例如,栅极)。状态引脚216被配置为限定电路的、用于使用控制单元的状态信号。例如,控制单元可以包括微处理器,该微处理器将控制信号传递到限定连接到输入引脚206的电压源的dc至dc转换器。状态引脚216上的状态信号可以与

控制第一晶体管202的信号相同。因此,使第一晶体管202关断的信号也可以被用作状态信号216上的状态信号,以向连接到状态引脚216的外部控制单元报告短路事件。在一些低成本的短路保护解决方案中,图1中所示的示例可以比图2中所示的示例是更需要的,其中电路中的引脚的数目是成本问题,而当需要向外部控制单元报告任何短路事件时,图2中所示的示例可能比图1中的示例是更需要的。

34.在电路200的操作中,在启动时,如果输出端不存在对地短路,则r1偏置输出。如果不存在短路,则晶体管214将晶体管202偏置在低欧姆状态。如果出现短路,则第二晶体管214的栅极变为大约0v,并且这迫使第一晶体管202进入关断状态。可能发生一些电流泄漏,但是该电流泄漏通常被限于r1/v

batt

,对于(诸如机动车辆设置或电动车辆设置中)led照明情况,这可以是可接受的电流泄漏量。

35.图3是示出与图1和图2的电路类似的电路的图,但是还包括另一个附加的引脚(例如,控制引脚318),以促进由外部控制单元对电路的附加的控制。类似于图1和图2,图3是可以被用于控制从电压源到一个或多个led的电压的示例电路(例如,电路300)的电路图。如图3所示,电路300包括:第一电引脚306(也称为“输入引脚”),被配置为被电气地连接到电压源;以及第二电引脚308(也称为“输出引脚”),被配置为被电气地连接到一个或多个led。类似于图1和图2,术语“vbatt”通常表示与第一电引脚306相关联的节点上的输入电压。术语“vload”通常表示与第二电引脚308相关联的节点上的输出电压,第二电引脚可以被电气地耦合到一个或多个led。一个或多个led可以被布置在单独的电路(例如,与电路300分开)上,并且具有led的单独的电路可以包括被放置在led与电路300的第二电引脚308之间的限流电阻器。

36.类似于图1的电路100和图2的电路200,图3的电路300包括第一晶体管302,该第一晶体管302被电气地耦合到第一电引脚306和第二电引脚308。第一晶体管302在图3中也被标记为t1(其类似于图1和图2中的标记)。第一晶体管302可以包括功率开关,该功率开关被配置为限定从耦合到第一电引脚306的电压源到耦合到输出引脚308的一个或多个发光二极管的负载电流路径。在一些示例中,第一晶体管302可以包括pmos晶体管,这对于负载电流路径来说可以是具有成本效益的功率开关设计。然而,在其它示例中,其它类型的晶体管也可以被用于第一晶体管302。

37.电路300还包括第一电阻器304,该第一电阻器304被电气地耦合到第一电引脚306和第二电引脚308,并且与第一晶体管302并联放置。换句话说,第一电阻器304和通过第一晶体管302的负载电流路径是并联的电气路径。第一电阻器304限定从第一电引脚306到第二电引脚308的高阻抗路径,当第一晶体管302导通时,该高阻抗路径远高于通过第一晶体管302的负载电流路径。在一些示例中,第一电阻器304限定了50kohms至100kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。

38.如图3所示,第二晶体管314被电气地耦合到第一晶体管302的控制节点(例如,栅极)和参考节点(例如,接地节点)。第二晶体管314在图3中被标记为t2(其类似于图1和图2的标记)。在一些示例中,第二晶体管314可以包括nmos晶体管,这对于电路300来说可以是具有成本效益的设计。然而,其它示例中,其它类型的晶体管也可以被用于第二晶体管314。

39.第二晶体管314的控制节点(例如,栅极)被电气地耦合到第二电引脚308。然而,在图3所示的示例中,第二晶体管314不被直接地耦合到第二电引脚308,相反,二极管322被放

置在第二晶体管314的控制节点与第二电引脚308之间。二极管322被放置使得二极管322的正向传导路径是从第二晶体管314的控制节点到第二电引脚308的路径,并且反向传导路径(即,二极管322的击穿路径)是从第二电引脚308到第二晶体管314的控制节点的路径。

40.在图3中,第二电阻器302被放置在第一电引脚306与第一晶体管302的控制节点(例如,栅极)之间。在一些示例中,第二电阻器312限定了10kohms至47kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。类似于图1和图2的示例,在图3中,第二晶体管314被配置为响应于连接到第二电引脚308的一个或多个led中的短路事件而关断。以这种方式,基于连接到第二电引脚308的led上是否存在短路来控制第二晶体管314,。如果连接到第二电引脚308的led中没有短路,则第二晶体管314保持导通。如果在连接到第二电引脚308的一个或多个led中发生短路事件,则第二晶体管314关断。

41.第一晶体管302被配置为响应于第二晶体管314的关断而关断。以这种方式,通过第一晶体管302的负载电流路径可以响应于一个或多个led上的短路事件而被禁用。一个或多个led上的短路事件使第二晶体管314关断,这转而使第一晶体管302关断。以这种方式,电路300包括针对一个或多个led中的短路事件的电路保护,这对于led控制而言可能是期望的。当第一晶体管302关断时,从输入引脚306到输出引脚308的低阻抗路径被禁用,并且从输入引脚306到输出引脚308的唯一电流路径是通过第一电阻器304的高阻抗路径。这可以在一个或多个led中发生短路的情况下,保护电路300和更大系统的其它元件免受损坏或电气故障。与图1和图2的示例一样,对于图3的示例,led可以包括并联连接的两个或多个led(或并联连接的两个或多个led串),这对于单个驱动器被用于驱动多个led或多个led集合的低成本应用可能是期望的。

42.类似于图2中所示的示例,图3中所示的电路300还包括状态引脚316,该状态引脚316被电气地耦合到第一晶体管302的控制节点(例如,栅极)。状态引脚316被配置为限定电路的、用于使用控制单元的状态信号。例如,控制单元可以包括微控制器,该微控制器将控制信号传递到限定连接到输入引脚306的电压源的dc至dc转换器。状态引脚316上的状态信号可以与控制第一晶体管302的信号相同。因此,使第一晶体管302关断的信号也可以被用作状态引脚316上的状态信号,以向连接到状态引脚316的外部控制单元报告短路事件。因此,在一些低成本解决方案中,可能需要减少引脚数目并且避免状态引脚(诸如,图1的示例),而当需要向外部控制单元报告任何短路事件时,图2或图3中所示的示例可能是更需要的。

43.图3中所示的电路300还包括控制引脚318。第三电阻器320可以被放置在控制引脚318与第二晶体管314的控制节点(例如,栅极)之间。控制引脚318是相对于图1和图2中所示的示例的可选特征,并且对于需要外部控制的一些场景可能是期望的。特别地,控制引脚318可以允许外部控制单元提供电路300的导通-关断控制。电路30可以具有短路保护以防止连接到输出引脚308的一个或多个led短路,但是外部控制器也可能能够独立控制第二晶体管314的栅极。因此,无论连接到输出引脚308的led中是否存在任何短路,连接到控制引脚318的外部控制器都能够经由控制信号关断第二晶体管314。在这种情况下,第二晶体管314的关断将导致第一晶体管302的关断。以这种方式,外部控制单元能够通过第一晶体管302使能或禁用电路300的负载电流路径。

44.在一些示例中,除了图1中所示的电路100的特征,图3的电路300还包括被放置在

第二晶体管312的控制节点与第二电引脚308之间的二极管,使得二极管322的正向传导路径被限定为从第二晶体管314的控制节点到第二电引脚308。控制引脚318被配置为将来自控制电路(例如,外部控制单元)的控制信号提供给第二晶体管314的控制节点。第三电阻器320被放置在控制引脚320与第二晶体管314的控制节点之间,其中第二晶体管(例如,作为备选的,并且除了响应于连接到输出节点308的一个或多个短路事件而关断)还被配置为响应于来自控制电路的控制信号而关断。这种附加的控制对于led控制来说是期望的,尽管对于控制引脚318的额外的引脚来说对于图1和图2的示例可能需要相对于图3的示例降低成本的其它情况来说可能是期望的。

45.在一些示例中,除了图1所示的电路100的特征之外,图3的电路300包括电气地耦合到第一晶体管302的控制节点的第三电引脚(例如,状态引脚316),其中第三电引脚被配置为限定用于由控制单元使用的电路的状态信号。在该示例中,二极管322被放置在第二晶体管314的控制节点与第二电引脚(例如,输出引脚308)之间,使得二极管322的正向传导路径被限定为从第二晶体管314的控制节点到第二电引脚。第四电引脚(例如,控制引脚318)被配置为将来自控制电路的控制信号提供给第二晶体管314的控制节点,并且第三电阻器320被放置在第一电引脚与第二晶体管314的控制节点之间。在该示例中,第二晶体管314还被配置为响应于来自控制电路的控制信号而关断。

46.在电路300的操作中,对于图3所示的示例,在启动时,如果不存在对地短路,则第一电阻器304偏置输出。如果不存在短路并且控制信号由外部控制单元被施加到控制端子318,则第二晶体管314偏置第一晶体管302以将电路300的负载电流路径置于低欧姆状态。如果在输出端子308处出现短路,则第二晶体管314的栅极变为大约0v,这迫使第一晶体管302进入关断状态,从而导致电流通过电路300的第一电阻器304的更高的欧姆路径。可能发生一些电流泄漏,但是该电流泄漏通常被限于r1/v

batt

,对于(诸如机动车辆设置或电动车辆设置中)led照明情况,这可以是可接受的电流泄漏量。

47.图4至图6是可以被用于控制从电压源到led串的电压的电路的附加的电路图。尽管图1至图3的示例可以被配置为针对与一个或多个led相关联的led短路提供短路保护,但是图4至图6可以被设计为针对更大的led串内的单个led短路提供更精细的短路保护。

48.图4是包括被配置为连接到led模块401的电路400的电路装置450的电路图。电路400可以是具有包括高侧功率开关的第一晶体管402的所谓的“高侧”电路,并且电路400可以针对多个led中的单个led短路提供高侧短路保护。

49.如图4所示,led模块401可以包括形成串联布置的led串432的多个led。此外,led模块401可以包括位于其输入和led串432之间的限流电阻器430。电路400可以被配置为当提供针对与led串432内的单个led相关联的单个led短路的短路保护时,控制从电压源到led模块401中的led串432的电压。

50.电路400包括:第一电引脚406(也称为“输入引脚”),被配置为被电气地连接到电压源;以及第二电引脚408(也称为“输出引脚”),被配置为被电气地连接到led模块401内的led串432。在该配置中,第二电引脚408可以包括第一输出引脚,并且第二输出引脚409也可以被用于将led模块401电气地耦合到电路400,其中两个输出引脚408和409被连接到限流电阻器430的相对侧上。与本文描述的其它示例一样,电压源可以包括dc至dc功率转换器或通常被用于驱动led的另一个电压源。术语“vbatt”通常表示与第一电引脚406相关联的节

点上的输入电压。术语“vload”通常表示与第二电引脚408相关联的节点上的输出电压,该第二电引脚408可以被电气地耦合到led模块401内的led串432。此外,限流电阻器430可以被放置在led模块401上、在led与电路400的第二电引脚408之间。

51.电路400包括第一晶体管402,该第一晶体管402被电气地耦合到第一电引脚406和第二电引脚408。第一晶体管402在图4中也被标记为t1。第一晶体管402可以包括功率开关,该功率开关被配置为限定从耦合到第一电引脚406的电压源到耦合到输出引脚408的led模块401内的led串432的负载电流路径。在一些示例中,第一晶体管402可以包括pmos晶体管,这对于负载电流路径来说可以是具有成本效益的功率开关设计。然而,在其它示例中,其它类型的晶体管也可以被用于第一晶体管402。

52.电路400还包括第一晶体管404,该第一晶体管404被电气地耦合到第一电引脚406和第二电引脚408并且与第一晶体管402并联放置。换句话说,第一电阻器404和通过第一晶体管402的负载电流路径是并联的电气路径。第一电阻器404限定了从第一电引脚406到第二电引脚408的高阻抗路径,当第一晶体管402导通时,该高阻抗路径远高于通过第一晶体管402的负载电流路径。在一些示例中,第一电阻器404限定了在50kohms至100kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。

53.如图4所示,第二晶体管414被电气地耦合到第一晶体管402的控制节点(例如,栅极)和参考节点(例如,接地节点)。第二晶体管414在图4中也被标记为t2。在一些示例中,第二晶体管414可以包括nmos晶体管,这对于电路400来说可以是具有成本效益的设计。然而,在其它示例中,其它类型的晶体管也可以被用于第二晶体管414。

54.在电路400中,第二电阻器412被放置在第一电引脚与第一晶体管402的控制节点之间。第二电阻器412可以限定在10kohms至47kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。齐纳二极管422被放置在第二晶体管414的控制节点(例如,栅极)与第二输出引脚409之间,使得齐纳二极管422的正向传导路径被限定为从第二晶体管414的控制节点到led模块401中的led串431。此外,第三电阻器424被放置在第二晶体管414的控制节点与参考节点(例如,接地节点)之间。第三电阻器424可以限定在1kohms至10kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。

55.第二晶体管414被配置为响应于与发光二极管串432内的单个发光二极管相关联的短路事件而关断。短路事件可以导致节点431处的电压升高,从而导致电流反向流动通过齐纳二极管422并且改变第二晶体管414的控制节点处的控制信号。以这种方式,基于led串432内的led上是否存在短路来控制第二晶体管414。如果led模块401内的led中的任何led不存在短路,则第二晶体管414保持导通,该led模块401经由第二电引脚408(即,第一输出引脚)和第二输出引脚409被连接到电路400。如果led串432内的led中的一个led中发生短路事件,则第二晶体管414由于节点431处的电压升高而关断。

56.根据本公开,第一晶体管402被配置为响应于第二晶体管414的关断而关断。以这种方式,响应于与led串432内的单个led相关联的单个短路事件,可以禁用通过第一晶体管402的负载电流路径。led中的一个led上的短路事件导致第二晶体管414关断,这转而导致第一晶体管402关断。以这种方式,电路400包括针对形成led串432的多个led中的单个led内的短路事件的短路保护,这对于led控制来说可能是期望的。当第一晶体管402关断时,从输入引脚406到输出引脚408的低阻抗路径被禁用,并且从输入引脚406到输出引脚408的唯

一电流路径是通过第一电阻器404的高阻抗路径。这可以在一个或多个led中发生短路的情况下,保护电路400和更大系统的其它元件免受损坏或电气故障。

57.对于图4所示的示例,齐纳二极管422被放置在led串432的正极端子与第二晶体管414的栅极之间,以使得能够进行led串432内的单个led短路的检测。在这种情况下,如果负载侧处的电压高于第二晶体管414上的阈值电压加上齐纳二极管422的齐纳电压,则达到并且超过第二晶体管414的阈值。在图4描绘的示例中,如果led串432没有对地短路,则v

led_string

可以是v

led

的三倍。该电压可能需要足够高以将第二晶体管414触发到导通状态。如果led串432内的led中的一个led表现出电短路,则v

led_string

变为v

led

的2倍并且可能没有足够的电压来将第二晶体管414保持在导通状态。当第二晶体管414由于该单个led短路关断时,则第一晶体管402也变成关断状态。以这种方式,可以通过感测第二晶体管414的栅极处的电压来检测单个led短路。

58.与本文描述的其它示例一样,在一些情况下,第一晶体管402可以包括pmos晶体管,并且第二晶体管414可以包括nmos晶体管,这是有成本效益的实现。然而,更一般地,第一晶体管402和第二晶体管414可以各自被实现为场效应晶体管(fet)、双极结型晶体管(bjt)、氮化镓(gan)开关或可能的可控硅整流器(scr)。fet的示例可以包括但不限于结型场效应晶体管(jfet)、金属氧化物半导体fet(mosfet)、双栅极mosfet、绝缘栅双极晶体管(igbt)以及任何其它类型的fet或它们的任何组合。mosfet的示例可以包括但不限于p型金属氧化物半导体(poms)、n型金属氧化物半导体(nmos)、双扩散金属氧化物半导体(dmos)、或其它类型的mosfet或它们的任何组合。bjt的示例可以包括但不限于pnp、npn、异质结或任何其它类型的bjt或它们的任何组合。

59.图5是包括被配置为被连接到led模块501的电路装置550的电路图。图5类似于图4,但不同于图4的电路400,图5的电路500包括附加的引脚(例如,状态引脚516)以提供电路的状态信息。与图4类似,图5示出了示例电路(例如,电路500),示例电路可以被用于控制从电压源到led模块501内的led串的电压。

60.类似于图4的led模块401,图5的led模块501可以包括形成串联布置的led串532的多个led。此外,led模块501可以包括放置在其输入端与led串532之间的限流电阻器530。电路500可以被配置为当提供针对与led串532内的单个led相关联的单个led短路的短路保护时,控制从电压源到led模块501中的led串532的电压。

61.如图5所示,电路500包括:第一电引脚506(也称为“输入引脚”),被配置为被电气地连接到电压源;以及第二电引脚508(也称为“输出引脚”),被配置为被电气地连接到led模块501内的led串532。在该配置中,第二电引脚508可以包括第一输出引脚,并且第二输出引脚509也可以被用于将led模块501电气地耦合到电路500,其中两个输出引脚508和509被连接到限流电阻器530的相对侧。与本文描述的其它示例相同,电压源可以包括dc至dc功率转换器或通常被用于驱动led的另一个电压源。术语“vbatt”通常表示与第一电引脚506相关联的节点上的输入电压。术语“vload”通常表示与第二电引脚508相关联的节点上的输出电压,该第二电引脚508可以被电气地耦合到led模块501内的led串532。限流电阻器530可以被放置在led模块501上、在led与电路500的第二电引脚508之间。

62.电路500包括第一晶体管502,该第一晶体管502被电气地耦合到第一电引脚506和第二电引脚508。第一晶体管502在图5中也被标记为t1,这与本文描述的其它示例一致。第

一晶体管502可以包括功率开关,该功率开关被配置为限定从耦合到第一电引脚506的电压源到耦合到输出引脚508的led模块501内的led串532的负载电流路径。在一些示例中,第一晶体管502可以包括pmos晶体管,这对于负载电流路径来说可能是具有成本效益的功率开关设计。然而,在其它示例中,其它类型的晶体管也可以被用于第一晶体管502。

63.电路500还包括第一电阻器504,该第一电阻器504被电气地耦合到第一电引脚506和第二电引脚508并且与第一晶体管502并联放置。换句话说,第一电阻器504和通过第一晶体管502的负载电流路径是并联的电气路径。第一电阻器504限定了从第一电引脚506到第二电引脚508的高阻抗路径,当第一晶体管502导通时,该高阻抗路径远高于通过第一晶体管502的负载电流路径。在一些示例中,第一电阻器504限定了在50kohms至100kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。

64.如图5所示,第二晶体管514被电气地耦合到第一晶体管502的控制节点(例如,栅极)和参考节点(例如,接地节点)。第二晶体管514在图5中也被标记为t2。在一些示例中,第二晶体管514可以包括nmos晶体管,这对于电路500来说可以是具有成本效益的设计。然而,在其它示例中,其它类型的晶体管也可以被用于第二晶体管514。

65.在电路500中,第二电阻器512被放置在第一电引脚与第一晶体管502的控制节点之间。第二电阻器512可以限定在10kohms至47kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。齐纳二极管522被放置在第二晶体管514的控制节点(例如,栅极)与第二输出引脚509之间,使得齐纳二极管522的正向传导路径被限定为从第二晶体管514的控制节点到led模块501中的led串531。另外,第三电阻器524被放置在第二晶体管514的控制节点与参考节点(例如,接地节点)之间。第三电阻器524可以限定在1kohms至10kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。

66.第二晶体管514被配置为响应于与发光二极管串532内的单个发光二极管相关联的短路事件而关断。短路事件可以导致节点531处的电压升高,从而导致电流反向流动通过齐纳二极管522并且改变第二晶体管514的控制节点处的控制信号。以这种方式,基于led串532内的led上是否存在短路来控制第二晶体管514。如果在led模块501内的led中的任何led不存在短路,则第二晶体管514保持导通,该led模块501经由第二电引脚508(即,第一输出引脚)和第二输出引脚509被连接到电路500。如果在led串532内的led中的一个led中发生短路事件,则第二晶体管514由于节点531处的电压升高而关断。

67.根据本公开,第一晶体管502被配置为响应于第二晶体管514的关断而关断。以这种方式,可以响应于与led串532内的单个led相关联的单个短路事件禁用通过第一晶体管502的负载电流路径。led中的一个led上的短路事件导致第二晶体管514关断,这转而导致第一晶体管502关断。以这种方式,电路500包括针对形成led串532的多个led中的单个led内的短路事件的短路保护,这对于led控制而言可能是合乎需要的。当第一晶体管502关断时,从输入引脚506到输出引脚508的低阻抗路径被禁用,并且从输入引脚506到输出引脚508的唯一电流路径是通过第一电阻器504的高阻抗路径。这可以在一个或多个led中发生短路的情况下,保护电路500和更大系统的其它元件免受损坏或电气故障。

68.对于图5所示的示例电路500,在启动时,如果在led串532中不存在对地短路,则第一电阻器504利用有限的电流偏置输出。如果不存在短路,则led串532的正向电压足够高以克服齐纳二极管522并且将第二晶体管514触发到导通状态,这偏置第一晶体管502并且为

通过第一晶体管502的负载电流路径创建低欧姆状态。如果led串532内的一个led被短路,则齐纳二极管522的阴极上的电压不足以维持第二晶体管514的栅极上的电压,这导致第二晶体管514处于关断状态,从而迫使第一晶体管502到关断状态。类似于上述其它示例,可能发生一些电流泄漏,但是该电流泄漏通常被限于r1/v

batt

,对于(诸如机动车辆设置或电动车辆设置中)led照明情况,这可以是可接受的电流泄漏量。

69.与本文描述的其它示例一样,在一些情况下,第一晶体管502可以包括pmos晶体管,并且第二晶体管514可以包括nmos晶体管,这是具有成本效益的实现。然而,更一般地,第一晶体管502和第二晶体管514可以各自使用(诸如,上面提到的那些)其它类型的晶体管来实现。

70.与图4中电路400的示例不同,图5中所示的电路500还包括状态引脚516,该状态引脚516被电气地耦合到第一晶体管502的控制节点(例如,栅极)。状态引脚516被配置为限定用于使用控制单元的电路的状态信号。例如,控制单元可以包括微处理器,该微处理器将控制信号传递到dc至dc转换器,该dc至dc转换器限定连接到输入引脚506的电压源。状态引脚516上的状态信号可以与控制第一晶体管502的信号相同。因此,导致第一晶体管502关断的信号也可以被用作状态引脚516上的状态信号以向连接到状态引脚516的外部控制单元报告短路事件。在一些低成本的短路保护解决方案中,图4中所示的示例可能比图5所示的示例是更需要的,其中电路中的引脚的数目是成本问题,而当需要向外部控制单元报告任何短路事件时,图5中所示的示例可能比图4的示例是更需要的。

71.图6是示出类似于图5的电路装置并且包括另一个附加的电路引脚和一些附加的电气元件以促进电路的附加的控制的图。与图4和图5相似,图6示出了示例电路(例如,电路600),该示例电路可以被用于控制从电压源到led模块601内的led串的电压。

72.图6的led模块601可以包括形成串联布置的led串632的多个led。此外,led模块601可以包括被放置在其输入与led串632之间的限流电阻器630。电路600可以被配置为当提供针对与led串632内的单个led相关联的单个led短路的短路保护时,控制从电压源到led模块601中的led串632的电压。

73.如图6所示,电路600包括第一电引脚606(也称为“输入引脚”)和第二电引脚608(也称为“输出引脚”),第一电引脚606被配置为被电气地连接到电压源,第二电引脚608被配置为被电气地连接到led模块601内的led串632。在该配置中,第二电引脚608可以包括第一输出引脚,并且第二输出引脚609也可以被用于将led模块601电气地耦合到电路600,其中两个输出引脚608和609被连接到限流电阻器630的相对侧。与本文描述的其它示例一样,电压源可以包括dc至dc功率转换器或通常被用于驱动led的另一个电压源。此外,术语“vbatt”通常表示与第一电引脚606相关联的节点上的输入电压,并且术语“vload”通常表示与第二电引脚608相关联的节点上的输出电压。限流电阻器630可以被放置在led模块601上、在led和电路600的第二电引脚608之间。

74.电路600包括第一晶体管602,第一晶体管602被电气地耦合到第一电引脚606和第二电引脚608。第一晶体管602在图6中也被标记为t1,这与本文描述的其它示例一致。第一晶体管602可以包括功率开关,该功率开关被配置为限定从耦合到第一电引脚606的电压源到耦合到输出引脚608的led模块601内的led串632的负载电流路径。在一些示例中,第一晶体管602可以包括pmos晶体管,这对于负载电流路径来说可以是具有成本效益的功率开关

设计。然而,在其它示例中,其它类型的晶体管也可以被用于第一晶体管602。

75.电路600还包括被电气地耦合到第一电引脚606和第二电引脚608的第一电阻器604,并且与第一晶体管602并联放置。换句话说,第一电阻器604和通过第一晶体管602的负载电流路径是并联的电气路径。第一电阻器604限定了从第一电引脚606到第二电引脚608的高阻抗路径,当第一晶体管602导通时,该高阻抗路径远高于通过第一晶体管602的负载电流路径。在一些示例中,第一电阻器604限定了在50kohms至100kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。

76.如图6所示,第二晶体管614经由第三晶体管628被电气地耦合到第一晶体管602的控制节点(例如,栅极)。第二晶体管614还被连接到参考节点(例如,接地节点)。第二晶体管614在图6中也被标记为t2,并且第三晶体管被标记为t3。在一些示例中,第二晶体管614和第三晶体管628都可以包括nmos晶体管,这对于电路600来说可以是具有成本效益的设计。然而,在其它示例中,其它类型的晶体管也可以被用于第二晶体管614和第三晶体管628。

77.在电路60中,第二电阻器612被放置在第一电引脚与第一晶体管602的控制节点之间。第二电阻器612可以限定在10kohms至47kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。齐纳二极管622被放置在第二晶体管614的控制节点(例如,栅极)与输出引脚609之间,使得齐纳二极管622的正向导电路径被限定为从第二晶体管614的控制节点到led模块601中的led串631。此外,第三电阻器624被放置在第二晶体管614的控制节点与参考节点(例如,接地节点)之间。第三电阻器624可以限定在1kohms至10kohms之间的电阻,尽管在其它示例中可以使用另一个大小的电阻器。

78.第二晶体管614被配置为响应于与发光二极管串632内的单个发光二极管相关联的短路事件而关断。短路事件可以导致节点631处的电压升高,从而导致电流反向流动通过齐纳二极管622,并且改变在第二晶体管614的控制节点处的控制信号。以这种方式,基于led串632内的led上是否存在短路来控制第二晶体管614。如果led模块601内的led中的任何led中不存在短路,则第二晶体管614保持导通,第二晶体管614经由第二电引脚608(即,第一输出引脚)和第二输出引脚609被连接到电路600。如果在led串632内的led中的一个led中发生短路事件,则第二晶体管614由于节点631处电压升高而关断。

79.根据本公开,第一晶体管602被配置为响应于第二晶体管614的关断而关断。以这种方式,响应于与led串632内的单个led相关联的单个短路事件可以禁用通过第一晶体管602的负载电流路径。led中的一个led上的短路事件导致第二晶体管614关断,这转而导致第一晶体管602关断。以这种方式,电路600包括针对形成led串632的多个led中的单个led内的短路事件的短路保护,这对于led控制来说可能是期望的。当第一晶体管602关断时,从输入引脚606到输出引脚608的低阻抗路径被禁用,并且从输入引脚606到输出引脚608的唯一电流路径是通过第一电阻器604的高阻抗路径。这可以在一个或多个led中发生短路的情况下,保护电路600和更大系统的其它元件免受损坏或电气故障。

80.与图4中的电路400的示例不同并且类似于图5的示例电路500,图6中所示的电路600还包括状态引脚616,该状态引脚616被电气地耦合到第一晶体管602的控制引脚(例如,栅极)。状态引脚616被配置为限定用于使用控制单元的电路的状态信号。例如,控制单元可以包括微处理器,该微处理器将控制信号传递到dc至dc转换器,该dc至dc转换器限定连接到输入引脚606的电压源。状态引脚616上的状态信号可以与控制第一晶体管602的信号相

同。因此,使第一晶体管602关断的信号也可以被用作状态引脚616上的状态信号,以向连接到状态引脚616的外部控制单元报告短路事件。

81.如上所述(并且与图4的电路400和图5的电路500不同),电路600还包括第三晶体管628,第三晶体管628被放置在第二晶体管与第一晶体管的控制节点之间。此外,电路600包括控制引脚628,控制引脚628被配置为将来自控制电路的控制信号提供给第三晶体管628的控制节点。第四电阻器620被放置在控制引脚618与第三晶体管628的控制节点之间。在该装置中,第三晶体管628可以被配置为响应于来自控制电路的控制信号而关断。在这种情况下,第一晶体管628还被配置为响应于第三晶体管628的关断而关断。因此,第二晶体管614和第三晶体管628可以被配置为形成用于控制第一晶体管602的与门,使得第一晶体管602响应于第二晶体管614和第三晶体管628两者限定“on”状态来限定“on”状态。

82.如上所示,元件606可以包括第一电引脚并且元件608可以包括第二电引脚。状态引脚616可以包括第三电引脚,例如,被耦合到第一晶体管602的控制节点并且被配置为限定用于由控制单元使用的电路600的状态信号。此外,第三晶体管628被放置在第二晶体管614与第一晶体管602的控制节点之间。控制引脚618可以包括第四电引脚,第四电引脚被配置为将来自控制电路的控制信号提供给第三晶体管628的控制节点,并且第四电阻器620可以被放置在第四电引脚(例如,控制引脚618)与第三晶体管628的控制节点之间。第三晶体管628被配置为响应于来自控制电路的控制信号而关断并且第一晶体管602被配置为响应于第三晶体管628的关断而关断。第二晶体管614和第三晶体管628可以被配置为形成用于控制第一晶体管602的与门,使得第一晶体管602响应于第二晶体管614和第三晶体管628两者限定“on”状态来限定“on”状态。

83.对于图6中所示的示例电路600,在启动时,如果led串632中不存在对地短路,则第一电阻器604偏置具有有限的电流输出。如果不存在短路,则led串632的正向电压足够高以克服齐纳二极管622并且将第二晶体管614触发到导通状态。如果控制信号从外部控制单元被施加到控制端子618以将第三晶体管628转变为导通状态,则第二晶体管614和第三晶体管628被允许偏置第一晶体管602,以导致第一晶体管602导通,并且从而为通过电路600的负载电流路径创建低欧姆路径。然而,如果一个led表现出电短路,则齐纳二极管622的阴极上的电压可能不足以克服齐纳二极管622以维持第二晶体管614的栅极上的电压。当第二晶体管614的栅极处的电压变为大约0v时,由于led串632内的一个led中的电短路,这迫使第一晶体管602处于关断状态,从而保护电路免受电短路的影响。可能发生一些电流泄漏,但是该电流泄漏通常被限于r1/v

batt

,对于(诸如机动车辆设置或电动车辆设置中)led照明情况,这可以是可接受的电流泄漏量。

84.图7是与由于本公开一致的电路(诸如,电路100、200、300、400、500或600)执行的技术一致的流程图。如图7所示,该方法包括经由包括第一晶体管(t1)的电路(例如,电路100、200、300、400、500或600)控制从电压源到一个或多个发光二极管的电压,第一晶体管(t1)包括被配置为限定从电压源到一个或多个发光二极管(701)的负载电流路径的功率开关。该电路还基于发光二极管控制第二晶体管(t2)的控制节点,其中第二晶体管(t2)被配置为当发光二极管中的一个或多个发光二极管表现出电短路(702)时关断。此外,该电路控制第一晶体管(t1)的控制节点,使得第一晶体管被配置为响应于第二晶体管的关断而关断。

85.在一些(诸如,具有电路200、300、500或600的)示例中,图7中所示的方法还可以包括基于第一晶体管(t1)的控制节点提供电路的状态指示。在一些(诸如,具有电路300或600的)示例中,图7中所示的方法还可以包括接收从控制电路到第二晶体管(t2)的控制节点的控制信号,其中第二晶体管(t2)还被配置为响应于来自控制电路的控制信号或响应于表现出电短路的一个或多个发光二极管而关断。

86.在一些(诸如,具有电路600的)示例中,电路可以包括第三晶体管(t3),第三晶体管(t3)被放置在第二晶体管(t2)与第一晶体管(t1)的控制节点之间,并且该方法还可以包括在第三晶体管(t3)处接收控制信号,其中第三晶体管(t3)还被配置为响应于来自控制电路的控制信号而导通或关断,并且其中第一晶体管(t1)被配置为响应于第三晶体管(t3)的关断而关断。在这种(与图6的电路配置一致的)情况下,第二晶体管(t2)和第三晶体管(t3)可以形成用于控制第一晶体管(t1)的与门,使得第一晶体管(t1)响应于第二和第三晶体管(t2和t3)两者限定“on”状态来限定“on”状态。

87.在其它(诸如,具有电路400、500或600中的任一个电路的)示例中,一个或多个发光二极管可以包括发光二极管串,并且其中电短路包括与发光二极管串内的一个发光二极管相关联的单个短路。齐纳二极管(例如,422、522或622)的存在可以促进检测led串内的单个led短路的能力。

88.以下示例可以说明本公开的一个或多个方面。

89.示例1.一种被配置为控制从电压源到一个或多个发光二极管的电压的电路,电路包括:第一电引脚,被配置为被电气地连接到电压源;第二电引脚,被配置为被电气地连接到一个或多个发光二极管;第一晶体管,被电气地耦合到第一电引脚和第二电引脚,其中第一晶体管包括功率开关,该功率开关被配置为限定从电压源到一个或多个发光二极管的负载电流路径;第一电阻器,被电气地耦合到第一电引脚和第二电引脚,并且与负载电流路径并联放置;第二晶体管,被电气地耦合到参考节点和第一晶体管的控制节点,其中第二晶体管的控制节点被电气地耦合到第二电引脚;以及第二电阻器,被放置在第一电引脚与第一晶体管的控制节点之间,其中第二晶体管被配置为响应于一个或多个发光二极管中的短路事件而关断,以及其中第一晶体管被配置为响应于第二晶体管的关断而关断。

90.示例2.根据示例1所述的电路,还包括:状态引脚,被电气地耦合到第一晶体管的控制节点,其中状态引脚被配置为限定电路的、用于使用控制单元的状态信号。

91.示例3.根据示例1或2所述的电路,还包括:二极管,被放置在第二晶体管的控制节点与第二电引脚之间,使得二极管的正向传导路径被限定为从第二晶体管的控制节点到第二电引脚;控制引脚,被配置为将来自控制电路的控制信号提供给第二晶体管的控制节点;以及第三电阻器,被放置在控制引脚与第二晶体管的控制节点之间,其中第二晶体管还被配置为响应于来自控制电路的控制信号而关断。

92.示例4.根据示例1所述的电路,还包括:第三电引脚,被电气地耦合到第一晶体管的控制节点,其中第三电引脚被配置为限定电路的、用于由控制单元使用的状态信号;二极管,被放置在第二晶体管的控制节点与第二电引脚之间,使得二极管的正向传导路径被限定为从第二晶体管的控制节点到第二电引脚;第四电引脚,被配置为将来自控制电路的控制信号提供给第二晶体管的控制节点;以及第三电阻器,被放置在第四电引脚与第二晶体管的控制节点之间,其中第二晶体管还被配置为响应于来自控制电路的控制信号而关断。

93.示例5.根据示例1至4中的任一项所述的电路,其中:第一晶体管包括p型金属氧化物半导体(pmos)晶体管;并且第二晶体管包括n型金属氧化物半导体(nmos)晶体管。

94.示例6.一种被配置为控制从电压源到发光二极管串的电压的电路,电路包括:第一电引脚,被配置为被电气地连接到电压源;第二电引脚,被配置为被电气地连接到发光二极管串;第一晶体管,被电气地耦合到第一电引脚和第二电引脚,其中第一晶体管包括功率开关,该功率开关被配置为限定从电压源到发光二极管串的负载电流路径;第一电阻器,被电气地耦合到第一电引脚和第二电引脚,并且与负载电流路径并联放置;第二晶体管,被电气地耦合到参考节点和第一晶体管的控制节点,其中第二晶体管的控制节点被电气地耦合到第二电引脚;第二电阻器,被放置在第一电引脚与第一晶体管的控制节点之间,齐纳二极管,被放置在第二电引脚与第二晶体管的控制节点之间,使得二极管的正向导电路径被限定为从第二晶体管的控制节点到发光二极管串;以及第三电阻器,被放置在参考节点与第二晶体管的控制节点之间,其中第二晶体管被配置为响应于与发光二极管串内的单个发光二极管相关联的短路事件而关断,以及其中第一晶体管被配置为响应于第二晶体管的关断而关断。

95.示例7.根据示例6所述的电路,还包括:状态引脚,被电气地耦合到第一晶体管的控制节点,其中状态引脚被配置为限定电路的、用于由控制单元使用的状态信号。

96.示例8.根据示例6或7所述的电路,还包括:第三晶体管,被放置在第二晶体管与第一晶体管的控制节点之间;控制引脚,被配置为将来自控制电路的控制信号提供给第三晶体管的控制节点;以及第四电阻器,被放置在控制引脚与第三晶体管的控制节点之间,其中第三晶体管还被配置为响应于来自控制电路的控制信号而关断,并且其中第一晶体管被配置为响应于第三晶体管的关断而关断。

97.示例9.根据示例8所述的电路,其中第二晶体管和第三晶体管形成用于控制第一晶体管的与门,使得第一晶体管响应于第二晶体管和第三晶体管两者限定“on”状态来限定“on”状态。

98.示例10.根据示例8所述的电路,还包括:第三电引脚,被电气地耦合到第一晶体管的控制节点,其中第三电引脚被配置为限定电路的、用于由控制单元使用的状态信号;第三晶体管,被放置在第二晶体管与第一晶体管的控制节点之间;第四电引脚,被配置为将来自控制电路的控制信号提供给第三晶体管的控制节点;以及第四电阻器,被放置在第四电引脚与第三晶体管的控制节点之间,其中第三晶体管还被配置为响应于来自控制电路的控制信号而关断,并且其中第一晶体管被配置为响应于第三晶体管的关断而关断。

99.示例11.根据示例10所述的电路,其中第二晶体管和第三晶体管形成用于控制第一晶体管的与门,使得第一晶体管响应于第二晶体管和第三晶体管两者限定“on”状态来限定“on”状态。

100.示例12.根据示例6至10中的任一项所述的电路,其中:第一晶体管包括p型金属氧化物半导体(pmos)晶体管;并且第二晶体管包括n型金属氧化物半导体(nmos)晶体管。

101.示例13.一种方法,包括:经由电路控制从电压源到一个或多个发光二极管的电压,该电路包括第一晶体管,第一晶体管包括功率开关,功率开关被配置为限定从电压源到一个或多个发光二极管的负载电流路径;基于发光二极管控制第二晶体管的控制节点,其中第二晶体管被配置为当发光二极管中的一个或多个发光二极管表现出电短路时关断;以

及控制第一晶体管的控制节点,使得第一晶体管被配置为响应于第二晶体管的关断而关断。

102.示例14.根据示例13所述的方法,还包括:基于第一晶体管的控制节点提供电路的状态指示。

103.示例15.根据示例13或14所述的方法,还包括:接收从控制电路到第二晶体管的控制节点的控制信号,其中第二晶体管还被配置为响应于来自控制电路的控制信号或响应于一个或多个发光二极管表现出电短路而关断。

104.示例16.根据示例13或14所述的方法,还包括:在第三晶体管处接收控制信号,第三晶体管被放置在第二晶体管与第一晶体管的控制节点之间,其中第三晶体管还被配置为响应于来自控制电路的控制信号而导通或关断,并且其中第一晶体管被配置为响应于第三晶体管的关断而关断。

105.示例17.根据示例16所述的方法,其中第二晶体管和第三晶体管形成用于控制第一晶体管的与门,使得第一晶体管响应于第二晶体管和第三晶体管两者限定“on”状态来限定“on”状态。

106.示例18.根据示例13所述的方法,其中一个或多个发光二极管包括发光二极管串,并且其中电短路包括与发光二极管串内的一个发光二极管相关联的单个短路。

107.在本公开中已经描述了各个方面。这些方面和其它方面在以下权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1