MRAM器件及其制作方法与流程

本技术涉及半导体结构,具体而言,涉及一种mram器件及其制作方法。

背景技术:

1、磁性随机存储器(mram)具有读写速度快,功耗低、高密度以及可与cmos工艺集成等特点,是极具潜力的新型存储器。磁性隧道结(mtj)是mram芯片的核心单元,其主要由磁性自由层,绝缘层和磁性参考层组成,一个mtj称之为一个位元。磁性自由层可以通过磁场或者自旋极化电流改变状态,磁性自由层与参考层的相对关系(平行态/反平行态)决定了位元的电阻高低,从而存储“0”或者“1”信息。

2、现有的mram的结构如图1所示,其中该结构包括阵列区、逻辑区以及dummy区,磁性隧道结集成在后端工艺的两层金属层mx与mx+1连线之间。阵列区主要包括多个层叠的底部金属线mx、底部通孔bv、底部电极be、磁性隧道结mtj、顶部电极te、顶部通孔tv和顶部金属线mx+1。而逻辑区无底部通孔bv,由tv直接连接mx与mx+1。因此,逻辑区通孔高度为mram阵列中顶部通孔高度的至少两倍。例如,传统的mram位元采用一张光罩同时实现逻辑tv和阵列tv的图案化,由于逻辑区和阵列区之间存在上述工艺差异,会引入额外的工艺风险,对工艺稳定性、可靠性及芯片良率造成影响。此外,在现有技术下,mram阵列器件需要底部通孔以及底部电极,从而增加了工艺复杂度和成本,且由于工艺节点的微缩,会造成底部通孔以及底部电极工艺的工艺窗口恶化,很大程度上影响芯片制造良率。

3、在背景技术部分中公开的以上信息只是用来加强对本文所描述技术的背景技术的理解,因此,背景技术中可能包含某些信息,这些信息对于本领域技术人员来说并未形成在本国已知的现有技术。

技术实现思路

1、本技术的主要目的在于提供一种mram器件及其制作方法,以解决现有技术中mram结构的阵列区与逻辑区的工艺差异较大,影响工艺稳定性的问题。

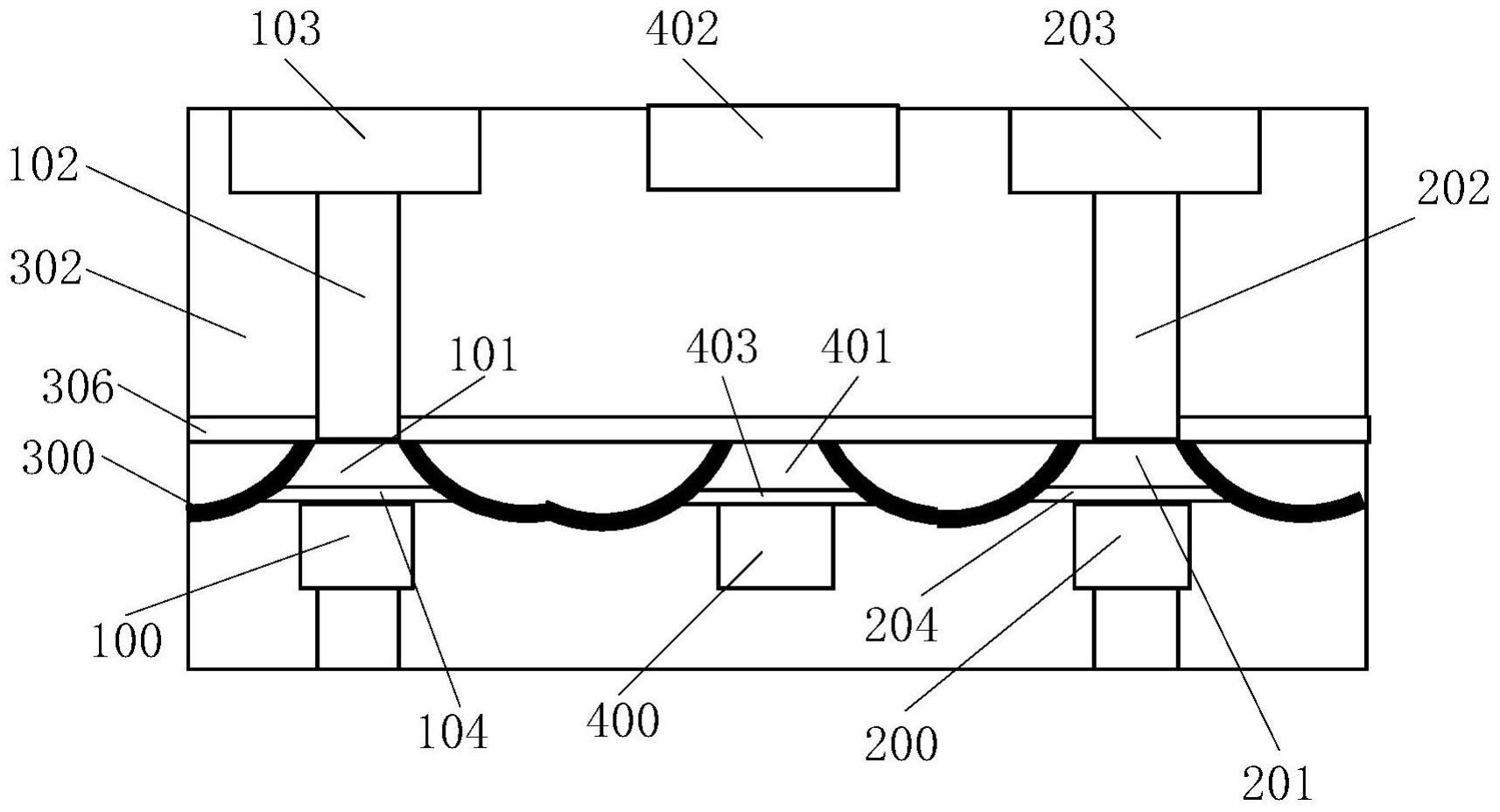

2、根据本技术的一个方面,提供了一种mram器件,包括基底、阵列区以及逻辑区,其中,所述基底包括衬底以及位于所述衬底上的介质层;所述阵列区位于所述介质层中,所述阵列区包括间隔设置的多个阵列器件,所述阵列器件包括依次叠置的第一金属线、第一mtj、第一通孔以及第二金属线;所述逻辑区位于所述介质层中且位于所述阵列区的外围,所述逻辑区包括多个互连结构,所述互连结构包括依次叠置的第三金属线、第二mtj、第二通孔以及第四金属线,其中,所述阵列器件与所述互连结构同时形成,所述第二mtj的面积大于或者等于预定阈值。

3、可选地,所述阵列区还包括多个第一缓冲层,所述第一缓冲层位于所述第一金属线与所述第一mtj之间,所述逻辑区还包括多个第二缓冲层,所述第二缓冲层位于所述第三金属线与所述第二mtj之间。

4、可选地,所述第一金属线的靠近所述第一mtj的表面为第一表面,所述第一缓冲层的靠近所述第一金属线的表面为第二表面,所述第二表面的面积大于所述第一表面的面积;所述第三金属线的靠近所述第二mtj的表面为第三表面,所述第二缓冲层的靠近所述第三金属线的表面为第四表面,所述第四表面的面积大于所述第三表面的面积。

5、可选地,所述第一mtj的靠近所述第一金属线的表面为第五表面,所述第一金属线的靠近所述第一mtj的表面为第一表面,所述第五表面大于所述第一表面;所述第二mtj的靠近所述第三金属线的表面为第六表面,所述第三金属线的靠近所述第二mtj的表面为第三表面,所述第六表面大于所述第三表面。

6、可选地,所述阵列区还包括多个第一电极,所述第一电极位于所述第一mtj的远离所述第一金属线的表面上,所述逻辑区还包括多个第二电极,所述第二电极位于所述第二mtj的远离所述第三金属线的表面上。

7、可选地,所述mram器件还包括保护结构,所述保护结构位于所述第一mtj以及所述第一通孔之间,所述保护结构还位于所述第二mtj以及所述第二通孔之间,且所述保护结构覆盖各所述第一mtj的裸露表面以及各所述第二mtj的裸露表面。

8、可选地,所述mram器件还包括刻蚀停止结构,所述刻蚀停止结构位于所述保护结构与所述第一通孔之间,所述刻蚀停止结构还位于所述保护结构与所述第二通孔之间。

9、可选地,所述逻辑区还包括多个虚拟器件,所述虚拟器件包括叠置的第五金属线以及第三mtj,所述虚拟器件还包括第六金属线,所述第六金属线位于所述第三mtj的远离所述第五金属线的一侧。

10、根据本技术的另一方面,还提供了一种mram器件的制作方法,包括:提供基底,所述基底包括衬底以及位于所述衬底的裸露表面上的第一介质子层,所述第一介质子层包括多个第一金属线以及多个第三金属线;在所述第一金属线的裸露表面上形成第一mtj,且在所述第三金属线的裸露表面上形成第二mtj,所述第二mtj的面积大于或者等于预定阈值;在形成有所述第一mtj以及所述第二mtj的所述基底的裸露表面上形成第二介质子层;至少在所述第二介质子层中形成多个第一通孔、多个第二金属线、多个第二通孔以及多个第四金属线,所述第二金属线位于所述第一mtj的远离所述第一金属线的一侧,所述第一通孔位于所述第二金属线与所述第一mtj之间,所述第四金属线位于所述第二mtj的远离所述第三金属线的一侧,所述第二通孔位于所述第四金属线与所述第二mtj之间。

11、可选地,在所述第一金属线的裸露表面上形成第一mtj,且在所述第三金属线的裸露表面上形成第二mtj,包括:在所述基底的裸露表面上依次形成预备缓冲层、mtj堆叠层以及第一掩膜层;以所述第一掩膜层为掩膜,依次刻蚀所述mtj堆叠层以及所述预备缓冲层,得到多个层叠的第一缓冲层以及所述第一mtj,以及多个层叠的第二缓冲层以及所述第二mtj。

12、可选地,在所述第一金属线的裸露表面上形成第一mtj,且在所述第三金属线的裸露表面上形成第二mtj,包括:在所述基底的裸露表面上依次形成预备缓冲层以及第二掩膜层;以所述第二掩膜层为掩膜,刻蚀所述预备缓冲层,得到多个第一缓冲层和多个第二缓冲层;在所述第一缓冲层的裸露表面上、所述第二缓冲层的裸露表面上以及所述基底的裸露表面上沉积介质材料;对形成有所述介质材料的所述基底进行平坦化,使得所有的所述第一缓冲层以及所有的所述第二缓冲层裸露,得到中间结构;在所述中间结构的裸露表面上依次形成mtj堆叠层以及第三掩膜层;以所述第三掩膜层为掩膜,刻蚀所述mtj堆叠层,得到多个所述第一mtj以及多个所述第二mtj。

13、可选地,所述第一金属线的靠近所述第一mtj的表面为第一表面,所述第一缓冲层的靠近所述第一金属线的表面为第二表面,所述第二表面的面积大于所述第一表面的面积;所述第三金属线的靠近所述第二mtj的表面为第三表面,所述第二缓冲层的靠近所述第三金属线的表面为第四表面,所述第四表面的面积大于所述第三表面的面积。

14、可选地,在所述第一金属线的裸露表面上形成第一mtj,且在所述第三金属线的裸露表面上形成第二mtj之后,在形成有所述第一mtj以及所述第二mtj的所述基底的裸露表面上形成第二介质子层之前,所述方法还包括:在所述第一缓冲层、所述第一mtj、所述第二缓冲层、所述第二mtj以及所述基底的裸露表面上依次沉积保护材料以及介质材料;对形成有所述保护材料以及所述介质材料的所述基底进行平坦化,以使得所述保护材料的部分裸露,剩余的所述保护材料形成保护结构,剩余的介质材料形成第三介质层。

15、可选地,在对形成有所述保护材料以及所述介质材料的所述基底进行平坦化,以使得所述保护材料的部分裸露之后,所述方法还包括:在形成有所述第三介质层以及所述保护结构的所述基底的裸露表面上形成刻蚀停止结构。

16、可选地,至少在所述第二介质子层中形成多个第一通孔、多个第二金属线、多个第二通孔以及多个第四金属线,包括:在所述第二介质子层中依次形成贯穿至所述第一mtj表面的所述第一通孔以及所述第二金属线,同时在所述第二介质子层中依次形成贯穿至所述第二mtj表面的所述第二通孔以及所述第四金属线。

17、可选地,在所述第一金属线的裸露表面上形成第一mtj,且在所述第三金属线的裸露表面上形成第二mtj之后,在形成有所述第一mtj以及所述第二mtj的所述基底的裸露表面上形成第二介质子层之前,所述方法还包括:在所述第一mtj的远离所述第一金属线的表面上依次形成第一电极以及第一刻蚀停止层,同时在所述第二mtj的远离所述第三金属线的表面上依次形成第二电极以及第二刻蚀停止层。

18、可选地,所述基底还包括多个第五金属线,在所述第一金属线的裸露表面上形成第一mtj,且在所述第三金属线的裸露表面上形成第二mtj,还包括:在所述第一金属线的裸露表面上形成所述第一mtj的同时,在所述第三金属线的裸露表面上形成所述第二mtj,且在所述第五金属线的裸露表面上形成第三mtj,至少在所述第二介质子层中形成多个第一通孔、多个第二金属线、多个第二通孔以及多个第四金属线,包括:在所述第二介质子层中形成多个所述第一通孔、多个所述第二金属线、多个所述第二通孔、多个所述第四金属线以及多个第六金属线,所述第六金属线位于所述第三mtj的远离所述第五金属线的一侧,所述第五金属线与所述第一金属线同时形成,所述第六金属线与所述第二金属线同时形成。

19、应用本技术的技术方案,所述的mram器件中,阵列区的每个阵列器件均包括依次叠置的第一金属线、第一mtj、第一通孔以及第二金属线,逻辑区的多个互连结构均包括依次叠置的第三金属线、第二mtj、第二通孔以及第四金属线,且所述阵列器件与所述互连结构同时形成。相比现有的mram结构的阵列区与逻辑区的工艺差异较大,影响工艺稳定性的问题,本技术的所述的mram器件中,阵列器件与互连结构的结构相同,均包括叠置的金属线、mtj、通孔以及金属线,保证了阵列区域与逻辑区域之间的工艺差异较小,从而保证了mram结构的工艺稳定性较好。并且,与现有技术相比,本技术的mram器件的阵列器件中可以直接在所述第一金属线上形成所述第一mtj,这样避免了工艺节点微缩造成的底部通孔以及底部电极工艺的工艺窗口恶化,保证了所述第一金属线以及所述第二金属线之间的高度较低,保证了所述第三金属线以及所述第四金属线之间的高度较低,保证了工艺可靠性较好,同时该阵列器件无需底部通孔以及底部电极,保证了mram器件的制作工艺较为简单,保证了工艺效率较高以及工艺成本较低。

- 还没有人留言评论。精彩留言会获得点赞!