半导体元件及其制作方法与流程

本发明涉及一种制作半导体元件,尤其是涉及一种制作磁阻式随机存取存储器(magnetoresistive random access memory,mram)元件的方法。

背景技术:

1、已知,磁阻(magnetoresistance,mr)效应是材料的电阻随着外加磁场的变化而改变的效应,其物理量的定义,是在有无磁场下的电阻差除上原先电阻,用以代表电阻变化率。目前,磁阻效应已被成功地运用在硬盘生产上,具有重要的商业应用价值。此外,利用巨磁电阻物质在不同的磁化状态下具有不同电阻值的特点,还可以制成磁性随机存储器(mram),其优点是在不通电的情况下可以继续保留存储的数据。

2、上述磁阻效应还被应用在磁场感测(magnetic field sensor)领域,例如,移动电话中搭配全球定位系统(global positioning system,gps)的电子罗盘(electroniccompass)零组件,用来提供使用者移动方位等信息。目前,市场上已有各式的磁场感测技术,例如,各向异性磁阻(anisotropic magnetoresistance,amr)感测元件、巨磁阻(gmr)感测元件、磁隧穿结(magnetic tunneling junction,mtj)感测元件等等。然而,上述现有技术的缺点通常包括:较占芯片面积、制作工艺较昂贵、较耗电、灵敏度不足,以及易受温度变化影响等等,而有必要进一步改进。

技术实现思路

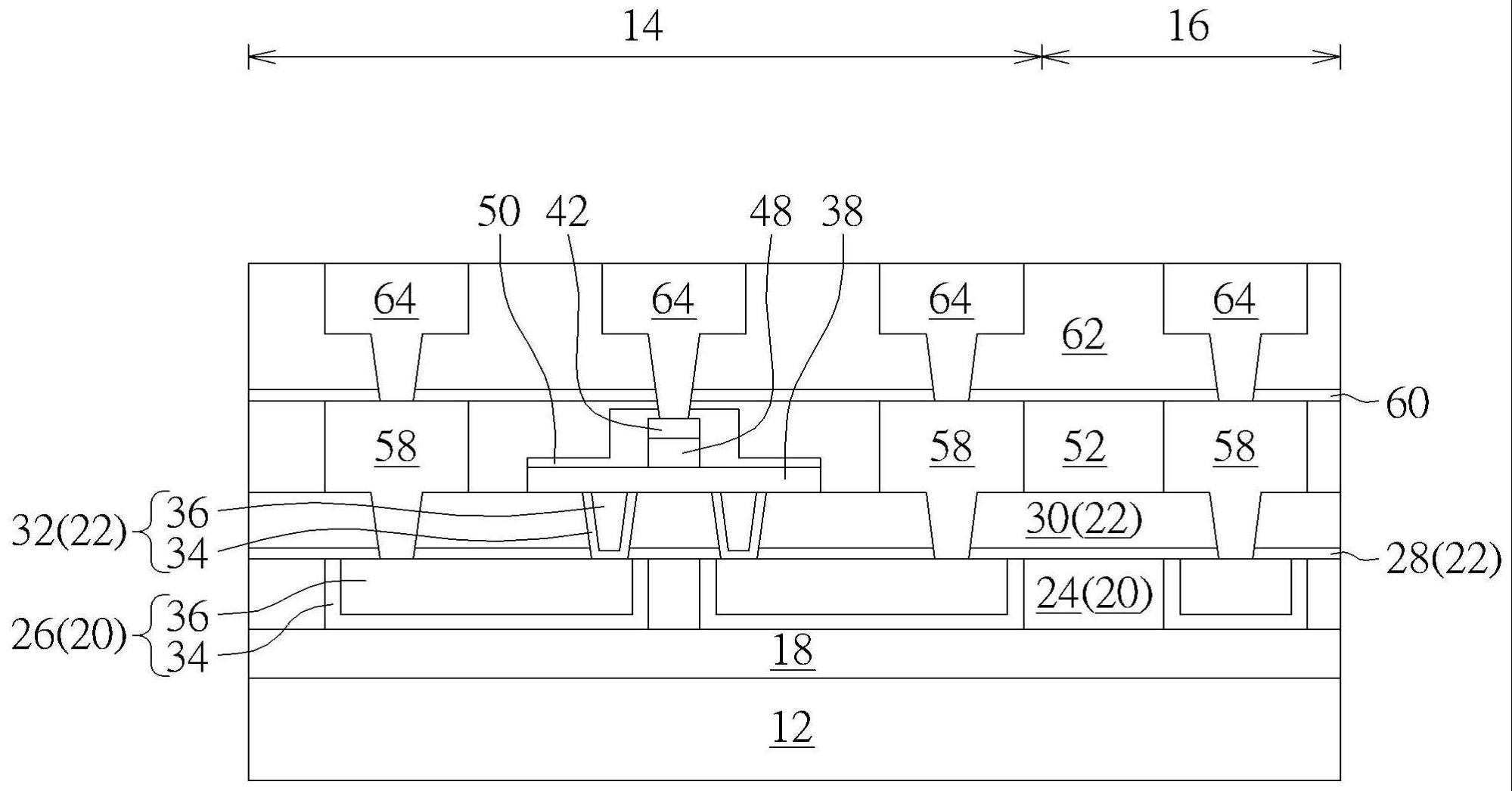

1、本发明一实施例公开一种制作半导体元件的方法,其主要先提供一包含mram区域与逻辑区域的基底,然后形成第一金属间介电层于基底上,形成第一金属内连线与第二金属内连线于mram区域的第一金属间介电层内,形成一自旋轨道转矩式(spin orbittorque,sot)层于第一金属内连线与第二金属内连线上,形成一磁性隧穿结(magnetictunneling junction,mtj)堆叠结构于sot层上,形成一硬掩模于mtj堆叠结构上,利用该硬掩模图案化mtj堆叠结构以形成mtj,形成一遮盖层于sot层与硬掩模上,再图案化遮盖层以及sot层。

2、本发明一实施例公开一种半导体元件,其主要包含一自旋轨道转矩式(spinorbit torque,sot)层设于一基底上,一磁性隧穿结(magnetic tunneling junction,mtj)设于sot层上,一硬掩模设于mtj上以及一遮盖层设于sot层以及mtj上。

技术特征:

1.一种制作半导体元件的方法,其特征在于,包含:

2.如权利要求1所述的方法,其中该基底包含mram区域以及逻辑区域,该方法包含:

3.如权利要求2所述的方法,另包含于图案化该遮盖层以及该自旋轨道转矩式层之前进行蚀刻制作工艺去除部分该遮盖层。

4.如权利要求2所述的方法,另包含:

5.如权利要求4所述的方法,其中该遮盖层顶表面低于该第三金属内连线顶表面。

6.如权利要求4所述的方法,另包含:

7.如权利要求2所述的方法,其中该自旋轨道转矩式层上的该遮盖层以及该磁性隧穿结旁的该遮盖层包含不同厚度。

8.如权利要求2所述的方法,其中该自旋轨道转矩式层上的该遮盖层厚度小于该磁性隧穿结旁的该遮盖层厚度。

9.如权利要求1所述的方法,其中该遮盖层侧壁切齐该自旋轨道转矩式层侧壁。

10.一种半导体元件,其特征在于,包含:

11.如权利要求10所述的半导体元件,其中该基底包含mram区域以及逻辑区域,该半导体元件包含:

12.如权利要求11所述的半导体元件,另包含:

13.如权利要求11所述的半导体元件,其中该遮盖层顶表面低于该第三金属内连线顶表面。

14.如权利要求11所述的半导体元件,其中该自旋轨道转矩式层上的该遮盖层以及该磁性隧穿结旁的该遮盖层包含不同厚度。

15.如权利要求11所述的半导体元件,其中该自旋轨道转矩式层上的该遮盖层厚度小于该磁性隧穿结旁的该遮盖层厚度。

16.如权利要求10所述的半导体元件,其中该遮盖层侧壁切齐该自旋轨道转矩式层侧壁。

技术总结

本发明公开一种半导体元件及其制作方法,其中该制作半导体元件的方法为先提供一包含MRAM区域与逻辑区域的基底,然后形成第一金属间介电层于基底上,形成第一金属内连线与第二金属内连线于MRAM区域的第一金属间介电层内,形成一自旋轨道转矩式(spin orbit torque,SOT)层于第一金属内连线与第二金属内连线上,形成一磁性隧穿结(magnetic tunneling junction,MTJ)堆叠结构于SOT层上,形成一硬掩模于MTJ堆叠结构上,利用该硬掩模图案化MTJ堆叠结构以形成MTJ,形成一遮盖层于SOT层与硬掩模上,再图案化遮盖层以及SOT层。

技术研发人员:林宏展

受保护的技术使用者:联华电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!