模数转换器的制作方法

1.本技术涉及集成电路技术领域,尤其涉及一种模数转换器。

背景技术:

2.随着集成电路产业的迅速发展,模数转换器逐渐向高速度以及低功耗的方向发展。其中,逐次逼近型模数转换器(successive approximation register analog-to-digital converter,sar adc)凭借其制作成本低、延迟小以及精度适中的特点,被广泛地应用于各个集成电路系统中。

3.而如何提高sar adc的模数转换速度成为研究的关键点。

技术实现要素:

4.本技术的实施例提供一种模数转换器,能够提高模数转换器的模数转换速度。

5.为达到上述目的,本技术采用如下技术方案:

6.第一方面,提供了一种模数转换器,其特征在于,包括:采样保持电路、比较器、控制器以及数模转换器;采样保持电路耦合比较器的正相输入端,控制器耦合比较器的输出端以及数模转换器的输入端,数模转换器的输出端耦合比较器的反相输入端;采样保持电路,被配置为接收模拟信号,在第一采样时间段对模拟信号进行采样生成第一模拟采样信号,将第一模拟采样信号传输至比较器的正相输入端;控制器,被配置为获取第一数字信号,将第一数字信号传输至数模转换器的输入端;其中,第一数字信号为第二模拟采样信号对应的数字信号,第二模拟采样信号为采样保持电路在第一采样时间段的前一采样时间段采样生成的模拟采样信号;数模转换器,被配置为将第一数字信号转换为第一模拟参考信号,将第一模拟参考信号传输至比较器的反相输入端;比较器,被配置为比较第一模拟采样信号以及第一模拟参考信号,生成第一比较结果,将第一比较结果传输至控制器;控制器,还被配置为根据第一比较结果以及第一数字信号生成第二数字信号。上述的模数转换器,采样保持电路接收模拟信号,并且采样保持电路在第一采样时间段对模拟信号进行采样生成第一模拟采样信号,将第一模拟采样信号输入至比较器的正相输入端。其中,控制器被配置为获取第一数字信号,该第一数字信号是第二模拟采样信号对应的数字信号,第二模拟采样信号为采样保持电路在第一采样时间段的前一采样时间段采样生成的模拟采样信号。数模转换器,将第一数字信号转换成第一模拟参考信号,将第一模拟参考信号传输至比较器的反相输入端,也就表示,比较器比较的是第一模拟采样信号与第二模拟采样信号,并且根据第二模拟采样信号与第一模拟采样信号的大小,以及第二模拟采样信号对应的第一数字信号生成下一个用于比较的数字信号。在模拟信号中,第一模拟采样信号与第二模拟采样信号相邻,因此第一模拟采样信号往往比第二模拟采样信号大一个小量或者小一个小量,那么通过用第二模拟采样信号和第一模拟采样信号的比较方式,并且已知第二模拟采样信号对应的数字信号的前提下,确定第一模拟采样信号所转换的数字信号时,往往只需要进行较少的比较次数,即可生成第一模拟采样信号转换成的数字信号,以此提高模数转

换器的模数转换速度,同时降低模数转换器的功耗。

7.可选的,控制器,具体被配置为根据第一比较结果确定第一模拟采样信号大于第一模拟参考信号时,对第一数字信号加上预定步长生成第二数字信号;或者,控制器,具体被配置为根据第一比较结果确定第一模拟采样信号小于第一模拟参考信号时,对第一数字信号减去预定步长生成第二数字信号。其中,该控制器将第二数字信号传输至数模转换器的输入端。在该可选方案中,如果第一模拟采样信号大于第一模拟参考信号,则表示第一数字信号小,因此需要将第一数字信号加上预定步长;或者,如果第一模拟采样信号小于第一模拟参考信号,则表示第一数字信号大,因此需要将第一数字信号减去预定步长。

8.可选的,控制器,还被配置为当确定对第一数字信号连续加上n个预定步长时,触发将第三数字信号传输至数模转换器的输入端,其中第三数字信号的最高有效位置为1,其他有效位置为0,n为大于等于2的正整数;数模转换器,被配置为将第三数字信号转换为第二模拟参考信号,将第二模拟参考信号传输至比较器的反相输入端;比较器,被配置为根据第一模拟采样信号和第二模拟参考信号生成第二比较结果,将第二比较结果传输至控制器;控制器,被配置为根据第二比较结果,确定第一模拟采样信号大于第二模拟参考信号时,将第三数字信号的次高有效位置为1;或者,控制器,被配置为根据第二比较结果,确定第一模拟采样信号小于第二模拟参考信号时,将第三数字信号的最高有效位置为0,将第三数字信号的次高有效位置为1;控制器,被配置为在确定将第三数字信号的最低有效位置为0时,或者,在确定将第三数字信号的最低有效位置为1时,确定第一模拟采样信号对应第三数字信号。在该可选方案中,如果对第一数字信号连续加上n个预定步长以后,还不能确定第一模拟采样信号对应转换成的数字信号时,则表示第一模拟采样信号相较于第二模拟采样信号有较大的变化,例如发生信号突变,这时可以选用传统的sar adc的将模拟采样信号转换成数字信号的方式,这样使得该模数转换器可以使用两种不同的方式将模拟采样信号转换成数字信号。

9.可选的,控制器,还被配置为当确定对第一数字信号连续减去n个预定步长时,触发将第三数字信号传输至数模转换器的输入端,其中第三数字信号的最高有效位置为1,其他有效位置为0,n为大于等于2的正整数;数模转换器,被配置为将第三数字信号转换为第二模拟参考信号,将第二模拟参考信号传输至比较器的反相输入端;比较器,被配置为根据第一模拟采样信号和第二模拟参考信号生成第二比较结果,将第二比较结果传输至控制器;控制器,被配置为根据第二比较结果,确定第一模拟采样信号大于第二模拟参考信号时,将第三数字信号的次高有效位置为1;或者,控制器,被配置为根据第二比较结果,确定第一模拟采样信号小于第二模拟参考信号时,将第三数字信号的最高有效位置为0,将第三数字信号的次高有效位置为1;控制器,被配置为在确定将第三数字信号的最低有效位置为0时,或者,在确定将第三数字信号的最低有效位置为1时,确定第一模拟采样信号对应第三数字信号。

10.可选的,数模转换器,被配置为将第二数字信号转换为第三模拟参考信号,将第三模拟参考信号传输至比较器的反相输入端;比较器,被配置为根据第一模拟采样信号和第三模拟参考信号生成第三比较结果,将第三比较结果传输至控制器;控制器,被配置为根据第三比较结果和第一比较结果,确定第一模拟采样信号小于第一模拟参考信号并且第一模拟采样信号大于第三模拟参考信号时,确定第一模拟采样信号对应第二数字信号;或者,所

述控制器,被配置为根据第三比较结果和第一比较结果,确定第一模拟采样信号大于第一模拟参考信号并且第一模拟采样信号小于第三模拟参考信号时,确定第一模拟采样信号对应第二数字信号。在该可选方式中,由于在第一模拟采样信号小于第一模拟参考信号并且第一模拟采样信号大于第三模拟参考信号时,将第一模拟采样信号转换成第二数字信号;在第一模拟采样信号大于第一模拟参考信号并且第一模拟采样信号小于第三模拟参考信号时,将第一模拟采样信号转换成第二数字信号。也就表示当前的模拟采样信号v2会被转换成后一个数字信号。

11.可选的,采样保持电路,被配置为接收模拟信号,在第二采样时间段对模拟信号进行采样生成第三模拟采样信号,其中,第一采样时间段的结束时刻与第二采样时间段的起始时刻之间的差值大于预定时长。在该可选方案中,第一采样时间段的结束时刻与第二采样时间段的起始时刻之间的差值大于等于预定时长,也就表示采样保持电路在第一采样时间段对模拟信号进行采样生成第一模拟采样信号以后,需要将第一模拟采样信号保持预定时长,使得该第一模拟采样信号转换成数字信号以后,再在第二采样时间段对模拟信号进行采样生成第三模拟采样信号。

12.可选的,数模转换器,具体被配置为在第一采样时间段之后,按照预定的时钟信号将第一数字信号转换为第一模拟参考信号。

13.可选的,采样保持电路,被配置为接收模拟信号,在初始采样时间段对模拟信号进行采样生成第二模拟采样信号,将第二模拟采样信号传输至比较器的正相输入端;控制器,被配置为生成第三数字信号,其中第三数字信号的最高有效位为1,其他有效位为0,将第三数字信号传输至数模转换器的输入端;数模转换器,被配置为将第三数字信号转换为第四模拟参考信号,将第四模拟参考信号传输至比较器的反相输入端;比较器,被配置为根据第二模拟采样信号和第四模拟参考信号生成第四比较结果,将第四比较结果传输至控制器;控制器,被配置为根据第四比较结果,确定第二模拟采样信号大于第四模拟参考信号时,将第三数字信号的次高有效位置为1;或者,控制器,被配置为根据第四比较结果,确定第二模拟采样信号小于第四模拟参考信号时,将第三数字信号的最高有效位置为0,将第三数字信号的次高有效位置为1;控制器,被配置为在确定将第三数字信号的最低有效位置为0时,或者,在确定将第三数字信号的最低有效位置为1时,生成第一数字信号。在该可选方案中,第一数字信号的生成,是按照传统的sar adc的方式将第二模拟采样信号转换成第一数字信号的。

附图说明

14.图1为现有技术中的sar adc将模拟信号转换成数字信号的流程示意图;

15.图2为现有技术中的sar adc将模拟信号转换成数字信号的时序示意图一;

16.图3为现有技术中的sar adc将模拟信号转换成数字信号的时序示意图二;

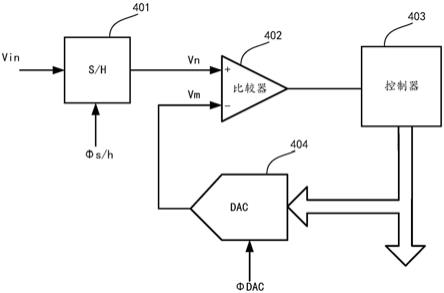

17.图4为本技术的实施例提供的模数转换器的结构示意图;

18.图5为本技术的实施例提供的模拟信号的波形示意图;

19.图6为本技术的实施例提供的模数转换器将模拟信号转换成数字信号的流程示意图;

20.图7为本技术的实施例提供的模数转换器将模拟信号转换成数字信号的时序示意

significant bit,msb)置为1,其他有效位置为0的规则,生成数字信号dac1(100)(这里只是以精度为3bit为例模数转换的结果在(000-111)之间,当然sar adc的精度也可能采用4bit(0000-1111)等)。控制器将数字信号dac1(100)传输至数模转换器(digital-to-analog converter,dac),数模转换器将数字信号dac1(100)转换成模拟参考信号vdac1,随后,数模转换器将模拟参考信号vdac1传输至比较器的反相输入端。参照图2所示,由于当前的模拟采样信号vsh大于模拟参考信号vdac1,比较器输出的比较结果大于0,则表示数字信号dac1(100)的最高有效位是1。

29.在时间段t13,图1所示的比较器接收自正相输入端传输的模拟采样信号vsh,还接收自反相输入端传输的模拟参考信号vdac2,比较器将正相输入端传输的模拟采样信号vsh减去反相输入端传输的模拟参考信号vdac2,生成比较结果。其中,如图2所示,控制器在时间段t12已经确认数字信号dac1的最高有效位为1,并且按照将数字信号dac1的次高有效位置为1,其他有效位置为0的规则,生成数字信号dac2(110),控制器将数字信号dac2(110)传输至数模转换器,数模转换器将数字信号dac2(110)转换成模拟参考信号vdac2,随后,数模转换器将模拟参考信号vdac2传输至比较器的反相输入端。由于当前的模拟采样信号vsh小于模拟参考信号vdac2,比较器输出的比较结果不大于0,则表示数字信号dac2(110)的次高有效位是0。

30.在时间段t14,图1所示的比较器接收自正相输入端传输的模拟采样信号vsh,还接收自反相输入端传输的模拟参考信号vdac3,比较器将正相输入端传输的模拟采样信号vsh减去反相输入端传输的模拟参考信号vdac3,生成比较结果。其中,如图2所示,控制器在时间段t13已经确认数字信号dac2(110)的次高有效位为0,并按照将最低有效位(least significant bit,lsb)置为1的规则,生成数字信号dac3(101),控制器将数字信号dac3(101)传输至数模转换器,数模转换器将数字信号dac3(101)转换成模拟参考信号vdac3,随后,数模转换器将模拟参考信号vdac3传输至比较器的反相输入端。由于当前的模拟采样信号vsh大于模拟参考信号vdac3,比较器输出的比较结果大于0,则表示数字信号dac3(101)的最低有效位是1。

31.在上述时间段t11至时间段t14结束后,控制器可以确定当前的模拟采样信号vsh转换成的数字信号的每一个有效位上的数值,可以确定当前模拟采样信号vsh对应的数字信号为101。

32.参照图3所示,图3为现有技术中的sar adc将模拟信号转换成数字信号的时序示意图二,上述的sar adc将模拟信号转换成数字信号时,系统时钟clk周期往复变化,并且在时间段t11时,系统时钟clk经过一个时钟周期,模拟采样电路s/h在时间段t11根据时钟信号φs/h对模拟信号进行采样模拟采样信号vsh;在时间段t12,数模转换器根据时钟信号φdac将数字信号dac1转换成模拟参考信号vdac1,控制器确定数字信号dac1的最高有效位msb为1;在时间段t13,数模转换器根据时钟信号φdac将数字信号dac2转换成模拟参考信号vdac2,控制器确定数字信号dac2的次高有效位n2为0;在时间段t12,数模转换器根据时钟信号φdac将数字信号dac3转换成模拟参考信号vdac3,控制器确定数字信号dac3的最低有效位lsb为1。并且控制器从时间段t11也开启输出op,需要说明的是,当前输出的是在时间段t11的前一个采样时间段对模拟信号进行采样生成的模拟采样信号所对应的数字信号。

33.在上述的sar adc进行模数转换时,每次采样的模拟信号都要从最高位到最低位的顺序依次比较并确定数值,限制了该sar adc的模数转换速度。

34.为了提高sar adc的模数转换速度,参照图4所示,本技术的实施例提供了一种模数转换器,该模数转换器包括:采样保持电路401、比较器402、控制器403以及数模转换器404,采样保持电路401耦合比较器402的正相输入端,控制器403耦合比较器402的输出端以及数模转换器404的输入端,数模转换器404的输出端耦合比较器402的反相输入端。其中,采样保持电路401传输至比较器402的模拟采样信号vn包括如下所述的模拟采样信号v1、模拟采样信号v2以及模拟采样信号v3;数模转换器404传输至比较器402的模拟参考信号vm包括如下所述的模拟参考信号vm1、模拟参考信号vm2、模拟参考信号vm3以及模拟参考信号vm4。

35.其中,比较器的正相输入端也被称为正向输入端,比较器的反相输入端也被称为反向输入端。

36.在该模数转换器将模拟信号转换成数字信号时,采样保持电路401,被配置为接收模拟信号vin,在一种示例中,该模拟信号vin的波形图如图5所示,该模拟信号vin可以是正弦波信号,并且模拟信号vin的波形在0至满量程电压vfs(即该模拟信号波动的范围)之间波动。其中,在模数转换器的精度为3bit时,模数转换器将模拟信号转换成的数字信号有000-111,其中,000对应的是模拟信号的0至((1/8)*vfs)的范围;001对应的是模拟信号的((1/8)*vfs)至((2/8)*vfs)的范围;010对应的是模拟信号的((2/8)*vfs)至((3/8)*vfs)的范围

…

以此类推,相邻的两位数字信号对应的模拟信号之间间隔(1/8)*vfs。在模数转换器的精度为4bit时,模数转换器将模拟信号转换成的数字信号有0000-1111,其中,0000对应的是模拟信号的0至((1/16)*vfs)的范围;0001对应的是模拟信号的((1/16)*vfs)至((2/16)*vfs)的范围;0010对应的是模拟信号的((2/16)*vfs)至((3/16)*vfs)的范围

…

以此类推,相邻的两位数字信号对应的模拟信号之间间隔(1/16)*vfs。

37.采样保持电路401,被配置为接收模拟信号,在第一采样时间段对模拟信号进行采样生成第一模拟采样信号,将第一模拟采样信号传输至比较器402的正相输入端。示例性的,参照图5所示,采样保持电路401对模拟信号vin进行采样生成模拟采样信号v2。

38.控制器403,被配置为获取第一数字信号,将第一数字信号传输至数模转换器404的输入端;其中,第一数字信号为第二模拟采样信号对应的数字信号,第二模拟采样信号为采样保持电路401在第一采样时间段的前一采样时间段采样生成的模拟采样信号。示例性的,采样保持电路401是在第一采样时间段(采样生成第一模拟采样信号)的前一采样时间段采样生成第二模拟采样信号,并且第二模拟采样信号对应的数字信号是第一数字信号,那么,当前的控制器403将获取第一数字信号,并且将第一数字信号传输至数模转换器404的输入端,当前的控制器403的意图在于比较第二模拟采样信号与第一模拟采样信号。

39.数模转换器404,被配置为将第一数字信号转换为第一模拟参考信号,将第一模拟参考信号传输至比较器402的反相输入端。其中,第二模拟采样信号对应第一数字信号,数模转换器404将第一数字信号转换成第一模拟参考信号,也就表示第一模拟参考信号等于第二模拟采样信号,并且这里所谓的等于并不代表数值上完全相等,而是表示第二模拟采样信号与第一模拟参考信号同源。

40.比较器402,被配置为比较第一模拟采样信号以及第一模拟参考信号,生成第一比

较结果,将第一比较结果传输至控制器403。其中,比较器402比较第一模拟采样信号和第一模拟参考信号,也就表示比较器402比较的是第一模拟采样信号和第二模拟采样信号,而且第一模拟采样信号的采样时间段和第二模拟信号的采样时间段属于相邻的两个采样时间段。其中,比较器402通常将其正相输入端传输的第一模拟采样信号减去反相输入端传输的第一模拟参考信号生成第一比较结果,并且比较器402的比较结果通常只有两个值,一个为1(也叫高电平),另一个为0(也叫低电平),在一些比较器中,比较结果为1表示第一模拟采样信号大于第一模拟参考信号,比较结果为0表示第一模拟采样信号小于等于第一模拟参考信号;在另一些比较器中,比较结果为1表示第一模拟采样信号大于等于第一模拟参考信号,比较结果为0表示第一模拟采样信号小于第一模拟参考信号。本技术的实施例中的比较器402传输的比较结果为1表示第一模拟采样信号大于第一模拟参考信号,比较器402传输的比较结果为0表示第一模拟采样信号小于第一模拟参考信号。当然,如果采用了上述第一种比较器,则比较器402传输的比较结果为1表示第一模拟采样信号大于第一模拟参考信号,比较器402传输的比较结果为0表示第一模拟采样信号小于等于第一模拟参考信号;如果采用了第二种比较器,则比较器402传输的比较结果为1表示第一模拟采样信号大于等于第一模拟参考信号,比较器402传输的比较结果为0表示第一模拟采样信号小于第一模拟参考信号。

41.控制器403,还被配置为根据第一比较结果以及第一数字信号生成第二数字信号。具体的,控制器403,具体被配置为根据第一比较结果确定第一模拟采样信号大于第一模拟参考信号时,对第一数字信号加上预定步长生成第二数字信号;或者,控制器403,具体被配置为根据第一比较结果确定第一模拟采样信号小于第一模拟参考信号时,对第一数字信号减去预定步长生成第二数字信号。控制器403,将第二数字信号传输至数模转换器404的输入端。控制器403通过给第二模拟采样信号对应的数字信号逐次加上预定步长或者减去预定步长,最终生成第一模拟采样信号对应的数字信号。

42.上述的模数转换器,采样保持电路接收模拟信号,并且采样保持电路在第一采样时间段对模拟信号进行采样生成第一模拟采样信号,将第一模拟采样信号输入至比较器的正相输入端。其中,控制器被配置为获取第一数字信号,该第一数字信号是第二模拟采样信号对应的数字信号,第二模拟采样信号为采样保持电路在第一采样时间段的前一采样时间段采样生成的模拟采样信号。数模转换器,将第一数字信号转换成第一模拟参考信号,将第一模拟参考信号传输至比较器的反相输入端,也就表示,比较器比较的是第一模拟采样信号与第二模拟采样信号,并且根据第二模拟采样信号与第一模拟采样信号的大小,以及第二模拟采样信号对应的第一数字信号生成下一个用于比较的数字信号。在模拟信号中,第一模拟采样信号与第二模拟采样信号相邻,因此第一模拟采样信号往往比第二模拟采样信号大一个小量或者小一个小量,那么通过用第二模拟采样信号和第一模拟采样信号的比较方式,并且已知第二模拟采样信号对应的数字信号的前提下,确定第一模拟采样信号所转换的数字信号时,往往只需要进行较少的比较次数,即可生成第一模拟采样信号转换成的数字信号,以此提高模数转换器的模数转换速度,同时降低模数转换器的功耗。

43.在一些实施例中,第一数字信号按照如下方式生成:

44.采样保持电路401,被配置为接收模拟信号,在初始采样时间段对模拟信号进行采样生成第二模拟采样信号,将模拟采样信号传输至比较器402的正相输入端。示例性的,参

照图5所示,采样保持电路401对模拟信号vin进行采样生成模拟采样信号v1,并将模拟采样信号v1传输至比较器402的正相输入端。

45.控制器403,被配置为生成第三数字信号,其中第三数字信号的最高有效位为1,其他有效位为0,将第三数字信号传输至数模转换器404的输入端。示例性的,控制器403根据当前的模数转换器的精度,生成第三数字信号,例如,该模数转换器的精度为3bit,第三数字信号为(100);该模数转换器的精度为4bit,第三数字信号为(1000);以此类推。

46.数模转换器404,被配置为将第三数字信号转换为第四模拟参考信号,将第四模拟参考信号传输至比较器402的反相输入端。示例性的,控制器403生成的第三数字信号需要转换成第四模拟参考信号,才能与第二模拟采样信号进行比较,因此需要数模转换器404接收自控制器403传输的第三数字信号,并且将第三数字信号转换成第四模拟参考信号,然后数模转换器404将第四模拟参考信号传输至比较器402。

47.比较器402,被配置为根据第二模拟采样信号和第四模拟参考信号生成第四比较结果,将第四比较结果传输至控制器403。示例性的,比较器402接收自正相输入端传输的第二模拟采样信号,比较器402还接收自反相输入端传输的第四模拟参考信号,比较器402比较第二模拟采样信号和第四模拟参考信号,生成第四比较结果。

48.控制器403,被配置为根据第四比较结果,确定第二模拟采样信号大于第四模拟参考信号时,将第三数字信号的次高有效位置为1;或者,控制器403,被配置为根据第四比较结果,确定第二模拟采样信号小于第四模拟参考信号时,将第三数字信号的最高有效位置为0,将第三数字信号的次高有效位置为1。示例性的,在控制器403接收到比较器402传输的第四比较结果,并且可以确定当前的第二模拟采样信号大于第四模拟参考信号时,则表明当前的第三数字信号比第二模拟采样信号对应的数字信号小,因此第二模拟采样信号对应的数字信号的最高有效位为1,则该控制器403将第三数字信号的最高有效位置位1不变,并且将第三数字信号的次高有效位置为1,然后再确定第二模拟采样信号对应转换成的数字信号的次高有效位的数值。或者,在控制器403接收到比较器402传输的第四比较结果,并且可以确定当前的第二模拟采样信号小于第四模拟参考信号时,则表明当前的第三数字信号比第二模拟采样信号对应的数字信号大,因此控制器可以确定第二模拟采样信号对应的数字信号的最高有效位为0,则该控制器403将第三数字信号的最高有效位置为0,并且将第三数字信号的次高有效位置为1,然后再确定第二模拟采样信号对应转换成的数字信号的次高有效位的数值。

49.控制器403,被配置为在确定将第三数字信号的最低有效位置为0时,或者,在确定将第三数字信号的最低有效位置为1时,生成第一数字信号。示例性的,在上述的步骤逐次重复时,控制器403可以分别确定第三数字信号的最高有效位、次高有效位

…

最低有效位上的数值,在控制器403确定将第三数字信号的最低有效位置为0时,或者,在控制器确定将第三数字信号的最低有效位置为1时,则表明当前的控制器403已经确定第二模拟采样信号对应转换成的数字信号的每一个有效位上的数值,即可生成第一数字信号,并且,在该实施例中,第一数字信号是通过传统sar adc的模数转换方式生成的。

50.在另一些实施例中,第一数字信号还可以按照上述的第一模拟采样信号转换成数字信号的方式生成,本技术的实施例对第一数字信号的生成方式不做限定。

51.示例性的,以模数转换器的精度为3bit为例,进一步对本技术的实施例提供的模

数转换器的模数转换方式进行说明。参照图6和图7所示所示,图6为本技术的实施例提供的模数转换器将模拟信号转换成数字信号的流程示意图,图7为本技术的实施例提供的模数转换器将模拟信号转换成数字信号的时序示意图一。其中,采样保持电路401传输至比较器402的模拟采样信号vn包括如下所述的模拟采样信号v1、模拟采样信号v2以及模拟采样信号v3;数模转换器404传输至比较器402的模拟参考信号vm包括如下所述的模拟参考信号vm1、模拟参考信号vm2、模拟参考信号vm3以及模拟参考信号vm4。

52.在时间段t21,采样保持电路401被配置为接收模拟信号vin,在初始采样时间段对模拟信号vin进行采样生成模拟采样信号v1,采样保持电路401将模拟采样信号v1传输至比较器402的正相输入端。具体的,采样保持电路401根据时钟信号φs/h对模拟信号vin进行采样生成模拟采样信号v1,并且该模拟采样信号v1保持至时间段t24结束。

53.在时间段t22,控制器403,被配置为生成第三数字信号,其中第三数字信号的最高有效位为1,其他有效位为0,将第三数字信号传输至数模转换器的输入端。参照图7所示,控制器403根据当前模数转换器的精度为3bit,得知当前的模拟采样信号v1需要转换成三位二进制数字信号,并且控制器403按照最高有效位置为1,其他有效位置为0的规则,生成数字信号(100),并且控制器403将数字信号(100)传输至数模转换器404的输入端;数模转换器404,被配置为将数字信号100转换成模拟参考信号vm1(也就是上述的第四模拟参考信号),具体的,数模转换器404根据时钟信号φdac将数字信号100转换成模拟参考信号vm1,将模拟参考信号vm1传输至比较器402的反相输入端;比较器402被配置为根据模拟参考信号vm1以及模拟采样信号v1生成比较结果c1(也就是上述的第四比较结果),示例性的,比较器402可以根据将其正相输入端传输的模拟采样信号v1减去反相输入端传输的模拟参考信号vm1生成比较结果c1,比较器402将比较结果c1传输至控制器403。控制器403,还被配置为根据比较结果c1,确定模拟采样信号v1大于模拟参考信号vm1时,将数字信号(100)的次高有效位置为1,生成数字信号(110),或者,在确定模拟采样信号v1小于模拟参考信号vm1时,将数字信号(100)的最高有效位置为0,将数字信号100的次高有效位置为1,生成数字信号(010)。图6所示的模拟采样信号v1小于模拟参考信号vm1,因此生成数字信号(010),也就表示,在时间段t22后,模拟采样信号v1对应的数字信号的最高有效位的数值已确定。

54.如图7所示,在时间段t23,按照与时间段t22相同的比较方式,确定模拟采样信号v1对应的数字信号的次高有效位的数值,该模拟采样信号v1对应的数字信号的次高有效位的数值为1;在时间段t24,按照与时间段t22相同的比较方式,确定模拟采样信号v1对应的数字信号的最低有效位的数值,该模拟采样信号v1对应的数字信号的最低有效位的数值为0。控制器403,被配置为在确定数字信号(100)的最低有效位的数值为0,或者,在确定数字信号(100)的最低有效位的数值为1时,生成数字信号d1(也就是上述的第一数字信号),模拟采样信号v1生成的数字信号为(010),数字信号d1为(010)。

55.在时间段t25,参照图5所示,采样保持电路401,被配置为接收模拟信号vin,在第一采样时间段对模拟信号vin进行采样生成模拟采样信号v2,将模拟采样信号v2传输至比较器402的正相输入端。

56.结合图6所示,在时间段t26时,控制器403,被配置为获取数字信号d1,将数字信号d1传输至数模转换器404的输入端,其中,数字信号d1为模拟采样信号v1对应的数字信号,模拟采样信号v1为采样保持电路401在第一采样时间段的前一采样时间段采样生成的模拟

采样信号,因此模拟采样信号v2与模拟采样信号v1相邻。数模转换器404,被配置为将数字信号d1转换为模拟参考信号vm2(也就是上述的第一模拟参考信号),将模拟参考信号vm2传输至比较器402的反相输入端;比较器402,被配置为比较模拟采样信号v2以及模拟参考信号vm2,生成比较结果c2(也就是上述的第一比较结果),示例性的,比较器402可以根据将其正相输入端传输的模拟采样信号v2减去反相输入端传输的模拟参考信号vm2生成比较结果c2,将比较结果c2传输至控制器403;控制器403,还被配置为根据比较结果c2以及数字信号d1生成数字信号d2(也就是上述的第二数字信号)。示例性的,图6所示的模拟采样信号v2大于模拟参考信号vm2,则比较器将其正相输入端传输的模拟采样信号v2减去反相输入端传输的模拟参考信号vm2生成比较结果c2大于0,控制器403被配置为对数字信号d1加上预定步长生成数字信号d2,将数字信号d2传输至数模转换器404的输入端,该预定步长通常为1,因此数字信号d2为(010+1),数字信号d2为(011)。

57.在另一些实施例中,控制器403,具体被配置为根据比较结果c2确定模拟采样信号v2小于模拟参考信号vm2时,也就是比较器402将其正相输入端传输的模拟采样信号v2减去反相输入端传输的模拟参考信号vm2生成比较结果c2小于0时,对数字信号d1减去预定步长生成数字信号d2,将数字信号d2传输至数模转换器404的输入端。该预定步长通常为1,例如在数字信号d1为010时,对数字信号d1减去预定步长,生成数字信号d2,因此数字信号d2为(010-1),数字信号d2为(001)。

58.在时间段t27,数模转换器404被配置为将数字信号d2转换为模拟参考信号vm3,将模拟参考信号vm3传输至比较器402的反相输入端;比较器402,被配置为根据模拟采样信号v2和模拟参考信号vm3生成比较结果c3,将比较结果c3传输至控制器403;控制器403,被配置为根据比较结果c2和比较结果c3,确定模拟采样信号v2小于模拟参考信号vm2并且模拟采样信号v2大于模拟参考信号vm3时,确定将模拟采样信号v2对应数字信号d2;或者,控制器403,被配置为根据比较结果c2和比较结果c3,确定模拟采样信号v2大于模拟参考信号vm2并且模拟采样信号v2小于模拟参考信号vm3时,确定将模拟采样信号v2对应数字信号d2。也就表示当前的模拟采样信号v2被转换成后一个数字信号。当然,在该模数转换器被配置为获取将模拟采样信号转换的较大的一个数字信号时,控制器403,被配置为根据比较结果c2和比较结果c3,确定模拟采样信号v2小于模拟参考信号vm2并且模拟采样信号v2大于模拟参考信号vm3时,确定将模拟采样信号v2对应数字信号d1;或者,控制器403,被配置为根据比较结果c2和比较结果c3,确定模拟采样信号v2大于模拟参考信号vm2并且模拟采样信号v2小于模拟参考信号vm3时,确定将模拟采样信号v2对应数字信号d2。在该模数转换器被配置为获取将模拟采样信号转换的较小的一个数字信号时,控制器403,被配置为根据比较结果c2和比较结果c3,确定模拟采样信号v2小于模拟参考信号vm2并且模拟采样信号v2大于模拟参考信号vm3时,确定将模拟采样信号v2对应数字信号d2;或者,控制器403,被配置为根据比较结果c2和比较结果c3,确定模拟采样信号v2大于模拟参考信号vm2并且模拟采样信号v2小于模拟参考信号vm3时,确定将模拟采样信号v2对应数字信号d1。

59.本技术的实施例是以模数转换器的精度为3bit为例进行说明的,在模数转换器的精度更高时,本技术的实施例提供的模数转换器的速度将越快。

60.在一些实施例中,控制器403,还被配置为当确定对数字信号d1连续加上n个预定步长时,触发将数字信号d3传输至数模转换器404的输入端,其中数字信号d3的最高有效位

置为1,其他有效位置为0,n为大于等于2的正整数;将数字信号d3传输至数模转换器404的输入端;数模转换器404,被配置为将数字信号d3转换为模拟参考信号vm4,将模拟参考信号vm4传输至比较器402的反相输入端;比较器402,被配置为根据模拟采样信号v2和模拟参考信号vm4生成比较结果c4,将比较结果c4传输至控制器403;控制器403,被配置为根据比较结果c4,确定模拟采样信号v2大于模拟参考信号vm4时,将数字信号d3的次高有效位置为1。或者,控制器403,被配置为根据比较结果c4,确定模拟采样信号v2小于模拟参考信号vm4时,将数字信号d3的最高有效位置为0,将数字信号d3的次高有效位置为1。控制器403,被配置为在确定将数字信号d3的最低有效位置为0时,或者,在确定将数字信号d3的最低有效位置为1时,确定模拟采样信号v2对应数字信号d3。

61.在另一些实施例中,控制器403,还被配置为当确定对数字信号d1连续减去n个预定步长时,触发将数字信号d3传输至数模转换器404的输入端,其中数字信号d3的最高有效位置为1,其他有效位置为0,n为大于等于2的正整数;将数字信号d3传输至数模转换器404的输入端;数模转换器404,被配置为将数字信号d3转换为模拟参考信号vm4,将模拟参考信号vm4传输至比较器402的反相输入端;比较器402,被配置为根据模拟采样信号v2和模拟参考信号vm4生成比较结果c4,将比较结果c4传输至控制器403;控制器403,被配置为根据比较结果c4,确定模拟采样信号v2大于模拟参考信号vm4时,将数字信号d3的次高有效位置为1。或者,控制器403,被配置为根据比较结果c4,确定模拟采样信号v2小于模拟参考信号vm4时,将数字信号d3的最高有效位置为0,将数字信号d3的次高有效位置为1。控制器403,被配置为在确定将数字信号d3的最低有效位置为0时,或者,在确定将数字信号d3的最低有效位置为1时,确定模拟采样信号v2对应数字信号d3。

62.也就是说,在上述的模数转换器中的控制器403确定对数字信号d1连续加上或者连续减去n个预定步长后,还是无法确定模拟采样信号v2对应的数字信号,则表明当前的模拟采样信号v2相较于模拟采样信号v1发生了较大的改变,例如发生了信号突变。示例性的,在模拟采样信号v1对应的数字信号为(000),模拟采样信号v2对应的数字信号为(111),因此对数字信号(000)加上一次预定步长会变成数字信号(001),再加上一次预定步长会变成数字信号(010)

…

连续加上7次预定步长才能得到数字信号(111)。因此,在本技术中,控制器确定给数字信号(000)连续加上2次预定步长以后,还不能确定模拟采样信号v2对应的数字信号,则触发获取数字信号(100),并且选用传统的sar adc的将模拟采样信号v2转换成数字信号的方式,这样使得本技术的实施例提供的模数转换器可以使用两种不同的方式将模拟采样信号v2转换成数字信号。需要说明的是,n为大于等于2的正整数,n的具体取值由上述的模数转换器的精度决定,例如当精度是3bit的时候限定n等于2,在精度为4bit是限定n等于3,本技术的实施例对此不做限定。

63.参照图5所示,本技术的实施例提供的模数转换器在第二采样时间段对模拟信号vin进行采样生成模拟采样信号v3,其中,第一采样时间段的结束时刻与第二采样时间段的起始时刻之间的差值大于预定时长,示例性的,该预定时长需要确保第一采样时间段对模拟信号进行采样生成的模拟采样信号v2转换成数字信号以后,模数转换器才在第二采样时间段对模拟信号vin进行采样生成模拟采样信号v3。参照图8所示,本技术的实施例提供了模数转换器将模拟信号转换成数字信号的时序示意图二,上述的模数转换器将模拟信号转换成数字信号时,系统时钟clk周期往复变化,并且在时间段t25时,系统时钟clk经过一个

时钟周期,模拟采样电路s/h根据时钟信号φs/h将模拟信号转换成模拟采样信号v2;在时间段t26,数模转换器根据时钟信号φdac将数字信号(010)转换成模拟参考信号vm2,比较器进行第一次比较comp1,控制器确定模拟采样信号v2大于模拟参考信号vm2;在时间段t27,数模转换器根据时钟信号φdac将数字信号(011)转换成模拟参考信号vm3,比较器进行第二次比较comp2,控制器确定模拟采样信号v2小于模拟参考信号vm3。并且控制器从时间段t25也开启输出op,需要说明的是,当前输出的是第一采样时间段的前一个采样时间段t21采样生成的模拟采样信号v1所转换的数字信号(010),也就表示,模数转换器在开启一次采样时,输出前一次采样的模拟采样信号转换成的数字信号。然后在时间段t28对模拟信号vin进行采样生成模拟采样信号v3,时间段t25的结束时刻与时间段t28的开始时刻之间包括时间段t26和时间段t27,并且在时间段t26和时间段t27之间控制器确定将模拟采样信号v2转换成数字信号。其中,上述的每一个时间段所表示时长可以相同也可以不同,本技术的实施例对此不做限定。例如可以在系统时钟经过2个时钟周期时,模拟采样电路s/h根据时钟信号φs/h将模拟信号转换成模拟采样信号v2。

64.在上述实施例中,对各个实施例的描述各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

65.尽管结合具体特征及其实施例对本技术进行了描述,显而易见的,在不脱离本技术的精神和范围的情况下,可对其进行各种修改和组合。相应地,本说明书和附图仅仅是所附权利要求所界定的本技术的示例性说明,且视为已覆盖本技术范围内的任意和所有修改、变化、组合或等同物。显然,本领域的技术人员可以对本技术进行各种改动和变型而不脱离本技术的精神和范围。这样,倘若本技术的这些修改和变型属于本技术权利要求及其等同技术的范围之内,则本技术也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1