晶体振荡器的制作方法

1.本发明涉及一种进行储存晶体振子的封装体内的温度调整的晶体振荡器。

背景技术:

2.作为用于抑制周围温度变化的影响而获得稳定的振荡输出的晶体振荡器,已知一种包括储存晶体振子并且对内部温度进行调整的封装体的晶体振荡器(恒温晶体振荡器(oven controlled crystal oscillator,ocxo))。在此ocxo的制造步骤中,通过将所述封装体的结构零件接合,而进行所述封装体的全密闭。具体而言,例如存在如下情况:通过电阻焊接将支撑搭载有各种电路零件的基板的基底的金属部、与金属盖中向外侧扩展形成的周缘部接合,而进行其全密闭。

3.另外,例如专利文献1中,示出如下结构的元件作为ocxo的一例:分别在基板下表面搭载晶体振子及加热器(发热体),在基板上表面搭载振荡电路及加热器,基板的周缘部支撑在设于封装体内的阶部。并且在此ocxo中,经由设于基板的端子及连接于所述端子的接合线,搭载于基板的各零件与设于封装体内的端子电连接。

4.现有技术文献

5.专利文献

6.专利文献1:日本专利特开2006-14208(图4、段落[0020])

技术实现要素:

[0007]

发明所要解决的问题

[0008]

对于ocxo要求小型化,与此相应地,对于封装体的结构零件中要焊接的区域,要求缩小化。为了应对此种情况,研究例如使用纵截面为凹状的陶瓷制基底及金属制盖体作为封装体的结构零件,通过缝焊接等将盖体与设于基底开口缘的金属部接合而进行密封。

[0009]

但是,关于包括通过以此方式进行密封而制得的封装体的ocxo,由于陶瓷的导热率相对较高,因此有设于封装体内的发热体的热量传递至封装体,并发散到所述封装体外部的疑虑。如此一来,导致封装体内的温度控制较为困难。即,ocxo的小型化与封装体内的温度控制性成为取舍关系。

[0010]

本发明是鉴于所述情况而成,其目的在于提供一种小型且能够获得稳定的振荡输出的晶体振荡器。

[0011]

解决问题的技术手段

[0012]

本发明的晶体振荡器是包括在内部储存晶体振子的封装体的晶体振荡器,其特征在于包括:

[0013]

基板,在一面侧设有所述晶体振子,在另一面侧设有包括用于使所述晶体振子振荡的振荡电路的电路零件、及调整所述封装体内的温度的发热体;

[0014]

阶部,以所述晶体振子、所述电路零件及所述发热体从所述封装体的壁部隔开的方式,形成于所述封装体的内壁以从一面侧仅支撑所述基板中的端部;以及

[0015]

金属线,将设于所述发热体的端子与设于所述封装体的内部的端子不经由所述基板地加以连接。

[0016]

发明的效果

[0017]

根据本发明的晶体振荡器,分别在基板的一面侧设有晶体振子,在基板的另一面侧设有包括振荡电路的电路零件及发热体,以设于基板的这些各构成元件从封装体的壁部隔开的方式,所述基板的端部支撑在所述封装体内。并且,发热体的端子及设于封装体的端子不经由基板而通过金属线连接。通过此种结构防止基板大型化,且抑制从发热体向封装体传热,所述封装体内的温度控制性变高。因此,关于本发明的晶体振荡器,能制成小型晶体振荡器,且能获得稳定的振荡输出。

附图说明

[0018]

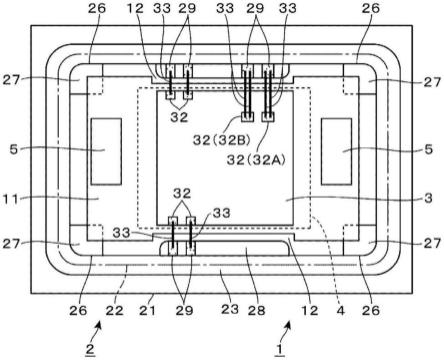

图1是本发明的一实施方式的ocxo的横向俯视图。

[0019]

图2是所述ocxo的纵向前视图。

20.图3是所述ocxo的纵向侧视图。

[0021]

图4是所述ocxo的上表面侧分解立体图。

[0022]

图5是所述ocxo的下表面侧分解立体图。

[0023]

图6是用于说明各自构成所述ocxo的基板与封装体的位置关系的俯视图。

[0024]

图7是说明评价试验结果的折线图。

具体实施方式

[0025]

关于作为本发明的一实施方式的包括封装体的晶体振荡器的ocxo1,一边适当参照图1的横向俯视图、图2的纵向前视图、图3的纵向侧视图、图4的上表面侧分解立体图、图5的下表面侧分解立体图,一边进行说明。ocxo1包括基板11、封装体2、集成电路(integrated circuit,ic)芯片3、晶体振子4及两个电容器5。ic芯片3、晶体振子4及电容器5设于基板11,关于其配置将于下文叙述。

[0026]

具有作为恒温槽作用的封装体2形成为方形,包括基底21及盖体(盖)22。封装体2构成为俯视长方形。以下,每次说明ocxo1时,将所述长方形的长边方向作为左右方向、短边方向作为前后方向进行说明。而且,将设有盖体22的侧作为上侧进行说明。但是,此处所述的上下左右前后的方向是为了便于说明ocxo1的结构而附加的,ocxo1可以在任一方向上使用。封装体2的左右的长度为9mm以下,更具体而言,例如为7mm,封装体2的前后的长度为7mm以下,更具体而言,例如为5mm。

[0027]

所述基底21构成封装体2的侧壁及底部,其材质为陶瓷。基底21的纵截面形成为凹状,因此基底21包括上侧开口的开口部。以沿着此开口部边缘的方式,形成作为环状突起的密封圈23作为金属部。在此密封圈23上焊接作为金属板的盖体(盖)22的周缘部,使封装体2内为气密空间。俯视下,所述气密空间形成为大致长方形。

[0028]

在基底21的下表面设有用于将ocxo1与外部设备连接的金属制的焊垫24、焊垫25,例如焊垫24设有四个,焊垫25设有两个。焊垫24是与构成ocxo1的各电路连接的电极端子。即,焊垫24与搭载于基板11的所述各零件电连接,通过各焊垫24与设于ocxo1外部的外部设备的电极端子连接,ocxo1运行。

[0029]

对封装体2的内部进行说明。通过封装体2内的四个各角部中的侧壁的下部侧以向封装体2的内侧鼓起的方式形成,而在所述封装体2的内侧壁设有阶部26。换个角度而言,通过封装体2内的四个各角部中的底面隆起,而形成阶部26。阶部26的上表面形成与封装体2的底壁及盖体22平行地支撑基板11的支撑面27。

[0030]

而且,通过封装体2的前方侧、后方侧的各侧壁中的左右的中央下部也以向封装体2的内侧鼓起的方式形成,而设有左右细长的阶部28,各阶部28形成为高于所述阶部26。在各阶部28的上表面形成有多个端子29作为金属膜的图案。端子29经由封装体2的侧壁及底壁的内部、和形成于所述底壁表面的未图示的导电路径,而连接于所述封装体2的下表面的焊垫24。以下,为了避免混淆,有时将阶部26记载为基板支撑用阶部26,将阶部28记载为连接用阶部28。

[0031]

继而,对基板11进行说明。基板11例如为树脂制,在其上表面侧(另一面侧)、下表面侧(一面侧)形成有包括金属膜例如铜膜的图案。关于其图案中作为下表面侧图案的散热用图案,将于下文具体说明。

[0032]

基板11俯视下为大致长方形,例如长边方向的长度、短边方向的长度分别为5mm、3mm。关于所述基板11,其四个角部的下表面侧经由未图示的粘附材料固定并支撑在所述基板支撑用阶部26的支撑面27上,其长边方向、短边方向分别相对于封装体2的长边方向、短边方向对齐。并且,基板11的侧面远离封装体2的侧壁。进而详细地说,设于基板11的各零件(ic芯片3、晶体振子4及电容器5)从封装体2的内壁隔开。因此,关于基板11及搭载于基板11的各零件,除基板11的角部以外,为浮在封装体2空中的状态。另外,在基板11的前方侧、后方侧各自的左右的中央部设有缺口12,防止所述基板11与所述封装体2的连接用阶部28接触。

[0033]

在基板11的上表面侧设有ic芯片3及两个电容器5。各电容器5为旁路电容器,分别设在基板11的左右。并且,ic芯片3夹于电容器5设于基板11的中央部。ic芯片3是包括用于使晶体振子4振荡的振荡电路、将来自振荡电路的输出放大的放大电路(输出电路)及发热体(加热器电路)等多个电路的电路零件。另外,虽省略图示,但在基板11的上表面或下表面设有热敏电阻作为用于检测晶体振子4的温度的电路零件。根据利用所述热敏电阻的检测温度,调整由ic芯片3带来的发热体的发热量,进行温度控制使晶体振子4的温度、即封装体2内的温度变得固定。关于此热敏电阻,和其他电路零件同样地,也不接触封装体2的内壁。

[0034]

在ic芯片3的上表面设有许多端子。关于这些端子,为了避免与封装体2侧的端子29混淆,而记载为芯片端子32。此许多芯片端子32中的一部分多个端子通过接合线33分别与所述封装体2的连接用阶部28的端子29连接。即,芯片端子32及端子29通过接合线33直接连接而不经由设于基板11的作为金属膜的图案。接合线33相对较细,例如其截面直径为30μm。而且,接合线33例如包含金或铜。

[0035]

另外,关于许多芯片端子32中的其他一部分多个端子,为了与晶体振子4、电容器5电连接,通过接合线33连接于设于基板11的上表面的图案。其中,此种芯片端子32中的其他一部分端子、基板11的上表面的图案、所述连接其他一部分端子及所述图案的接合线33省略图示。

[0036]

作为所述不经由基板11而通过接合线33与封装体2的端子29直接连接的芯片端子32,包含设于发热体的多个芯片端子32。为了便于说明,将此发热体的芯片端子32记载为

32a、32b。芯片端子32a是对发热体施加电源电压的端子(vcc端子),芯片端子32b是接地端子。

[0037]

如此,通过发热体的芯片端子32a、芯片端子32b利用接合线33与封装体2的端子29直接连接的结构,抑制发热体向封装体2的外部散热。关于此散热的抑制,进一步详细地叙述。制成如下结构:假如不直接连接芯片端子32a、芯片端子32b及端子29,而在基板11形成与芯片端子32a、芯片端子32b各者连接的金属膜的图案,通过接合线33连接此图案及封装体2的端子29。或者制成如下结构:在基板11形成与芯片端子32a、芯片端子32b各者连接的金属膜的图案,并且在封装体2的基板支撑用阶部26设置与此基板11的图案连接,并向封装体2的外部拉出的导电路径。

[0038]

但是,若以如上方式制成在基板11形成与芯片端子32a、芯片端子32b连接的图案的结构,则发热体的热量沿所述图案、即基板11移动,但如上所述,由于基板11的角部与封装体2接触,因此经由所述角部的朝向封装体2的传热量变多,作为其结果,导致向封装体2的外侧的散热量变多。另一方面,在发热体的芯片端子32a、芯片端子32b通过接合线33直接与封装体2的端子29连接的结构中,由于没有与芯片端子32a、芯片端子32b连接的基板11的图案,因此经由所述图案的朝向所述基板11的热传导不存在,由于接合线33较细,因此经由所述接合线33的朝向封装体2的热量移动较少。因此,发热体的热量容易停留在封装体2内,能够抑制朝向封装体2的外部的散热。

[0039]

芯片端子32a、芯片端子32b分别通过多个接合线33,例如如图1所示,通过两个接合线33连接于封装体2的端子29。由此,芯片端子32a、芯片端子32b与端子29间的电压下降被抑制。而且,根据封装体2的外侧的温度(周围环境温度),为了获得较高的发热量,而在发热体中流通相对较大的电流,但即便在此种情况下,也可以抑制来自每个接合线33的发热,能够更加确实地防止由所述发热引起的接合线33的破损。另外,作为分别与芯片端子32a、芯片端子32b连接的接合线33并不限于此例,也可以多于两个。

[0040]

以下,也一边参照概略性表示基板11的下表面的图6,一边进行说明。在基板11的背面侧的中央部设有晶体振子4。此晶体振子4被封装化。具体进行说明,晶体振子4除包括形成有激励电极的晶体片(为了便于说明,设为晶体振子元件41)以外,还包括气密地收容所述晶体振子元件41的振子用封装体42。在形成为方形的振子用封装体42的表面形成有四个端子,所述四个端子分别与设于基板11的下表面的图案连接。

[0041]

将此振子用封装体42的四个端子中的经由所述振子用封装体42内未图示的导电路径与晶体振子元件41的激励电极连接的两个端子示出为43。并且,将剩余的两个端子示出为44。端子44为接地端子,通过经由设于基板11的导电路径(通孔或图案)、接合线33及封装体2的端子29,与封装体2下侧的焊垫24中的接地用焊垫24电连接。

[0042]

并且,在基板11的下表面,设有分别配置于晶体振子4的左侧、右侧且与所述端子44连接的图案。若将所述图案作为散热用图案45,则各散热用图案45以其一部分与封装体2的基板支撑用阶部26的支撑面27重叠的方式形成。如上所示,基板11经由粘附材料固定于封装体2,散热用图案45经由粘附材料层叠于基板支撑用阶部26的支撑面27。

[0043]

对散热用图案45的作用进行说明,ic芯片3中所包含的除发热体以外的各电路通过自耗电力发热,其发热量与发热体的发热量不同且无法控制。因此,认为由于所述各电路的发热,导致封装体2内的温度偏离所需温度,为了应对所述发热问题而设置散热用图案

45。进而详细地叙述,ic芯片3的发热体以外的电路的热量经由连接ic芯片3及晶体振子4的接合线33及基板11的导电路径而向晶体振子4传热。并且,此热量向与晶体振子4连接的散热用图案45传递,进而向与散热用图案45相接的封装体2的基板支撑用阶部26移动。基板11的导电路径和散热用图案45为金属,即导电性高的材料,此种向基板支撑用阶部26的传热高效率地进行。并且,以此方式移动至基板支撑用阶部26的热量经由封装体2的壁部,向所述封装体2的外侧扩散。

[0044]

补充说明,在基板支撑用阶部26未设置连接基板11的支撑面27及封装体2的外侧表面的导电路径。即,包括连接端子29及封装体2的外侧表面的焊垫24的导电路径的连接用阶部28、与所述基板支撑用阶部26为相互不同的结构。这是因为,假如连接封装体2的外侧及支撑面27的导电路径设于基板支撑用阶部26,则关于从发热体散发的热量,有通过经由所述导电路径从基板11向封装体2的外部扩散的量变多的顾虑,即,有导致经由支撑基板11的基板支撑用阶部26的朝向外部的散热量变大的疑虑。即,ocxo1中,通过制成在基板支撑用阶部26未设置所述导电路径的结构,抑制经由此基板支撑用阶部26的不需要的散热,封装体2内的温度控制性提高。

[0045]

如上所述,在ocxo1中,在基板11的上表面侧、下表面侧分别设有ic芯片3、晶体振子4,基板11从下表面侧通过封装体2的阶部26支撑其角部。由此,如例示其尺寸那样,能将ocxo1小型化。并且,通过ic芯片3中所包含的发热体的芯片端子32及封装体2的端子29由接合线33连接,抑制从发热体散发的热量向封装体2的外部扩散。因此,抑制封装体2内的温度偏移设定温度,因此ocxo1可以获得稳定的振荡输出。另外,晶体振子4在基板11中设于与基底21的开口侧相反的下表面侧,由此不易受到封装体2外侧的温度变化等环境变化的影响,这也有助于振荡输出的稳定化。

[0046]

进而,如上所述,抑制发热体的热量向封装体2的外部扩散,另一方面,从ic芯片3中除发热体以外的电路散发的热量经由作为散热用金属膜的散热用图案45,高效率地向封装体2的外部扩散。因此,能够更加确实地抑制封装体2内的温度偏移设定温度。

[0047]

在以上所述示例中,以与晶体振子4的端子43、端子44中作为接地端子的端子44连接的方式形成散热用图案45,但只要是从晶体振子4的端子向封装体2传热的结构即可,也可以连接于端子43的方式形成散热用图案45。另外,在图6中省略显示,但在基板11的下表面形成有用于连接晶体振子4、及ic芯片3等基板11的上表面侧的各零件的图案(连接用图案)。散热用图案45可与此连接用图案分开(分离)形成,也可一部分与所述连接用图案共通化(相互相接)而形成。

[0048]

而且,在所述例中,为了能更加确实地向封装体2散热,散热用图案45以与阶部26的支撑面27重叠的方式形成。但是,散热用图案45的面积相对越大则由于热辐射而向封装体2移动的热量越多,因此可通过适当设定此面积,使散热用图案45以不与阶部26重叠的方式形成。如此,在不与阶部26重叠的情况下,例如露出基板11的下表面的散热用图案45的面积为基板11的下表面的面积的20%以上。所述露出基板11的下表面的面积是未被晶体振子4等零件覆盖的区域的面积。

[0049]

另外,在图6所示的例子中,散热用图案45以与四个基板支撑用阶部26中的三个重叠的方式形成,但以与几个阶部26重叠的方式形成是可以任意决定的,以使封装体2内的温度控制性良好。即,与散热用图案45重叠的阶部26的数量不限于三个。

[0050]

在所述例子中,发热体组装于ic芯片3,但也可以是单独的电路零件,而不按此种方式组装。而且,振荡电路等电路零件也可作为个别的电路零件而不集成化。而且,支撑基板11的基板支撑用阶部26不限于是按以上方式支撑作为基板11周缘部的一部分的角部的结构,也可以按支撑基板11的整个周缘部的方式构成。但是,为了防止发热体的热量从基板11向封装体2移动,优选为仅支撑角部。

[0051]

而且,对封装体2是焊接的结构进行了叙述,但并不限于这样通过焊接而制造,例如也可以通过钎料或粘附材料进行盖体22与基底21的接合。因此,密封圈23也并非必须,盖体22也不限于金属。而且,如发明所要解决的问题的项目中所述,本发明的技术在基底21为陶瓷制的情况下有效,但根据本发明,不论基底21的材质如何,都能抑制热量向封装体2的外侧释放,因此基底21不限于由陶瓷构成,例如也可使用树脂等材料构成。

[0052]

如此,关于本次揭示的实施方式,应认为所有方面都为例示而非限制。所述实施方式可不脱离附加的申请专利范围及其主旨,而以各种形态进行省略、置换、变更或组合。

[0053]

(评价试验)

[0054]

说明与本发明关联进行的评价试验。通过模拟,分别测定改变ocxo1的周围环境温度时的ic芯片3的温度、晶体振子4的温度。更详细而言,ic芯片3的温度是组装于ic芯片3的热敏电阻的检测温度,更详细而言,晶体振子4的温度是设置于晶体振子4附近的热敏电阻的检测温度。图7是表示此评价试验结果的折线图。如图所示,当周期环境温度在-40℃~+85℃内变化时,ic芯片3的温度变化控制在2℃左右,晶体振子4的温度变化控制在5℃左右。因此,确认ocxo1可获得如上所述的效果,即可如上所述使封装体2内的温度稳定化。

[0055]

另外,使用除基板11未设置散热用图案45以外以与ocxo1相同的方式构成的ocxo,进行对ocxo1所进行的模拟相同的模拟。其结果,确认到ocxo1抑制关于ic芯片3及晶体振子4的温度变化。即,确认通过设置散热用图案45,封装体2内的温度控制性变高。

[0056]

符号的说明

[0057]

1:ocxo

[0058]

2:封装体

[0059]

26:阶部

[0060]

29:端子

[0061]

3:ic芯片

[0062]

32a、32b:端子

[0063]

33:接合线

[0064]

4:晶体振子。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1