一种低开销容忍三节点翻转自恢复的抗辐射加固锁存器

1.本发明属于集成电路技术领域,涉及一种低开销容忍三节点翻转自恢复的抗辐射加固锁存器。

背景技术:

2.在cmos中,传输门(transmission gate)是一种既可以传送数字信号又可以传输模拟信号的可控开关电路。而传输门由一个pmos管和一个nmos管并联构成,其具有很低的导通电阻(几百欧)和很高的截止电阻(大于10^9欧)。

3.所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态才被保存到输出,直到下一个锁存信号到来时才改变。锁存器多用于集成电路中,在数字电路中作为时序电路的存储元件,在某些运算器电路中有时采用锁存器作为数据暂存器。封装为独立的产品后也可以单独应用,数据有效延迟于时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些应用中,单片机的i/o口上需要外接锁存器。例如,当单片机连接片外存储器时,要接上锁存器,这是为了实现地址的复用。假设,mcu端口其中的8路的i/o管脚既要用于地址信号又要用于数据信号,这时就可以用锁存器先将地址锁存起来。

4.随着集成电路工艺尺寸不断减小,电路性能和集成度不断提升,晶体管特征尺寸的缩减,使得电路中节点间距离减小,电路中敏感节点的临界点电荷量降低,极易因为辐射粒子撞击集成电路表面而造成的软错误所影响。电路器件单元密度的上升带来的电荷共享效应,使得单个粒子撞击造成电路中多个敏感节点的翻转,严重影响电路的稳定可靠运行。

5.由于存储单元在集成电路芯片中占据较大的面积,因此当芯片工作在辐射环境中有辐射引起的软错误的概率较高,对于存储单元的抗辐射加固设计引起了人们的广泛关注。

6.对于存储单元的抗辐射加固设计主要有:(1)系统级加固,采用时间冗余多次执行刷新,或者空间冗余的方式进行模块复制表决输出;(2)电路级加固,采用特殊的加固单元例如c单元或者dice单元等。

7.文献《radiation hardened latch designs for double and triple node upsets》中的锁存器采用了五个四输入c单元构成了一个互锁单元存储数据,采用两个三输入c单元和一个二输入c单元构成输出模块拦截软错误的传播,但是该结构主要有多个多输入c单元构成,仅能够容忍三节点翻转,无法自恢复。同时,由于未采用快速通路,在透明期进行数据传输需要经过多组元器件,大大增加了延迟开销。文献《a novel self-recoverable and triple nodes upset resilience dice latch》中的锁存器由存储模块和输出模块两个部分构成;存储模块由四个dice单元构成,每两个dice之间通过公共节点相互连接;输出模块由每个dice单元的一个输出连接至一个四输入的钟控c单元构成。该结构通过dice结构自身的加固能力以及使用多模冗余技术实现容忍三节点翻转且自恢复能力,但是由于在输出模块采用了c单元作为输出,使得该结构会产生高阻态,影响电路运行

的稳定性,同时采用四个dice单元会导致电路的功耗开销较高。文献《design of a triple-node-upset self-recoverable latch for aerospace applications in harsh radiation environments》中的锁存器由七个软错误拦截单元互锁构成,每一个软错误拦截单元由两个三输入c单元和一个二输入钟控c单元构成,该结构通过软错误拦截单元阻止错误的传播,通过反馈互锁的电路结构将发生翻转的节点恢复过来。但是该结构使用了大量的晶体管,面积开销较大,同时电路中存在大量的反馈互锁环路,增加了功耗开销。文献《a novel tnu error-resilient latch for harsh radiation environment》中的锁存器采用十二个三输入c单元构成环状反馈互锁环路,但是该结构通过c单元拦截软错误继续传播,同时通过反馈连接的方式实现容忍三节点翻转且自恢复的能力。该结构使用了大量的晶体管,导致面开销较高。由于结构内部构建了多条反馈互锁环路同时未采用时钟门控技术,即使时透明期c单元也处于导通状态,增加了功耗开销。

8.综上所述,目前的抗辐射加固锁存器普遍存在着以下问题:1)多数抗辐射加固锁存器设计仅能够容忍多节点翻转,无法自恢复,对于一些功耗要求苛刻的环境,锁存器需要长时间运行在锁存期以降低功耗,错误的逻辑值仍被保留锁存器内部,影响电路运行的稳定性和可靠性;2)容忍多节点翻转且自恢复的锁存器的功耗、面积、延迟开销较高。

技术实现要素:

9.本发明的目的在于一种低开销容忍三节点翻转自恢复的抗辐射加固锁存器,以解决现有技术的抗辐射加固锁存器存在的面积开销高、稳定性差的问题。

10.本发明是通过以下技术方案解决上述技术问题的:

11.一种低开销容忍三节点翻转自恢复的抗辐射加固锁存器,包括:输入单元、存储单元、输出单元;所述的输入单元分别与第一dice单元(11)、第二dice单元(12)、第三dice单元(13)的输入节点连接,所述的输入单元还与输出单元的输出节点连接;所述的存储单元包括:第一dice单元(11)、第二dice单元(12)、第三dice单元(13);第一钟控反相器(21)、第二钟控反相器(22)、第三钟控反相器(23);所述的第一dice单元(11)、第二dice单元(12)、第三dice单元(13)的第一个输出节点通过公共节点(n7)连接在一起;所述的第一dice单元(11)的第二输出节点(n1b)与第一钟控反相器(21)的输入节点连接,第一钟控反相器(21)的输出节点与第二dice单元(12)的第二输入节点(n4)连接;第二dice单元(12)的第二输出节点(n3b)与第二钟控反相器(22)的输入节点连接,第二钟控反相器(22)的输出节点与第三dice单元(13)的第二输入节点(n6)连接;第三dice单元(13)的第二输出节点(n5b)与第三钟控反相器(23)的输入节点连接,第三钟控反相器(23)的输出节点与第一dice单元(11)的第二输入节点(n2)连接;所述的公共节点(n7)与输出单元的输入节点连接。

12.本发明的锁存器的存储单元的每个dice单元的一个输出节点连接至公共节点(n7),每个dice单元的另一个输出节点连接至下一个dice单元的输入节点,构成了三个反馈互锁环路,实现了数据的存储和容忍三节点翻转且自恢复的能力;存储单元仅采用3个dice单元和3个钟控反相器,锁存器的面积小;未采用高阻态的c单元,对高阻态不敏感,因此锁存器的性能更加稳定。

13.进一步地,所述的第一dice单元(11)的第二输出节点(n1b)、第一钟控反相器(21)、第二dice单元(12)的第二输入节点(n4)、公共节点(n7)在锁存器内部形成第一反馈

互锁环路,所述的第二dice单元(12)的第二输出节点(n3b)、第二钟控反相器(22)、第三dice单元(13)的第二输入节点(n6)、公共节点(n7)在锁存器内部形成第二反馈互锁环路,所述的第三dice单元(13)的第二输出节点(n5b)、第三钟控反相器(23)、第一dice单元(11)的第二输入节点(n2)、公共节点(n7)在锁存器内部形成第三反馈互锁环路,三个反馈互锁环路用于在锁存器的发生三节点翻转时自恢复。

14.进一步地,所述的输入单元包括:第一传输门(31)、第二传输门(32)、第三传输门(33)、第四传输门(34)、第五传输门(35)、第六传输门(36)、第七传输门(37);所述的第一dice单元(11)的第一输入节点(n1)与第一传输门(31)的输出节点连接,第一dice单元(11)的第二输入节点(n2)与第二传输门(32)的输出节点连接;所述的第二dice单元(12)的第一输入节点(n3)与第三传输门(33)的输出节点连接,第二dice单元(12)的第二输入节点(n4)与第四传输门(34)的输出节点连接;所述的第三dice单元(13)的第一输入节点(n5)与第五传输门(35)的输出节点连接,第三dice单元(13)的第二输入节点(n6)与第六传输门(36)的输出节点连接;所述的第七传输门(37)的输出节点与输出单元的输出节点连接。

15.进一步地,所述的输出单元包括:第四钟控反相器(24);所述的第七传输门(37)的输出节点与第四钟控反相器(24)的输出节点连接,第四钟控反相器(24)的输入节点与公共节点(n7)连接在一起。

16.进一步地,当锁存器处于透明期时,此时第一传输门(31)、第二传输门(32)、第三传输门(33)、第四传输门(34)、第五传输门(35)、第六传输门(36)、第七传输门(37)均处于导通状态,第一钟控反相器(21)、第二钟控反相器(22)、第三钟控反相器(23)、第四钟控反相器(24)均处于关断状态;输入节点(d)通过第一传输门(31)、第二传输门(32)将数据传输至第一dice单元(11)的第一输入节点(n1)以及第二输入节点(n2),通过第三传输门(33)、第四传输门(34)将数据传输至第二dice单元(12)的第一输入节点(n3)以及第二输入节点(n4),通过第五传输门(35)、第六传输门(36)将数据传输至第三dice单元(13)的第一输入节点(n5)以及第二输入节点(n6),第一dice单元(11)、第二dice单元(12)、第三dice单元(13)分别再将数据传输至第二输出节点(n1b)、第二输出节点(n3b)、第二输出节点(n5b)以及公共节点(n7);输入节点(d)通过第七传输门(37)将数据传输至输出节点(q),此时由于第四钟控反相器(24)处于关断状态,输出节点(q)只能由输入节点(d)驱动。

17.进一步地,当锁存器处于锁存期时,此时第一传输门(31)、第二传输门(32)、第三传输门(33)、第四传输门(34)、第五传输门(35)、第六传输门(36)、第七传输门(37)均处于关断状态,第一钟控反相器(21)、第二钟控反相器(22)、第三钟控反相器(23)、第四钟控反相器(24)均处于导通状态;由于第七传输门(37)处于关断状态,输出节点(q)由锁存器内部公共节点(n7)通过第四钟控反相器(24)驱动;此时由第一dice单元(11)、第二dice单元(12)、第三dice单元(13)进行数据保持。

18.本发明的优点在于:

19.(1)本发明的锁存器的存储单元的每个dice单元的一个输出节点连接至公共节点(n7),每个dice单元的另一个输出节点连接至下一个dice单元的输入节点,构成了三个反馈互锁环路,实现了数据的存储和容忍三节点翻转且自恢复的能力;存储单元仅采用3个dice单元和3个钟控反相器,锁存器的面积小;未采用c单元,对高阻态不敏感,因此锁存器的性能更加稳定;

20.(2)采用时钟门控技术,锁存器在透明期时钟控反相器都处于关断状态,避免了在透明期产生反馈互锁环路和电流竞争,降低锁存器在透明期的功耗;

21.(3)在透明期输出节点(q)直接由输入节点(d)通过第七传输门(37)驱动,建立了输出与输出之间的快速通道,降低了锁存器在透明期的传输延迟;

22.(4)输出单元采用钟控反相器实现,未使用c单元作为表决器,从存储单元到输出单元所经过的电路元器件的数量更少,降低了锁存器的延迟。

附图说明

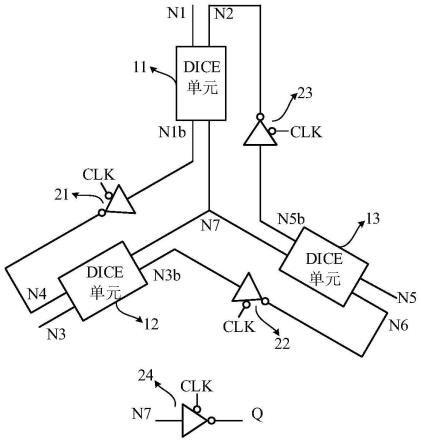

23.图1是本发明实施例一的低开销容忍三节点翻转自恢复的抗辐射加固锁存器的存储单元和输出单元的结构图;

24.图2是本发明实施例一的低开销容忍三节点翻转自恢复的抗辐射加固锁存器的输入单元的结构图;

25.图3是dice单元的内部结构图;

26.图4是钟控反相器的内部结构图。

具体实施方式

27.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

28.下面结合说明书附图以及具体的实施例对本发明的技术方案作进一步描述:

29.实施例一

30.如图1所示,本发明实施例的低开销容忍三节点翻转自恢复的抗辐射加固锁存器的存储单元,包括:三个dice单元,分别为:第一dice单元11、第二dice单元12、第三dice单元13;四个钟控反相器,分别为:第一钟控反相器21、第二钟控反相器22、第三钟控反相器23、第四钟控反相器24。

31.如图2所示,本发明实施例的低开销容忍三节点翻转自恢复的抗辐射加固锁存器的输入单元,包括:七个传输门,分别为:第一传输门31、第二传输门32、第三传输门33、第四传输门34、第五传输门35、第六传输门36、第七传输门37。

32.所述的第一dice单元11的第一输入节点n1与第一传输门31的输出节点连接,第一dice单元11的第二输入节点n2与第二传输门32的输出节点连接;所述的第二dice单元12的第一输入节点n3与第三传输门33的输出节点连接,第二dice单元12的第二输入节点n4与第四传输门34的输出节点连接;所述的第三dice单元13的第一输入节点n5与第五传输门35的输出节点连接,第三dice单元13的第二输入节点n6与第六传输门36的输出节点连接。

33.所述的第一dice单元11、第二dice单元12、第三dice单元13的第一个输出节点通过公共节点n7连接在一起;所述的第一dice单元11的第二输出节点n1b与第一钟控反相器21的输入节点连接,第一钟控反相器21的输出节点与第二dice单元12的第二输入节点n4连接;第二dice单元12的第二输出节点n3b与第二钟控反相器22的输入节点连接,第二钟控反相器22的输出节点与第三dice单元13的第二输入节点n6连接;第三dice单元13的第二输出

节点n5b与第三钟控反相器23的输入节点连接,第三钟控反相器23的输出节点与第一dice单元11的第二输入节点n2连接。

34.所述的第七传输门37的输出节点与第四钟控反相器24的输出节点连接,第四钟控反相器24的输入节点与公共节点n7连接在一起。

35.图3是dice单元的内部结构图,图4是钟控反相器的内部结构图,dice单元和钟控反相器均为现有技术,此处不再赘述。

36.锁存器的运行过程:

37.1、clk和nck分别为系统时钟和负系统时钟,当clk=1、nck=0时,锁存器处于透明期。此时第一传输门31、第二传输门32、第三传输门33、第四传输门34、第五传输门35、第六传输门36、第七传输门37均处于导通状态,第一钟控反相器21、第二钟控反相器22、第三钟控反相器23、第四钟控反相器24均处于关断状态;输入节点d通过第一传输门31、第二传输门32将数据传输至第一dice单元11的第一输入节点n1以及第二输入节点n2,通过第三传输门33、第四传输门34将数据传输至第二dice单元12的第一输入节点n3以及第二输入节点n4,通过第五传输门35、第六传输门36将数据传输至第三dice单元13的第一输入节点n5以及第二输入节点n6,第一dice单元11、第二dice单元12、第三dice单元13分别再将数据传输至第二输出节点n1b、第二输出节点n3b、第二输出节点n5b以及公共节点n7;输入节点d通过第七传输门37将数据传输至输出节点q,此时由于第四钟控反相器24处于关断状态,输出节点q只能由输入节点d驱动。

38.2、当clk=0、nck=1时,锁存器处于锁存期。此时第一传输门31、第二传输门32、第三传输门33、第四传输门34、第五传输门35、第六传输门36、第七传输门37均处于关断状态,第一钟控反相器21、第二钟控反相器22、第三钟控反相器23、第四钟控反相器24均处于导通状态;由于第七传输门37处于关断状态,输出节点q由锁存器内部公共节点n7通过第四钟控反相器24驱动;此时由第一dice单元11、第二dice单元12、第三dice单元13进行数据保持;所述的第一dice单元11的第二输出节点n1b、第一钟控反相器21、第二dice单元12的第二输入节点n4、公共节点n7在锁存器内部形成第一反馈互锁环路,所述的第二dice单元12的第二输出节点n3b、第二钟控反相器22、第三dice单元13的第二输入节点n6、公共节点n7在锁存器内部形成第二反馈互锁环路,所述的第三dice单元13的第二输出节点n5b、第三钟控反相器23、第一dice单元11的第二输入节点n2、公共节点n7在锁存器内部形成第三反馈互锁环路,三个反馈互锁环路用于在锁存器的发生三节点翻转时自恢复。

39.锁存器的三节点翻转自恢复

40.考虑到锁存器中任意三个节点都有发生翻转的可能性,由于结构的对称性,可分为以下六种情况:

41.1、三个dice单元中,每一个dice单元各有一个节点发生翻转

42.例如节点n1、n3、n5发生翻转。由于dice单元自身具有单节点翻转自恢复性,节点n1,n3和n5会分别由第一dice单元11、第二dice单元12、第三dice单元13恢复过来。

43.2、三个dice单元中,有两个dice单元各有两个节点发生翻转,第三个dice单元只有一个节点发生翻转

44.例如节点n3、n5、n7发生翻转。在第一dice单元11中仅有一个节点n7发生翻转,节点n7会通过第一dice单元11恢复过来,接着在第二dice单元12和第三dice单元13中分别仅

剩下一个节点n3和节点n5翻转,节点n3和节点n5分别通过第二dice单元12和第三dice单元13恢复过来。

45.例如节点n3b、n5b、n7发生翻转。dice单元无法容忍相隔节点发生翻转如图2中节点1和节点2之间为相隔节点,节点1b和节点2b之间也为相隔节点,其他节点之间皆为相邻节点,因此节点n3,节点n4,节点n5和节点n6也会受到影响。由于在第一dice单元11中仅有一个节点n7发生翻转,因此节点n7会通过第一dice单元11恢复过来。由于节点n1b未受到影响,节点n1b通过第一钟控反相器21将节点n4恢复过来。由于dice单元具有容忍相邻节点翻转且自恢复的能力,因此节点n3和节点n3b通过第二dice单元12恢复过来,接着节点n3b通过第二钟控反相器22将节点n6恢复过来,最后节点n5和节点n5b通过第三dice单元13恢复过来。

46.3、三个dice单元中,有一个dice单元的三个节点发生翻转,另两个dice单元各只有一个节点发生翻转

47.例如节点n5、n5b、n7发生翻转,节点n2和节点n6也会受到影响。节点n2和节点n7先由第一dice单元11恢复过来。由于节点n3b未受到影响,节点n3b通过第二钟控反相器22将节点n6恢复过来,接着节点n5和节点n5b由第三dice单元13恢复过来。

48.4、三个dice单元中,有一个dice单元中有两个节点发生翻转,一个dice单元中有一个节点发生翻转,另一个dice单元中无节点发生翻转

49.例如节点n1、n2、n4发生翻转,节点n1b和n7也会受到影响。节点n4和n7先由第二dice单元12恢复过来。由于节点n5b未受到影响,节点n5b通过第三钟控反相器23将节点n2恢复过来,接着节点n1和节点n1b由第一dice单元11恢复过来。

50.例如节点组n1、n2、n3发生翻转,节点n1b、n4和n7也会受到影响。节点n7由第三dice单元13恢复过来。由于节点n5b未受到影响,节点n5b通过第三钟控反相器23将节点n2恢复过来,接着n1和n1b由第一dice单元11恢复过来,节点n1b通过第一钟控反相器21将节点n4恢复过来,此时第二dice单元12中仅剩一个节点n3翻转,最后节点n3会通过第二dice单元12恢复过来。

51.5、三个dice单元中,发生翻转的三个节点位于同一个dice单元,另两个dice单元中节点发生翻转

52.例如节点n1,n1b,n2发生翻转,节点n4和n7也会受到影响。第三dice单元13会将节点n7恢复过来,由于节点n5b未受到影响,节点n5b通过第三钟控反相器23将节点n2恢复过来,最后n1和n1b通过第一dice单元11恢复过来,节点n1b通过第一钟控反相器21将节点n4恢复过来。

53.6、输出节点q发生翻转,另两个发生翻转的节点位于锁存器内部

54.通过上述的五种情况可知,本发明的锁存器结构可以容忍位于锁存器内部的任意三个节点发生翻转,如果出现输出节点q发生翻转,另两个发生翻转的节点位于内部节点的情况,则输出节点q由各dice单元中存储正确的数据通过节点n7,再通过第四钟控反相器24将输出节点q恢复过来。

55.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者

替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1