分数时钟分频器的制作方法

分数时钟分频器

1.相关申请的交叉引用

2.本技术要求以下申请的优先权,其内容通过引用整体结合于本技术中:

3.2022年3月31日提交的发明名称为“fractional clock divider[分数时钟分频器]”、专利申请号为17/710,963的美国专利申请;

[0004]

2021年11月22日提交的发明名称为“fractional clock divider[分数时钟分频器]”、专利申请号为63/281,738的美国临时专利申请。

技术领域

[0005]

本文描述的主题涉及时钟生成,更具体地,涉及具有分数分频的时钟生成。

背景技术:

[0006]

在一些发射器和接收器中,混频器分别用于在例如rf和基带频率之间转换和下变频数据。在一些实施例中,可以使用反馈控制的频率生成电路来生成rf频率,该反馈控制的频率生成电路可能对在基本rf频率或其谐波处耦合到其上的噪声是敏感的。因此,在不同于基本rf频率及其谐波的频率下,操作其它电路系统可能是有益的。因此,一些电路使用将基本rf频率除以非整数因子的时钟分频电路。

技术实现要素:

[0007]

一个发明方面是通信电路。该通信电路包括:时钟输入;以及时钟分频器电路,该时钟分频器电路被配置为生成输出时钟信号,该输出时钟信号的基频基本上等于在时钟输入处接收的输入时钟信号的基频除以因子(2n+1)/2n,其中n是整数,并且其中时钟分频器电路被配置为:至少部分地基于输入时钟信号生成2n+1个预对准相移时钟信号;至少部分地基于2n+1个预对准相移时钟信号来生成2n个特定相移时钟信号,其中2n个特定相移时钟信号在相位上基本上以360/2n度而分离;并且至少部分地基于2n个特定相移时钟信号生成输出时钟信号;以及混频器,该混频器被配置为接收输出时钟信号。

[0008]

在一些实施例中,2n+1个预对准相移时钟信号各自的基频等于输入时钟信号的基频的2/(2n+1)倍。

[0009]

在一些实施例中,2n+1个预对准相移时钟信号各自的脉冲宽度基本上等于输入时钟信号的周期。

[0010]

在一些实施例中,基于各自具有等于输入时钟信号的基频的1/(2n+1)倍的基频的2(2n+1)个中间相移时钟信号来生成2n+1个预对准相移时钟信号。

[0011]

在一些实施例中,2n个特定移位时钟信号各自的基频等于输入时钟信号的基频的2/(2n+1)倍。

[0012]

在一些实施例中,2n个特定移位时钟信号各自的脉冲宽度具有基本上等于输入时钟信号的周期的两倍。

[0013]

在一些实施例中,2n个特定移位时钟信号中的每一个对应于2n+1个预对准相移时

钟信号中的一个的相移版本。

[0014]

在一些实施例中,输出时钟信号的脉冲宽度基本上等于输入时钟信号的周期的两倍。

[0015]

另一发明方面是一种时钟分频器电路,该时钟分频器电路被配置为生成输出时钟信号,该输出时钟信号的基频基本上等于输入时钟信号的基频除以因子(2n+1)/2n,其中n是整数。时钟分频器电路包括:2n+1分频电路,该2n+1分频电路被配置为生成2(2n+1)个中间相移时钟信号;2倍频电路,该2倍频电路被配置为接收2(2n+1)个中间相移时钟信号并至少部分地基于所接收的2(2n+1)个中间相移时钟信号来生成2n+1个预对准相移时钟信号;相位调节电路,该相位调节电路被配置为接收2n+1个预对准相移时钟信号并至少部分地基于所接收的2n+1个预对准相移时钟信号来生成2n个特定相移时钟信号,其中2n个特定相移时钟信号在相位上基本上以360/2n度而分离;以及2n/2倍频电路,该2n/2倍频电路被配置为接收2n个特定相移时钟信号并至少部分地基于所接收的2n个特定相移时钟信号来生成输出时钟信号。

[0016]

在一些实施例中,2n+1分频电路包括被配置为响应于输入时钟信号进行移位的第一桶形移位器电路和第二桶形移位器电路。

[0017]

在一些实施例中,2倍频电路包括各自被配置为对多个2(2n+1)中间相移时钟信号执行逻辑“或(or)”功能的多个逻辑电路。

[0018]

在一些实施例中,相位调节电路包括被配置为生成2n+1个预对准相移时钟信号的延迟版本的多个延迟电路。

[0019]

在一些实施例中,控制延迟电路的延迟,以使得2n+1个预对准相移时钟信号的延迟版本中的第一延迟版本与2n+1个预对准相移时钟信号的延迟版本中的第二延迟版本重叠。

[0020]

在一些实施例中,2n/2倍频电路包括各自被配置为对基于2n个特定相移时钟信号生成的多个逻辑信号执行逻辑“或(or)”功能的多个第一逻辑电路。

[0021]

在一些实施例中,2n/2倍频电路包括各自被配置为对多个2n个特定相移时钟信号执行逻辑“与(and)”功能以生成逻辑信号的多个第二逻辑电路。

[0022]

在一些实施例中,输出时钟信号是差分的,并且其中2n/2倍频电路包括被配置成使差分输出时钟信号不重叠的不重叠电路。

[0023]

另一发明方面是一种操作通信电路的方法。该方法包括:利用时钟分频器电路生成输出时钟信号,该输出时钟信号的基频基本上等于输入时钟信号的基频除以因子(2n+1)/2n,其中n是整数,并且其中生成输出时钟信号包括:至少部分基于输入时钟信号来生成2n+1个预对准相移时钟信号;至少部分地基于2n+1个预对准相移时钟信号来生成2n个特定相移时钟信号,其中2n个特定相移时钟信号在相位上基本上以360/2n度而分离;并且至少部分地基于所述2n个特定相移时钟信号来生成输出时钟信号;以及,利用混频器接收输出时钟信号。

[0024]

在一些实施例中,2n+1个预对准相移时钟信号各自的基频等于输入时钟信号的基频的2/(2n+1)倍。

[0025]

在一些实施例中,基于各自具有等于输入时钟信号的基频的1/(2n+1)倍的基频的2(2n+1)个中间相移时钟信号来生成2n+1个预对准相移时钟信号。

[0026]

在一些实施例中,2n个特定移位时钟信号各自的基频等于输入时钟信号的基频的2/(2n+1)倍。

附图说明

[0027]

并入本说明书并构成其一部分的附图示出了本文公开的主题的某些方面,并且与描述一起帮助解释与所公开的实施方式相关联的一些原理。

[0028]

图1是根据一实施例的发射器电路的示意图。

[0029]

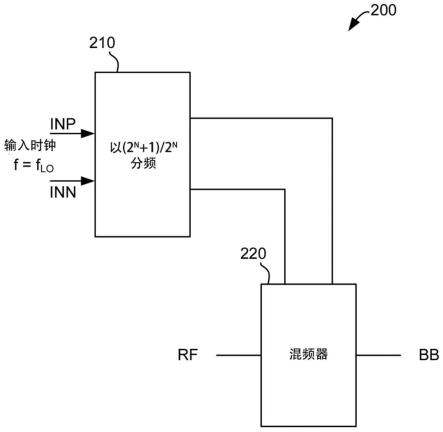

图2示出了根据一些实施例的发射器或接收器电路的一部分的示意图。

[0030]

图3示出了根据一些实施例的时钟分频器电路的示意图。

[0031]

图4示出了根据一些实施例的时钟分频器电路的示意图。

[0032]

图5示出了示出根据一些实施例的图4的时钟分频器电路的操作的波形图。

[0033]

图6示出了根据一些实施例的时钟倍频器和可调延迟电路的示意图。

[0034]

图7和图8示出了示出根据一些实施例的图6的时钟倍频器和可调延迟电路的操作的波形图。

[0035]

图9示出了根据一些实施例的时钟倍频器电路的示意图。

[0036]

图10示出了示出根据一些实施例的图9的时钟倍频器电路的操作的波形图。

[0037]

实际上,相似的附图标记表示相似的结构、特征或元件。

具体实施方式

[0038]

如下面进一步详细讨论的那样,本文讨论的实施例示出了用于生成时钟的电路和方法,这些时钟具有参考时钟的非整数分之一的频率。

[0039]

现在将参照附图描述几个示意性实施例,附图构成了本说明书的一部分。随后的描述仅提供了(多个)实施例,并不旨在限制本公开的范围、适用性或配置。相反,对(多个)实施例的接下来描述将为本领域技术人员提供用于实施一个或多个实施例的实现性描述。应当理解的是,在不脱离本公开的精神和范围的情况下,可以在元件的功能和布置方面进行各种改变。在以下描述中,出于解释的目的,阐述了具体细节,以便提供对某些发明实施例的透彻理解。然而,显而易见地,可以在没有这些具体细节的情况下实施各实施例。附图和描述不旨在是限制性的。词语“示例”或“示例性的”在本文用于表示“用作示例、实例或说明”。本文中描述为“示例性”或“示例”的任何实施例或设计不一定被解释为相比于其他实施例或设计是优选的或有利的。

[0040]

图1是根据一实施例的发射器电路100的实施例的示意图。发射器电路100包括天线或天线阵列110、开关120、rf链路130和控制器140。发射器电路100示出了特定的示例。也可以使用发射器电路的其他实施例。

[0041]

天线或天线阵列110可以是任何天线或天线阵列。例如,在一些实施例中,天线或天线阵列110包括1、2、3、4或更多天线。在一些实施例中,天线或天线阵列110包括线性天线阵列。在一些实施例中,天线或天线阵列110包括二维天线阵列,例如具有多行线性天线阵列。

[0042]

在其中天线或天线阵列110包括一个天线的实施例中,该一个天线可以直接连接到rf链路130,并且可以省略开关120。在其中天线或天线阵列110包括多个天线的实施例

中,每个天线可以直接连接到分开的rf链路。每个rf链路可以具有rf链路130的特征。

[0043]

天线或天线阵列110可以被配置成向接收器电路传输rf信号。rf信号包括利用低频信息信号调制的载波频率下的高频信号。如控制器140所控制那样,例如根据由开关120形成的可编程电连接,高频信号由来自天线或天线阵列110中的天线中的一个来传输。

[0044]

控制器140被配置成向rf链路130提供数字信号,其中数字信号对要由天线或天线阵列110传输的信息信号进行编码。

[0045]

rf链路130包括数模转换器电路(digital to analog converter circuit,dac)132、混频器136、频率合成器134和功率放大器(power amplifier,pa)138。rf链路130仅仅是示例,也可以替代性地使用其他rf链路的实施例。例如,如本领域技术人员所理解的那样,在一些实施例中,可以包括一个或多个放大器和/或过滤器。

[0046]

数字信号由数模转换器132使用本领域已知的技术进行处理,以生成代表数字信号的模拟基带信号(bb信号)。可以使用本领域已知的各种数模转换器结构。

[0047]

混频器136接收从数模转换器132输出的模拟基带信号和由频率合成器134生成的载波频率下的振荡器信号。响应于模拟基带信号和振荡器信号,混频器136使用本领域已知的技术将来自模数转换器132的模拟基带信号上变频为高频信号。可以使用本领域已知的各种混合器结构。由此所得到的高频信号在载波频率处被调制,以便包括低频信息信号的信息。

[0048]

功率放大器138被配置成接收高频信号并且例如根据由开关120形成的可编程电连接将高频信号驱动到来自天线或天线阵列110中的天线中的一个,如由控制器140控制的那样。功率放大器138使用本领域已知的技术将高频信号驱动到天线中的一个。可以使用本领域已知的各种功率放大器结构。

[0049]

如本领域技术人员所理解的那样,使用通信连接(图1中未示出),来自控制器140的控制信号可以控制例如开关120、功率放大器138、频率合成器134、混频器136和数模转换器132的某些可变功能,如本领域技术人员所理解的那样。

[0050]

来自控制器140的控制信号可以例如控制开关120来控制rf链路130利用多个天线中的哪一个来驱动高频信号。

[0051]

在具有各自连接到多个rf链路中的一个rf链路的多个天线的实施例中,控制器140可以为rf链路中的每一个rf链路生成控制信号。

[0052]

图2示出了根据一些实施例的发射器或接收器电路的频率合成器电路的一部分200的示意图。频率合成器电路可以具有与图1的频率合成器134相似或相同的特征。电路部分200包括时钟分频器210,该时钟分频器210例如可以被包括在图1的频率合成器134中。电路部分还包括混频器220。混合器220可以具有与图1的混合器136相似或相同的特征。混频器可以是本领域技术人员已知的任何混频器电路。

[0053]

时钟分频器210接收例如至少部分地由本地振荡器电路生成的输入差分时钟信号inp

–

inn。所接收的输入差分时钟信号具有基频,诸如rf频率。基于所接收的输入差分时钟信号,时钟分频器210生成具有等于基频除以(2n+1)/2n的频率的输出差分时钟信号,其中n是整数。

[0054]

混频器220被配置为接收来自时钟分频器210的输出差分时钟信号,并且例如在rf频率和基带频率之间上变频或下变频信息承载信号。

[0055]

图3示出了根据一些实施例的时钟分频器电路300的示意图。时钟分频器电路300可以用作图2的时钟分频器210中的时钟分频器或者作为其一部分。在一些实施例中,图2的时钟分频器210使用不同于图3中具体示出的电路。

[0056]

图3的时钟分频器电路300将输入差分时钟以9/8分频。可以由本领域的技术人员修改所示出的电路实施例,以将输入差分时钟以其它因子分频,诸如以(2n+1)/2n为特征的任何因子,其中n为整数。在所示的示例实施例中,n等于3。在其他实施方式中,n也可以是不同的数字。

[0057]

图3的时钟分频器电路300接收例如至少部分由本地振荡器电路生成的输入差分时钟信号。所接收的输入差分时钟信号具有基频,诸如rf频率。基于所接收的输入差分时钟信号,时钟分频器电路300生成具有等于基频除以(23+1)/23=9/8的频率的输出差分时钟信号outp

–

outn。

[0058]

图3的时钟分频器电路300包括2n+1分频电路310、2倍频电路320、相位调节电路330和2n/2倍频电路340。

[0059]2n

+1分频电路310接收输入差分时钟信号。在所示的实施例中,2n+1分频电路310将输入差分时钟信号以9分频,并生成各自具有等于基频除以9的频率的18个相移时钟信号。

[0060]

下文讨论了可以用作或部分用作2n+1分频电路310的2n+1分频电路的实施例。也可以使用其他2n+1分频电路。

[0061]

2倍频电路320从2n+1分频电路310接收18个相移时钟信号,并生成9个相移时钟信号,其中9个相移时钟信号中的每一个具有等于基频的2倍除以9的频率。

[0062]

下文讨论了可以用作或部分用作2倍频电路320的2倍频电路的实施例。也可以使用其他2倍频电路。

[0063]

在该实施例中,相位调节电路330从2倍频电路320接收9个相移时钟信号,并生成8个相移时钟信号,其中这8个相移时钟信号在相位上以基本相同的相位而分离。因此,8个相移时钟信号在相位上以等于或基本上等于360/8=45度而彼此分离。

[0064]

下面讨论可以用作或部分用作相位调节电路330的相位调节电路的实施例。也可以使用其他相位调节电路。

[0065]2n

/2倍频电路340从相位调节电路330接收8个相移时钟信号,并生成输出差分时钟信号outp-outn,其中输出差分时钟信号outp

–

outn的频率等于基频乘以1/(2n+1)x2x2n/2/或除以(2n+1)/2n。

[0066]

下文讨论可以用作或部分用作2n/2倍频电路340的2n/2倍频电路的实施例。也可以使用其他2n/2倍频电路。

[0067]

图4示出了根据一些实施例的被配置为将输入时钟除以2n+1的2n+1分频电路400的示意图,其中n=3。2n+1分频电路400可以用作图3的2n+1分频电路310。在一些实施例中,其他2n+1分频电路被用作图3的2n+1分频电路310。

[0068]

图4中示出的2n+1分频电路400接收输入差分时钟信号inp-inn。在所示的实施例中,2n+1分频电路400将输入差分时钟信号以9(2n+1)分频,并生成各自具有等于基频除以9的频率的18 2/(2n+1)个相移时钟信号。此外,相移时钟信号中的每一个的脉冲宽度基本上等于输入时钟信号的周期。

[0069]

在所示的实施例中,2n+1分频电路400包括第一和第二可复位桶形移位器电路410

和420。

[0070]

第一可复位桶形移位器电路410包括九个可复位触发器,该九个可复位触发器各自被配置为响应于输入inn处的时钟输入基于来自前一触发器的输入来生成下一触发器的输出,如所示出的那样。第一可复位桶形移位器电路410被复位,使得输出a3为高电平,而其其它输出a1、a2和a4-a9为低电平。

[0071]

第二可复位桶形移位器电路420包括九个可复位触发器,该九个可复位触发器各自被配置为响应于时钟输入inp基于来自前一触发器的输入来生成下一触发器的输出,如所示出的那样。第二可复位桶形移位器电路410被复位,使得输出b3为高电平,并且其其他输出b1、b2和b4

–

b9为低电平。

[0072]

图5示出了示出根据一些实施例的图4的时钟分频器电路400的操作的波形图。

[0073]

如所示出的那样,在复位信号cdn1和cdn2为低电平时,输出b3和a3为高电平,而其它输出b1、b2、b4-b9、a1、a2和a4-a9为低电平。在复位信号resetn变为高电平之后的输入时钟inp的两个下降沿,复位信号cdn2变为高电平。此外,在复位信号cdn2变为高电平之后的输入时钟inn的一个下降沿,复位信号cdn1变为高电平。此后,在复位信号cdn1为高电平时,第一桶形移位器电路410的ax输出中的一个为高电平,其中ax输出中的哪一个为高电平从输出a4开始旋转通过ax输出,并且响应于输入时钟inn的每个后续下降沿而改变。此外,在复位信号cdn2为高电平时,第二桶形移位器电路420的bx输出中的一个为高电平,其中bx输出中的哪一个为高电平从输出b4开始旋转通过bx输出,并且响应于输入时钟inp的每个后续下降沿而改变。

[0074]

图6示出了根据一些实施例的时钟倍频器电路610和可调延迟电路620的示意图。时钟倍频器电路610可以用作图3的2倍频电路320或者用作其一部分。在一些实施例中,其他时钟倍频器电路被用作图3的2倍频电路320或用作其一部分。可调延迟电路620可以用作图3的相位调节电路330的一部分或用作其一部分。在一些实施例中,其他可调延迟电路被用作图3的相位调节电路330或用作其一部分。

[0075]

时钟倍频器电路610和可调延迟电路620形成九个信号路径,该九个信号路径各自包括时钟倍频器电路610的九(2n+1)个2倍频部分中的一个和可调延迟电路620的九个相位调节部分中的一个。

[0076]

时钟倍频器电路610的每个2倍频部分接收来自第一桶形移位器电路410的一个输出ax作为第一输入,以及来自第二桶形移位器电路420的一个输出bx作为第二输入。在该实施例中,每个2倍频部分包括对第一和第二输入执行或非(nor)逻辑功能的或非门(nor gate)。相应地,时钟倍频器电路610的2倍频部分各自从时钟分频器电路400接收18个相移时钟信号中的两个。此外,时钟倍频器电路610的2倍频部分各自生成具有等于基频的2倍除以9的频率的倍频时钟信号/(bx+ax)或/(ax+bx)。

[0077]

时钟倍频器电路620的九(2n+1)个相位调节部分中的每一个接收倍频时钟信号/(bx+ax)或/(ax+bx)中的一个,并生成相移时钟信号d/(bx+ax)或d/(ax+bx)。每个相位调节部分包括多个缓冲器或反相器级,其中每个级的延迟受到控制信号delay的影响或控制。

[0078]

使用控制信号delay来控制缓冲器或反相器级的延迟,使得相移时钟信号d/(bx+ax)或d/(ax+bx)中的第一个相移时钟信号重叠于相移时钟信号d/(bx+ax)或d/(ax+bx)中的最后一个相移时钟信号。相应地,在所示的实施例中,九个相位调节部分接收由九个2倍

频部分生成的九个相移时钟信号d/(bx+ax)或d/(ax+bx),并生成九个相移时钟信号d/(bx+ax)或d/(ax+bx),其中相移时钟信号d/(bx+ax)或d/(ax+bx)中的两个重叠。相应地,九个相位调节部分生成八个特定相移时钟信号d/(bx+ax)或d/(ax+bx),其中八个特定相移时钟信号d/(bx+ax)或d/(ax+bx)在相位上以等于或基本上等于360/8=45度而分离。

[0079]

图7示出了示出根据一些实施例的图6的时钟倍频器电路610的2倍频部分的倍频时钟信号输出/(bx+ax)或/(ax+bx)的波形图。如所示出的那样,倍频时钟信号/(bx+ax)或/(ax+bx)中的每一个的频率等于基频的2倍除以9(2n+1)。此外,倍频时钟信号/(bx+ax)或/(ax+bx)中的每一个的脉冲宽度基本上等于输入时钟信号的周期。

[0080]

图8示出了示出了根据一些实施例的图6的时钟倍频器电路610的相位调节部分的相移时钟信号d/(bx+ax)或d/(ax+bx)的波形图。如所示出的那样,相移时钟信号中的第一相移时钟信号db5+a9对准于并且重叠于相移时钟信号中的相移时钟信号db9+a4。相应地,八个特定相移时钟信号db5+a9、da5+b1、db6+a1、da6+b2、db7+a2、da7+b3、db8+a3和da8+b4在相位上以相同的相位而分离,该相同的相位等于或基本上等于360/8=45度。另外,八个特定相移时钟信号db5+a9、da5+b1、db6+a1、da6+b2、db7+a2、da7+b3、db8+a3和da8+b4中的每一个的频率等于基频的2倍除以9(2n+1),并且,八个特定相移时钟信号db5+a9、da5+b1、db6+a1、da6+b2、db7+a2、da7+b3、db8+a3和da8+b4中的每一个的脉冲宽度基本上等于输入时钟信号的周期。

[0081]

相移时钟信号db5+a9和db9+a4的对准是通过使用控制信号delay来控制可调延迟电路620的相位调节部分的缓冲器或反相器级的延迟来进行的。例如,控制信号delay可以是模拟电压,并且缓冲器或反相器级可以具有受控制信号delay的模拟电压影响或控制的延迟。控制信号delay的模拟电压可以利用相位检测电路生成,该相位检测电路检测相移时钟信号db5+a9和db9+a4之间的相位差,并基于所检测到的相位差增加或减小控制信号delay的模拟电压,其中控制信号delay的模拟电压方面的增加或减小降低了相移时钟信号db5+a9和db9+a4之间的相位差。相位检测电路可以例如包括相位频率检测器pfd电路等。

[0082]

图9示出了根据一些实施例的时钟倍频器电路900的示意图。时钟倍频器电路900可以用作图3的2n/2倍频电路340或者用作其一部分。在一些实施例中,其他时钟倍频器电路被用作图3的2n/2倍频电路340或用作其一部分。在这个实施例中,时钟倍频器电路将时钟的频率乘以2n/2=4。

[0083]

时钟倍频器电路900的与门910对由图6的时钟倍频器电路610的相位调节部分生成的相邻相移时钟信号db5+a9和da5+b1、db6+a1和da6+b2、db7+a2和da7+b3、db8+a3和da8+b4、da5+b1和db6+a1、da6+b2和db7+a2、da7+b3和db8+a3以及da8+b4和db5+a9执行与(and)逻辑功能,以生成八个时钟信号cp1、cp2、cp3、cp4、cn1、cn2、cn3和cn4。另外,八个时钟信号cp1、cp2、cp3、cp4、cn1、cn2、cn3和cn4中的每一个的频率等于基频的2倍除以9(2n+1),并且八个时钟信号cp1、cp2、cp3、cp4、cn1、cn2、cn3和cn4中的每一个的脉冲宽度基本上等于输入时钟信号的半个周期。

[0084]

时钟倍频器电路900的或门(or gate)920对包括时钟信号cp1、cp2、cp3和cp4的第一组时钟信号执行第一或(or)逻辑功能,以生第一或逻辑信号cp,并对包括时钟信号cn1、cn2、cn3和cn4的第二组时钟信号执行第二或(or)逻辑功能,以生成第二或逻辑信号cn。另外,时钟信号cp和cn中的每一个的频率等于基频的4(2n)倍除以9(2n+1),并且时钟信号cp和

cn中的每一个的脉冲宽度基本上等于输入时钟信号的半个周期。

[0085]

时钟倍频器电路900的交叉耦合的或非门(nor gate)930接收第一和第二“或(or)”时钟信号cp和cn,并为反相器940生成信号,基于这些信号,反相器940生成输出时钟信号outp和outn。交叉耦合的与非门930形成非重叠电路,并确保相邻脉冲输出时钟信号outp和outn理想地不重叠。另外,输出时钟信号outp和outn中的每一个的频率等于基频的4(2n)倍除以9(2n+1),并且输出时钟信号outp和outn中的每一个的脉冲宽度基本上等于输入时钟信号的半个周期。

[0086]

图10示出了示出根据一些实施例的图9的时钟倍频器电路900的操作的波形图。

[0087]

如图所示,由于与门(and gates)910的“与”运算,cp1至cp4和cn1至cn4时钟信号的正脉冲比图8的相移时钟信号db5+a9、da5+b1、db6+a1、da6+b2、db7+a2、da7+b3、db8+a3和da8+b4更窄。此外,由于“或门(or gates)”的“或”运算,输出时钟信号outp和outn的频率为图8的相移时钟信号db5+a9、da5+b1、db6+a1、da6+b2、db7+a2、da7+b3、db8+a3和da8+b4的频率的四倍。

[0088]

相应地,在该实施例中,通过利用2n+1分频电路400将输入差分时钟inp

–

inn以(2n+1)分频,利用时钟倍频器电路610的2倍频部分进行2倍频,利用可调延迟电路620的相位调节部分进行相位调节以生成2n个特定相移时钟、以及利用倍频器电路900以2n/2倍频,来生成输出时钟信号outp和outn。

[0089]

结果,输出差分时钟信号的频率等于输入差分时钟信号的基频乘以2x2n/2/(2n+1)或除以(2n+1)/2n。结果,输出差分时钟信号的基频和至少其低阶谐波不同于输入差分时钟信号的基频和至少其低阶谐波。

[0090]

本文描述的主题的一个或多个方面或特征可以在数字电子电路系统、集成电路系统、专门设计的专用集成电路(application specific integrated circuit,asic)、现场可编程门阵列(field programmable gate array,fpga)计算机硬件、固件、软件和/或其组合中实现。这些不同的方面或特征可以包括在可编程系统上可执行和/或可解释的一个或多个计算机程序中的实施方式,该可编程系统包括至少一个可编程处理器,其可以是专用或通用的,被耦合以从存储系统、至少一个输入设备和至少一个输出设备接收数据和指令,以及向其传输数据和指令。可编程系统或计算系统可以包括客户端和服务器。客户端和服务器通常彼此远离,并且通常通过通信网络进行交互。客户端和服务器的关系是通过运行在各自的计算机上并彼此具有客户机-服务器关系的计算机程序产生的。

[0091]

这些计算机程序(其也可以被称为程序、软件、软件应用、应用、组件或代码)包括用于可编程处理器的机器指令,并且可以以高级过程语言、面向对象的编程语言、函数编程语言、逻辑编程语言和/或以汇编/机器语言来实施。如本文所用,术语“机器可读介质”指的是用于向可编程处理器提供机器指令和/或数据的任何计算机程序产品、装置和/或设备(例如磁盘、光盘、存储器和可编程逻辑器件(programmable logic device,pld)),包括接收机器指令作为机器可读信号的机器可读介质。术语“机器可读信号”是指用于向可编程处理器提供机器指令和/或数据的任何信号。机器可读介质可以非瞬态地存储这样的机器指令,例如非瞬态固态存储器或磁硬盘驱动器或任何等效的存储介质那样。机器可读介质可以替代性地或附加地以瞬时方式存储这样的机器指令,例如处理器高速缓存或与一个或多个物理处理器核心相关联的其他随机存取存储器那样。

[0092]

在上面的描述和权利要求中,诸如

“……

中的至少一个”或

“……

中的一个或多个”的短语可能在元素(元件)或特征的联合列表之后出现。术语“和/或”也可以出现在两个或多个元件或特征的列表中。除非其使用的上下文隐式地或显式地矛盾,否则这样的短语旨在单独地表示列出的元素或特征中的任何一个,或者表示列出的元素或特征中的任何一个与其他列出的元素或特征中的任何一个组合。例如,短语“a和b中的至少一个”、“a和b中的一个或多个”、和“a和/或b”各自旨在表示“仅a、仅b、或a和b一起”。类似的解释也旨在用于包括三个或更多个项的列表。例如,短语“a、b和c中的至少一个”、“a、b和c中的一个或多个”、和“a、b和/或c”各自旨在表示“仅a、仅b、仅c、a和b一起、a和c一起、b和c一起、或a和b和c一起”。上文和权利要求中的术语“基于”的使用旨在表示“至少部分基于”,使得未引用的特征或元素也是允许的。

[0093]

根据期望的配置,本文描述的主题可以体现在系统、装置、方法和/或物品中。前面描述中阐述的实施方式并不代表与本文描述的主题一致的所有实施方式。相反,它们仅仅是与所描述的主题相关的方面一致的一些示例。尽管上面已经详细描述了一些变行,但是其他修改或添加也是可能的。特别地,除了在此阐述的那些之外,可以提供另外的特征和/或变型。例如,上述实施方式可以针对所公开特征的各种组合和子组合,和/或上面公开的几个另外的特征的组合和子组合。此外,附图中描绘的和/或本文描述的逻辑流程不一定需要所示的特定顺序或连续顺序来实现期望的结果。其他实施方式也可能落入权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1