具有重迭式多重回路的电压控制环型振荡器的制作方法

1.本发明是关于一种具有重迭式多重回路的电压控制环型振荡器;特别是关于利用每两个邻接延迟单元之间连接形成一双组合延迟单元组,且每两个相邻该双级电压控制环型振荡器之间形成重迭共同连接同一延迟单元之电压控制环型振荡器。

背景技术:

2.习用电压控制环型振荡器,如中国台湾发明专利公开案第200814521号,其揭示一种使用双延迟路径之压控环形振荡器,其包含:n个延迟模块,每一延迟模块具有一第一组信号输入端、一第二组信号输入端与两信号输出端,其中此第一组、第二组信号输入端分别包含一第一极性信号输入端与一第二极性信号输入端,且此两信号输出端包含一第一极性与一第二极性信号输出端;其中每一延迟模块之第一组信号输入端耦接前一级延迟模块之输出端,每一延迟模块之第二组信号输入端耦接前一级延迟模块之第一组信号输入端,n≧2且n为自然数。藉此,提高振荡器之振荡频率、减少相位噪声,并改善振荡器之振荡频率随串级级数增加而下降之缺点。然而,该第200814521号之压控环形振荡器采用两组差动输入的延迟模块,因此该压控环形振荡器具有增加电路复杂度之缺点。

3.另一习用电压控制环形振荡器,如中国台湾发明专利公开案第200503421号,其揭示一种环状振荡电路,其目的在解决高频率时波形失真之问题,其特征为:复数个差动放大器之环状路径,使差动放大器之初级与最终级靠近配置,其结果可将相邻接之差动放大器彼此之间的距离尽可能作成均等。藉此,可将差动放大器间的信号线的长度作成均等,使传送延迟一致,其结果即输出单一频率性高的振荡信号。然而,该第200814521号之控制电路需要提供两个控制讯号至该环状振荡电路之差动放大器,因此该环状振荡电路具有增加电路复杂度之缺点。

4.另一习用电压控制环型振荡器,如美国发明专利公开案第20070008043号,其揭示数个延迟单元[delay cell],其应用于电压控制环型振荡器。然而,数个该延迟单元仅单纯串接形成多级延迟单元,因而该第20070008043号之电压控制环型振荡器仍具有习用环型振荡器无法保持高振荡频率之缺点。

[0005]

另一习用电压控制环型振荡器,如美国发明专利公开案第20070040622号,其揭示一差动放大电路应用于一环型振荡器。该环型振荡器具有两级串接差动放大器,因此其仍具有习用环型振荡器相位噪声高及输出振幅小之缺点。

[0006]

另一习用电压控制环型振荡器,如美国发明专利公开案第20080231378号,其揭示一环型振荡器。该环型振荡器具有数个延迟单元[delay cell],且该环型振荡器另额外需要一控制电路,因此虽有较宽的频率调谐范围,但其仍具有构造复杂及无法保持高振荡频率的缺点。

[0007]

另一习用电压控制环型振荡器,如美国发明专利公开案第20050068114号,其揭示一环型振荡电路。该环型振荡电路具有数个延迟单元[delay cell],且该环型振荡电路另额外需要一参考电压电路[reference voltage circuit],因此其仍具有构造复杂的缺点。

[0008]

前述中国台湾发明专利公开案第200814521号、第200503421号、美国发明专利公开案第20070008043号、第20070040622号、第20080231378号及第20050068114号仅为本发明技术背景之参考及说明目前技术发展状态而已,其并非用以限制本发明之范围。

[0009]

习用电压控制环型振荡器仍存在有必要进一步改善其特性之需求,以保持高振荡频率、增加输出振幅及降低相位杂。因此,习用电压控制环型振荡器仍可利用其它适当技术手段[例如:其它连接方式]改善其特性,以满足前述潜在需求。

[0010]

有鉴于此,本发明为了满足上述需求,其提供一种具有重迭式多重回路的电压控制环型振荡器,其利用每两个邻接延迟单元之间连接形成一双级电压控制环型振荡器,且每两个相邻该双级电压控制环型振荡器之间形成重迭共同连接同一延迟单元,以构成一重迭式多重回路,以达成保持高振荡频率、增加输出振幅及降低相位噪声之目的。

技术实现要素:

[0011]

本发明之主要目的系提供一种具有重迭式多重回路的电压控制环型振荡器,其利用每两个邻接延迟单元之间连接形成一双级电压控制环型振荡器,且每两个相邻该双级电压控制环型振荡器之间形成重迭共同连接同一延迟单元,以构成一重迭式多重回路,以达成保持高振荡频率、增加输出振幅及降低相位噪声的目的。

[0012]

为了达成上述目的,本发明之具有重迭式多重回路的电压控制环型振荡器包含一第一延迟单元、一第二延迟单元及一第三延迟单元。该第一延迟单元具有差动输入端及差动输出端,该第二延迟单元具有差动输入端及差动输出端,该第三延迟单元具有差动输入端及差动输出端。该第一延迟单元之差动输出端连接至该第二延迟单元之差动输入端,且该第二延迟单元之差动输出端连接至该第一延迟单元之差动输入端,以形成一第一双级电压控制环型振荡器。该第二延迟单元之差动输出端连接至该第三延迟单元之差动输入端,且该第三延迟单元之差动输出端连接至该第二延迟单元之差动输入端,以形成一第二双级电压控制环型振荡器。该第一双级电压控制环型振荡器及第二双级电压控制环型振荡器共同连接该第二延迟单元。

[0013]

本发明较佳实施例之该电压控制环型振荡器另包含一第四延迟单元,其具有差动输入端及差动输出端;该第三延迟单元之差动输出端连接至该第四延迟单元之差动输入端,且该第四延迟单元之差动输出端连接至该第三延迟单元之差动输入端,以形成一第三双级电压控制环型振荡器。该第二双级电压控制环型振荡器及第三双级电压控制环型振荡器共同连接该第三延迟单元。

[0014]

本发明较佳实施例之该电压控制环型振荡器之延迟单元数量n≧3。

[0015]

本发明较佳实施例之该电压控制环型振荡器可应用于一锁相回路。

附图说明

[0016]

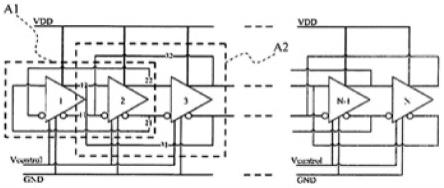

图1:本发明较佳实施例具有重迭式多重回路的电压控制环型振荡器之示意图。

[0017]

图2:本发明较佳实施例具有重迭式多重回路的电压控制环型振荡器选择采用延迟单元之架构示意图。

[0018]

图3:本发明较佳实施例具有重迭式多重回路的电压控制环型振荡器在各级延迟单元仿真产生之振荡频率与控制电压之关系曲线图。

[0019]

图4:本发明较佳实施例具有重迭式多重回路的电压控制环型振荡器在各级延迟单元仿真产生之相位噪声与控制电压之关系曲线图。

[0020]

图5:本发明较佳实施例具有重迭式多重回路的电压控制环型振荡器在各级延迟单元仿真产生之峰对峰值与控制电压之关系曲线图。

[0021]

附图标记说明:

[0022]

1...第一延迟单元

[0023]

2...第二延迟单元

[0024]

3...第三延迟单元

[0025]

n-1...第n-1延迟单元

[0026]

n...第n延迟单元

[0027]

11、12、21、22、31、32...线路

[0028]

a1...第一双级电压控制环型振荡器

[0029]

a2...第二双级电压控制环型振荡器

[0030]

m1、m2、m3、m4、m5、m6、m7...晶体管

具体实施方式

[0031]

为了充分了解本发明,于下文将例举较佳实施例并配合所附图式作详细说明,且其并非用以限定本发明。

[0032]

本发明较佳实施例之具有重迭式多重回路的电压控制环型振荡器可应用一般需要高频及低相位噪声之讯号处理系统;举例而言,本发明较佳实施例之具有重迭式多重回路的电压控制环型振荡器可应用于一锁相回路[phase-locked loop,pll]或其它功能回路,但其并非用以限定本发明之适用范围。

[0033]

图1揭示本发明较佳实施例之具有重迭式多重回路的电压控制环型振荡器之架构示意图。请参照图1所示,本发明之具有重迭式多重回路的电压控制环型振荡器包含数个延迟单元。数个该延迟单元之间进行串接,以增加该电压控制环型振荡器之振幅及减少该电压控制环型振荡器之相位噪声[phase noise]。将数个该延迟单元定义为一第一延迟单元1、一第二延迟单元2、一第三延迟单元3、

…

一第n-1延迟单元n-1及一第n延迟单元n。是以,本发明较佳实施例之具有重迭式多重回路的电压控制环型振荡器具有n级[stage]延迟单元。

[0034]

请再参照图1所示,该第一延迟单元1具有差动输入端,其用以输入正负极性讯号,且该第一延迟单元1具有差动输出端,其用以输出正负极性讯号。相对的,该第二延迟单元2亦具有差动输入端及差动输出端,其用以输入正负极性讯号及输出正负极性讯号。相对的,该第三延迟单元3亦具有差动输入端及差动输出端,其用以输入正负极性讯号及输出正负极性讯号。

[0035]

请再参照图1所示,该第一延迟单元1之差动输出端经由线路11、12连接至该第二延迟单元2之差动输入端,且该第二延迟单元2之差动输出端经由线路21、22连接至该第一延迟单元1之差动输入端,以形成一第一双级电压控制环型振荡器a1。该第二延迟单元2之差动输出端连接至该第三延迟单元3之差动输入端,且该第三延迟单元3之差动输出端经由线路31、32连接至该第二延迟单元2之差动输入端,以形成一第二双级电压控制环型振荡器

a2。该第一双级电压控制环型振荡器a1及第二双级电压控制环型振荡器a2共同连接该第二延迟单元2,即该第一双级电压控制环型振荡器a1及第二双级电压控制环型振荡器a2利用该第二延迟单元2形成重迭构造。

[0036]

同理,该电压控制环型振荡器另包含一第四延迟单元,其具有差动输入端及差动输出端;该第三延迟单元3之差动输出端连接至该第四延迟单元之差动输入端,且该第四延迟单元之差动输出端连接至该第三延迟单元3之差动输入端,以形成一第三双级电压控制环型振荡器。因此,该第二双级电压控制环型振荡器a2及第三双级电压控制环型振荡器共同连接该第三延迟单元3,即该第二双级电压控制环型振荡器a2及第三双级电压控制环型振荡器利用该第三延迟单元3形成重迭构造。

[0037]

请再参照图1所示,本发明较佳实施例之该电压控制环型振荡器之延迟单元数量n≧3,即该电压控制环型振荡器具有至少三个该延迟单元1、2、3。当本发明较佳实施例之该电压控制环型振荡器之延迟单元数量为n时,该电压控制环型振荡器具有n-1个双组合延迟单元组。

[0038]

图2揭示本发明较佳实施例之具有重迭式多重回路的电压控制环型振荡器选择采用延迟单元之架构示意图。请参照图2所示,该电压控制环型振荡器可选择一般延迟单元,于此不予赘述该延迟单元之构造,但其并非用以限制本发明。

[0039]

图3揭示本发明较佳实施例之具有重迭式多重回路的电压控制环型振荡器在3级[3stages]、4级[4stages]、5级[5stages]、6级[6stages]、7级[7stages]、8级[8stages]延迟单元仿真产生之振荡频率与控制电压关系之曲线图。图3另揭示一般电压控制环型振荡器在第2级延迟单元仿真产生之振荡频率与控制电压关系之曲线图。请参照图3所示,具2级[2stages]延迟单元之一般电压控制环型振荡器在控制电压1.0v至3.5v之间仿真产生之振荡频率与控制电压之关系曲线显示为最低振荡频率。反观,依本发明较佳实施例之具3级、4级、5级、6级、7级、8级延迟单元之电压控制环型振荡器在控制电压1.0v至3.5v之间仿真产生之振荡频率与控制电压之关系曲线,其显示电压控制环型振荡器随着依序3级、4级、5级、6级、7级、8级延迟单元之增加,而相对增加其振荡频率。

[0040]

图4揭示本发明较佳实施例之具有重迭式多重回路的电压控制环型振荡器在3级[3stages]、4级[4stages]、5级[5stages]、6级[6stages]、7级[7stages]、8级[8stages]延迟单元仿真产生之相位噪声与控制电压关系之曲线图。图4另揭示一般电压控制环型振荡器在第2级延迟单元仿真产生之相位噪声与控制电压关系之曲线图。请参照图4所示,具2级[2stages]延迟单元之一般电压控制环型振荡器在控制电压1.0v至3.5v之间仿真产生之相位噪声与控制电压之关系曲线显示为最高相位噪声。反观,依本发明较佳实施例之具3级、4级、5级、6级、7级、8级延迟单元之电压控制环型振荡器在控制电压1.0v至3.5v之间仿真产生之相位噪声与控制电压之关系曲线,其显示电压控制环型振荡器随着依序3级、4级、5级、6级、7级、8级延迟单元之增加,而相对降低其相位噪声。

[0041]

图5揭示本发明较佳实施例之具有重迭式多重回路的电压控制环型振荡器在3级[3stages]、4级[4stages]、5级[5stages]、6级[6stages]、7级[7stages]、8级[8stages]延迟单元仿真产生之峰对峰值[vp-p]与控制电压关系之曲线图。图5另揭示一般电压控制环型振荡器在第2级延迟单元仿真产生之峰对峰值与控制电压关系之曲线图。请参照图5所示,具2级延迟单元[2stages]之一般电压控制环型振荡器在控制电压1.0v至3.5v之间模拟

产生之峰对峰值与控制电压之关系曲线显示为最低峰对峰值。反观,依本发明较佳实施例之具3级、4级、5级、6级、7级、8级延迟单元之电压控制环型振荡器在控制电压1.0v至3.5v之间模拟产生之峰对峰值与控制电压之关系曲线,其显示电压控制环型振荡器随着依序3级、4级、5级、6级、7级、8级延迟单元之增加,而相对增加其峰对峰值。

[0042]

上述实验数据为在特定条件之下所获得的初步实验结果,其仅用以易于了解或参考本发明之技术内容而已,其尚需进行其他实验。该实验数据及其结果并非用以限制本发明之权利范围。

[0043]

前述较佳实施例仅举例说明本发明及其技术特征,该实施例之技术仍可适当进行各种实质等效修饰及/或替换方式予以实施;因此,本发明之权利范围须视后附申请专利范围所界定之范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1