显示基板及其制备方法、显示装置与流程

本文涉及但不限于显示,具体涉及一种显示基板及其制备方法、显示装置。

背景技术:

1、有机发光二极管(organic light emitting diode,简称oled)和量子点发光二极管(quantum-dot light emitting diodes,简称qled)为主动发光显示器件,具有自发光、广视角、高对比度、低耗电、极高反应速度、轻薄、可弯曲和成本低等优点。随着显示技术的不断发展,以oled或qled为发光器件、由薄膜晶体管(thin film transistor,简称tft)进行信号控制的柔性显示装置(flexible display)已成为目前显示领域的主流产品。

2、随着显示技术的不断发展,oled技术越来越多的应用于多种显示场景。例如,当oled技术应用于需要对环境光进行检测的显示装置中时,需要显示基板设置有透光区,使显示基板具有一定的透过率,以保证设置在显示基板下方的环境光感光器件能够顺利工作。

技术实现思路

1、以下是对本文详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本公开所要解决的技术问题是,提供一种显示基板及其制备方法、显示装置,以提高显示基板的透过率。

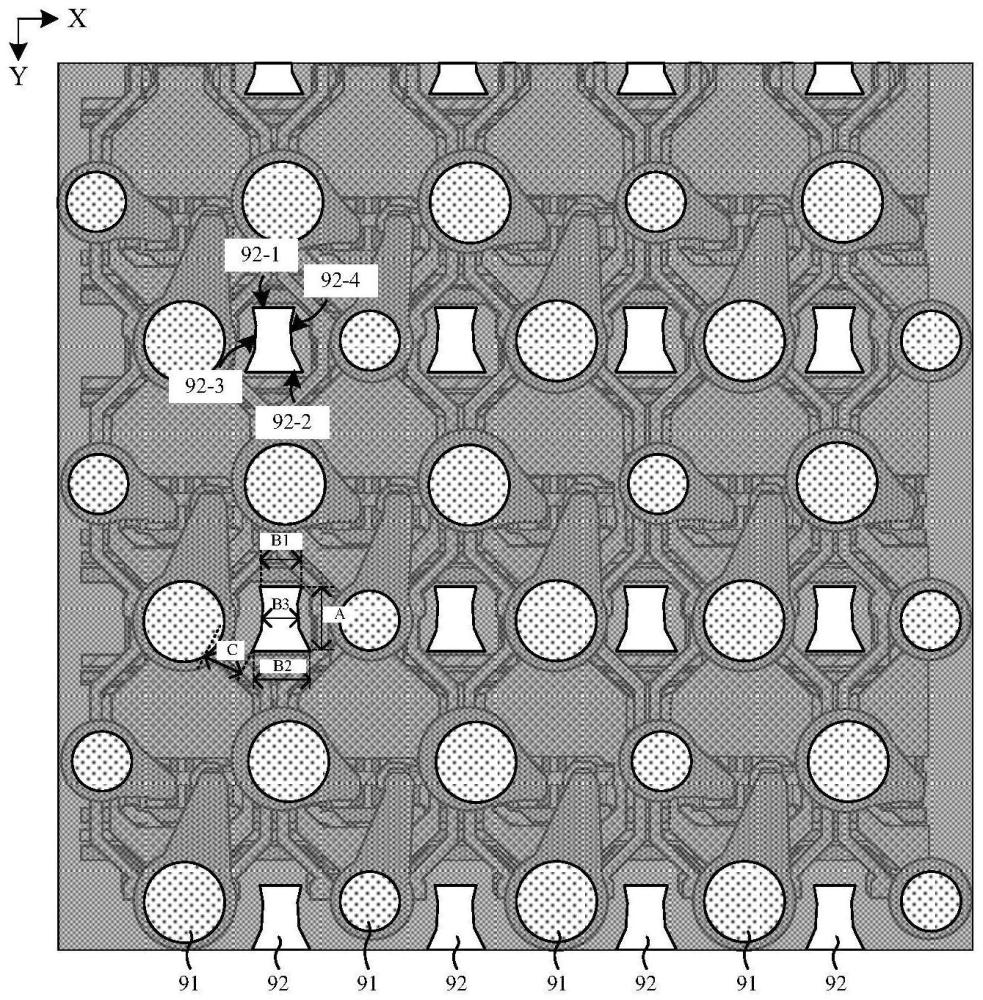

3、一方面,本公开提供了一种显示基板,包括设置在基底上的驱动电路层和设置在所述驱动电路层远离所述基底一侧的发光结构层,所述驱动电路层包括构成多个单元行和多个单元列的多个电路单元,所述发光结构层包括多个发光单元,至少一个电路单元包括像素驱动电路,至少一个发光单元包括设置在所述驱动电路层远离所述基底一侧的阳极和设置在所述阳极远离所述基底一侧的像素定义层,所述阳极与对应电路单元的像素驱动电路连接,所述像素定义层设置有像素开口,所述像素开口暴露出所述阳极;至少一个发光单元的像素定义层设置有透光开口,所述透光开口在所述基底上的正投影面积为0.09s至0.15s,s为所述电路单元在所述基底上的正投影面积。

4、在示例性实施方式中,所述透光开口的透过率大于或等于60%。

5、在示例性实施方式中,在平行于所述基底的平面上,至少一个透光开口的形状为梯形状,包括沿着所述单元行方向延伸的第一横边和第二横边、以及分别连接所述第一横边和第二横边的第一竖边和第二竖边;沿着所述单元列方向,所述第一横边和第二横边之间的距离为0.2l至0.3l,l为所述电路单元在所述单元列方向的尺寸。

6、在示例性实施方式中,沿着所述单元行方向,所述第一横边的宽度为0.3k至0.4k,所述第二横边的宽度为0.4k至0.5k,k为所述电路单元在所述单元行方向的尺寸。

7、在示例性实施方式中,所述第一竖边为向着所述第二竖边凸出的第一弧线形,所述第二竖边为向着所述第一竖边凸出的第二弧线形,在所述单元行方向,所述第一竖边与所述第二竖边之间的最小距离为0.3k至0.4k,k为所述电路单元在所述单元行方向的尺寸。

8、在示例性实施方式中,所述透光开口设置在所述单元行方向相邻的像素开口之间,所述像素开口靠近所述透光开口一侧的边缘与所述透光开口靠近所述像素开口一侧的边缘之间的最小距离为0.4k至0.5k,k为所述电路单元在所述单元行方向的尺寸。

9、在示例性实施方式中,至少一个单元行中设置有至少一个空白区,所述透光开口在所述基底上的正投影位于所述空白区在所述基底上的正投影的范围之内。

10、在示例性实施方式中,至少一个电路单元的像素驱动电路包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管和存储电容;所述第一晶体管的栅电极与第三扫描信号线连接,所述第一晶体管的第一极与第一初始信号线连接;所述第二晶体管的栅电极与第四扫描信号线连接,所述第二晶体管的第一极与所述第一晶体管的第二极连接;所述第四晶体管的栅电极与第一扫描信号线连接,所述第四晶体管的第一极与数据信号线连接;所述第七晶体管的栅电极与第二扫描信号线连接,所述第七晶体管的的第一极与所述第二初始信号线连接;第m单元行的第一扫描信号线设置在所述存储电容远离第m+1单元行的一侧,第m单元行的第三扫描信号线设置在所述第一扫描信号线远离所述存储电容的一侧,所述空白区设置在所述第一扫描信号线和第三扫描信号线之间,m为大于或等于1的正整数。

11、在示例性实施方式中,在所述单元列方向,所述空白区的长度为0.2l至0.3l,l为所述电路单元在所述单元列方向的尺寸。

12、在示例性实施方式中,所述空白区设置在第2i单元列与第2i+1单元列之间,i为大于或等于1的正整数。

13、在示例性实施方式中,所述空白区设置在第2i单元列的数据信号线与第2i+1单元列的数据信号线之间。

14、在示例性实施方式中,在所述单元行方向,所述空白区的宽度为0.8k至0.9k,k为所述电路单元在所述单元行方向的尺寸。

15、在示例性实施方式中,所述第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管和第七晶体管在所述基底上的正投影与所述空白区在所述基底上的正投影没有交叠。

16、在示例性实施方式中,所述存储电容在所述基底上的正投影与所述空白区在所述基底上的正投影没有交叠。

17、在示例性实施方式中,相邻单元列的像素驱动电路相对于中心线镜像对称,所述中心线是位于相邻单元列之间且沿着所述单元列方向延伸的直线。

18、在示例性实施方式中,所述驱动电路层至少包括沿着远离所述基底方向设置的第一半导体层、第一导电层、第二导电层、第二半导体层、第三导电层、第四导电层和第五导电层;所述第一半导体层至少包括多个多晶硅晶体管的有源层,所述第一导电层至少包括所述第一扫描信号线、第二扫描信号线、第一初始信号线和存储电容的第一极板,所述第二导电层至少包括存储电容的第二极板,所述第二半导体层至少包括多个氧化物晶体管的有源层,所述第三导电层至少包括所述第三扫描信号线、第四扫描信号线和第二初始信号线,所述第四导电层至少包括多个多晶硅晶体管的第一极和第二极、多个氧化物晶体管的第一极和第二极,所述第五导电层至少包括所述数据信号线。

19、在示例性实施方式中,所述显示基板还包括设置在所述发光结构层远离所述基底一侧的封装结构层和设置在所述封装结构层远离所述基底一侧的所述彩膜结构层,所述彩膜结构层至少包括黑矩阵和多个彩膜,所述黑矩阵设置在相邻的彩膜之间,所述透光开口在所述基底上的正投影位于所述彩膜在所述基底上的正投影的范围之内,所述黑矩阵设置有黑矩阵开口,所述透光开口在所述基底上的正投影位于所述黑矩阵开口在所述基底上的正投影的范围之内。

20、另一方面,本公开还提供了一种显示装置,包括前述的显示基板。

21、又一方面,本公开还提供了一种显示基板的制备方法,包括:

22、在基底上形成驱动电路层,所述驱动电路层包括构成多个单元行和多个单元列的多个电路单元,至少一个电路单元包括像素驱动电路;

23、在所述驱动电路层上形成发光结构层,所述发光结构层包括多个发光单元,至少一个发光单元包括设置在所述驱动电路层远离所述基底一侧的阳极和设置在所述阳极远离所述基底一侧的像素定义层所述阳极与对应电路单元的像素驱动电路连接,所述像素定义层设置有像素开口,所述像素开口暴露出所述阳极;至少一个发光单元的像素定义层设置有透光开口,所述透光开口在所述基底上的正投影面积为0.09s至0.15s,s为所述电路单元在基底上的正投影面积。

24、本公开示例性实施例公开了一种显示基板及其制备方法、显示装置,通过在像素定义层上设置透光开口,透光开口可以透过光线,提高了显示基板的透过率。

25、在阅读并理解了附图和详细描述后,可以明白其他方面。

- 还没有人留言评论。精彩留言会获得点赞!