用于动态功率降低的自门控触发器的制作方法

本公开总体上涉及诸如可编程逻辑器件(pld)的集成电路(ic)器件。更具体地,本公开涉及用于诸如现场可编程门阵列(fpga)的集成电路器件的动态功率降低的技术。

背景技术:

1、本部分旨在向读者介绍可能与以下描述和/或要求保护的本公开的各个方面相关的技术的各个方面。该讨论被认为有助于为读者提供背景信息以促进更好地理解本公开的各个方面。因此,可以理解的是,这些陈述要从这个角度来理解,而不是承认为现有技术。

2、集成电路器件存在于各种各样的产品中,包括计算机、手持设备、工业基础设施、电视和车辆。这些集成电路器件中的许多器件是为执行特定任务而设计和制造的专用集成电路(asic)。相比之下,可编程逻辑器件(例如,fpga)可以在制造后配置各种不同的系统设计。因此,可编程逻辑器件可以用于不同的任务和/或工作负载。然而,操作频率的增加和/或更高性能的计算可能导致可编程逻辑器件的更大动态功耗。

技术实现思路

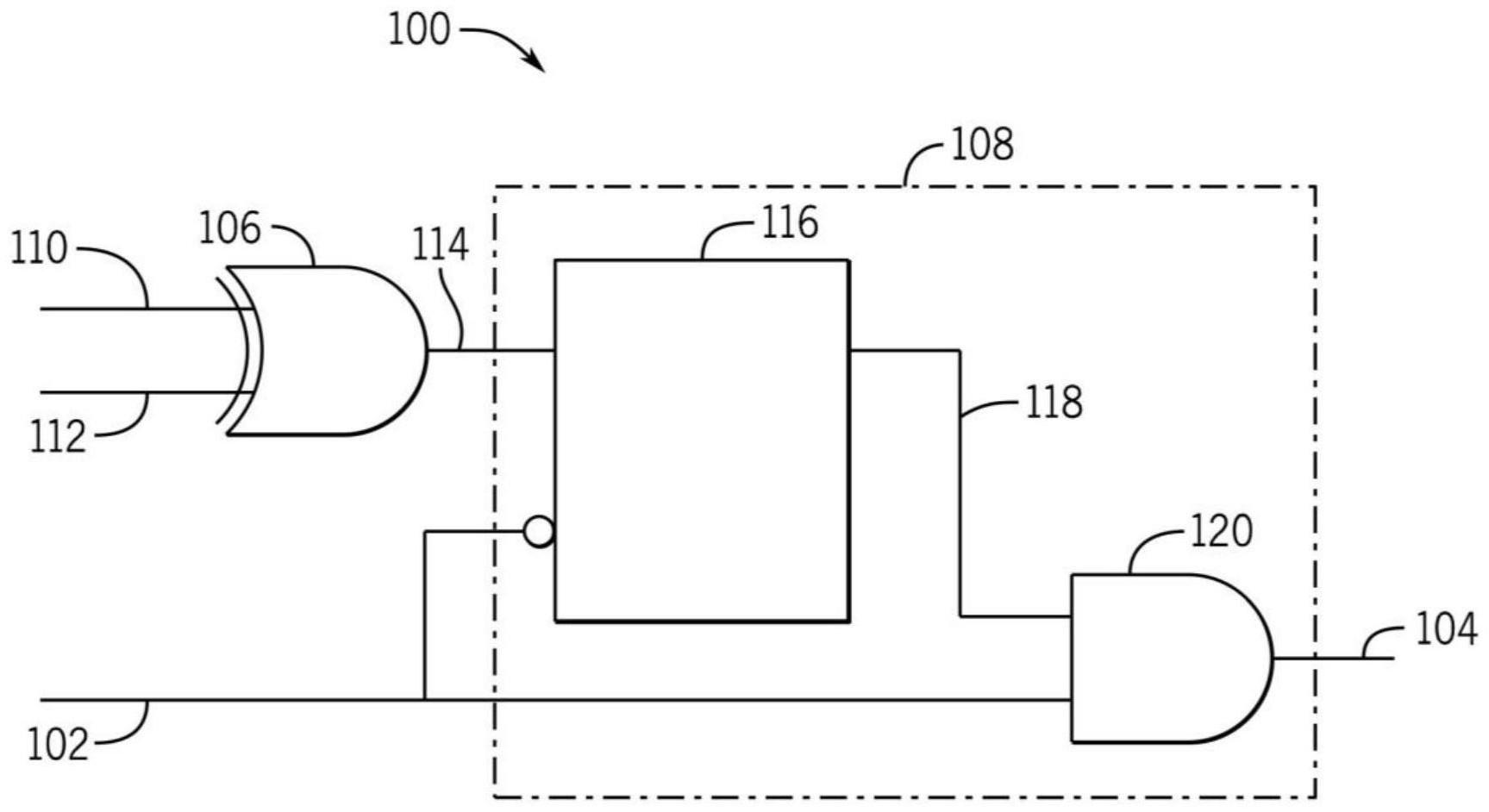

1、根据本公开的一个实施例,提供了一种具有时钟门控电路以生成门控时钟信号的可编程逻辑器件,所述可编程逻辑器件包括:时钟门控电路,所述时钟门控电路接收时钟信号,其中,所述时钟门控电路不依赖锁存器并且包括:门控信号电路,所述门控信号电路基于所述时钟信号和使能信号生成门控信号;逻辑门,所述逻辑门基于所述门控信号生成控制信号;以及门控时钟生成电路,所述门控时钟生成电路基于所述时钟信号和所述控制信号生成门控时钟信号。

2、根据本公开的一个实施例,提供了一种具有时钟门控电路以生成门控时钟信号的现场可编程门阵列(fpga),所述fpga包括:触发器,所述触发器基于输入信号和门控时钟信号生成输出信号;时钟门控电路,所述时钟门控电路接收时钟信号并对所述时钟信号进行门控以施加到所述触发器,其中,所述时钟门控电路包括:门控信号电路,所述门控信号电路基于所述时钟信号、所述输入信号和所述输出信号生成门控信号;逻辑门,所述逻辑门基于所述门控信号生成控制信号;以及门控时钟生成电路,所述门控时钟生成电路基于所述时钟信号和所述控制信号生成所述门控时钟信号。

3、根据本公开的一个实施例,提供了一种具有生成门控时钟信号的时钟门控电路的可编程逻辑电路,所述可编程逻辑电路包括:多个触发器,所述多个触发器生成多个输出信号并接收多个输入信号,其中,所述多个触发器中的触发器基于门控时钟信号和所述多个输入信号中的相应输入信号生成所述多个输出信号中的相应输出信号;时钟门控电路,所述时钟门控电路接收时钟信号,其中,所述时钟门控电路包括:多个门控信号电路,所述多个门控信号电路生成多个门控信号,其中,所述门控信号电路基于所述时钟信号、对应的输入信号和对应的输出信号生成所述多个门控信号中的对应门控信号;逻辑门,所述逻辑门基于所述多个门控信号生成控制信号;以及门控时钟生成电路,所述门控时钟生成电路基于所述时钟信号和所述控制信号生成所述门控时钟信号。

技术特征:

1.一种具有时钟门控电路以生成门控时钟信号的可编程逻辑器件,所述可编程逻辑器件包括:

2.根据权利要求1所述的可编程逻辑器件,其中,所述门控时钟生成电路包括多个晶体管。

3.根据权利要求2所述的可编程逻辑器件,其中,所述多个晶体管包括至少一个n沟道金属氧化物半导体(nmos)晶体管和至少一个p沟道金属氧化物半导体(pmos)晶体管。

4.根据权利要求3所述的可编程逻辑器件,其中,所述至少一个nmos晶体管的栅极端子和所述至少一个pmos晶体管的栅极端子耦合到所述时钟信号。

5.根据权利要求3所述的可编程逻辑器件,其中,所述至少一个nmos晶体管的栅极端子和所述至少一个pmos晶体管的栅极端子耦合到所述控制信号。

6.根据权利要求1所述的可编程逻辑器件,其中,所述门控信号电路包括n沟道金属氧化物半导体(nmos)晶体管、p沟道金属氧化物半导体(pmos)晶体管和反相器。

7.根据权利要求6所述的可编程逻辑器件,其中,所述反相器的输入耦合到所述时钟信号,并且所述nmos晶体管的栅极端子和所述pmos晶体管的栅极端子耦合到所述反相器的输出。

8.根据权利要求6所述的可编程逻辑器件,其中,所述nmos晶体管的栅极端子和所述pmos晶体管的栅极端子耦合到所述使能信号。

9.根据权利要求1至8中任一项所述的可编程逻辑器件,其中,所述逻辑门是反相器。

10.根据权利要求1至8中任一项所述的可编程逻辑器件,其中,所述可编程逻辑器件包括现场可编程门阵列(fpga)。

11.一种具有时钟门控电路以生成门控时钟信号的现场可编程门阵列(fpga),所述fpga包括:

12.根据权利要求11所述的fpga,其中,所述门控时钟生成电路包括n沟道金属氧化物半导体(nmos)晶体管和p沟道金属氧化物半导体(pmos)晶体管。

13.根据权利要求12所述的fpga,其中,所述nmos晶体管的栅极端子和所述pmos晶体管的栅极端子耦合到所述时钟信号。

14.根据权利要求12所述的fpga,其中,所述nmos晶体管的栅极端子和所述pmos晶体管的栅极端子耦合到所述控制信号。

15.根据权利要求11至14中任一项所述的fpga,其中,所述门控信号电路包括多个晶体管,所述多个晶体管包括至少一个n沟道金属氧化物半导体(nmos)晶体管和至少一个p沟道金属氧化物半导体(pmos)晶体管。

16.根据权利要求15所述的fpga,其中,所述至少一个nmos晶体管的栅极端子和所述至少一个pmos晶体管的栅极端子耦合到所述输入信号。

17.根据权利要求15所述的fpga,其中,所述至少一个nmos晶体管的栅极端子和所述至少一个pmos晶体管的栅极端子耦合到所述输出信号。

18.一种具有生成门控时钟信号的时钟门控电路的可编程逻辑电路,所述可编程逻辑电路包括:

19.根据权利要求18所述的可编程逻辑电路,其中,所述门控时钟生成电路是不依赖锁存器的。

20.根据权利要求18或19所述的可编程逻辑电路,其中,所述逻辑门是与非门。

技术总结

本公开涉及用于动态功率降低的自门控触发器。本文描述的系统或方法可以涉及一种用于启用或禁用集成电路器件的内部时钟的不依赖锁存器的时钟门控技术。一种可编程逻辑器件包括时钟门控电路,该时钟门控电路接收时钟信号并且是不依赖锁存器的。时钟门控电路包括门控信号电路,该门控信号电路基于时钟信号和使能信号生成门控信号。时钟门控电路还包括逻辑门,该逻辑门基于门控信号生成控制信号。时钟门控电路还包括门控时钟生成电路,该门控时钟生成电路基于时钟信号和控制信号生成门控时钟信号。

技术研发人员:马赫什·K·库马什卡尔,穆迪·阿尔塔夫·侯赛因,李越,阿图尔·马赫什瓦里,安克雷迪·纳拉马尔普

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!