一种正交六分频电路的制作方法

1.本发明属于射频通信芯片领域,特别涉及一种正交六分频电路。

背景技术:

2.目前常见的通信芯片常用的正交本振信号产生电路,大都为cmlflip-flop架构分频除2电路产生,或用两个vco设计成带正交iq-vco结构,直接产生iq信号输出。

3.如果所需的iq信号相对pll的vco的频率要低很多,一般会把vco的频率分频到所需的iq本振信号频率的2倍,再通过除2电路得到所需iq信号。iq正交信号为相位相差90度的i路和q路两路信号。最后送到混频器的iq信号为0度,90度,180度,270度4个相位的信号。i路为互为差分的0度和180度的信号,q路为互为差分的90度和270度的信号。

4.如专利号为201910653341.1,提出的一种满摆幅高速正交二分频电路,其通过加入nmos交叉耦合对,保证在高频输入信号下,输出信号最低点仍可以达到低电位,使输出电压摆幅达到电源电压,可以直接驱动后级电路。但是其存在着不便于分频操作的问题。

5.专利号为201520256451.1,提出的一种新型低成本分频电路,其实现了分频倍数可以为任何整数,不限制于现有的分频电路中仅为2的倍数的分频方式,而且仅仅通过改动拨码开关即可实现分频倍数的修改或设置,不需要做任何硬件电路的修改。其虽然可以进行分频倍数的修改,但是分频器功耗的较大,特别是频率很高时,功耗更大。进行iq除2分频时,要求输入的信号要严格差分,否则会有iq失配。因而要求所有分频链路上的分频器都为差分结构,对分频的要求较高。

技术实现要素:

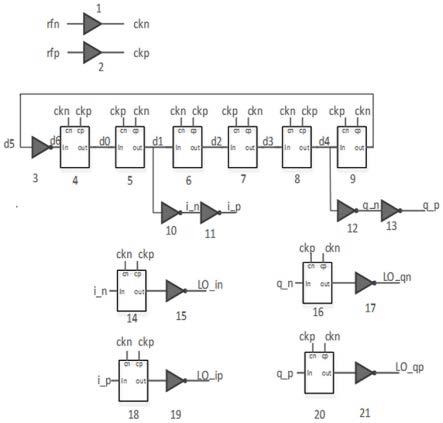

6.针对上述问题,本发明提供了一种正交六分频电路,包括:由两个反相器级联构成的用于输入rfn,rfp差分高频信号的输入缓冲驱动电路1和2,及与所述输入缓冲驱动电路1和2连接的分频电路,所述分频电路包括锁存电路4,5,6,7,8,9和反相器电路3,10,11,12,13;以及与所述分频电路相连接的输出采样电路,所述输出采样电路包括锁存电路14,16,18,20和由反相器15,17,19,21构成的输出驱动电路。所述输入缓冲驱动电路的输出信号分别为ckn,ckp,其中,所述ckn连接锁存电路4,6,8,14,18的cn以及锁存电路5,7,9,16,20的cp;所述ckp连接锁存电路4,6,8,14,18的cp以及锁存电路5,7,9,16,20的cn。

7.上述锁存电路4,5,6,7,8,9,14,16,18,20的电路相同,均包括2个pmos管p1,p2以及两个nmos管n1,n2;其中,所述pmos管p1的源极接电源vdd漏极p2的源极,栅极和n2管的栅极接一起接到in端;所述pmos管p2的栅极接端口cp,漏极和n1管的漏极接一起接到out端口;所述nmos管n1的栅极接cn端口,源极接n2管的漏极,n2管的源极接地。

8.上述锁存电路4的输出out通过连线d0接锁存电路5的in;锁存电路5的输出out通过连线d1接锁存电路6的in;锁存电路6的输出out通过连线d2接锁存电路7的in;锁存电路7的输出out通过连线d3接锁存电路8的in;锁存电路8的输出out通过连线d4接锁存电路9的in;锁存电路9的输出out通过连线d5接反相器3的输入;反相器3的输出通过连线d6接锁存

电路4的输入in。

9.上述反相器10的输入接连线d1,10的输出通过连线i_n接反相器11的输入,同时i_n接采样锁存电路14的输入in,采样锁存电路14的输出接反相器15的输入,反相器15的输出接连线lo_in,上述反相器11的输出通过连线i_p接采样锁存电路18的输入in,锁存电路18的输出接反相器19的输入,反相器19的输出接连线lo_ip。lo_in和lo_ip为分频电路的i路输出。

10.上述反相器12的输入接连线d4,反相器12的输出通过连线q_n接反相器13的输入,同时q_n接采样锁存电路16的输入in,锁存器16的输出接反相器17的输入,反相器17的输出接连线lo_qn。

11.上述反相器13的输出通过连线q_p接采样锁存电路20的输入in,锁存电路20的输出接反相器21的输入,反相器21的输出接连线lo_qp。

12.上述lo_qn和lo_qp为分频电路的q路输出。

13.本发明的有益效果是:1、本发明中提出的正交六分频电路,主要由输入缓冲驱动电路1和2、分频电路、输出采样电路构成,通过简单的单端级联锁存电路对高频信号进行分频,并通过采样技术得到相位失配较小的正交iq本振信号,电路结构简洁,电路的功耗得到有效的降低,高频重采技术保证了相位的匹配性能,有效降低了功耗,并且这个电路架构能工作到很高的频率;2、本发明通过单端级联循环锁存电路,实现了对高频信号的分频,比如:除2分频,只需要两个锁存电路级联,除4用4个锁存电路,除6用6个锁存电路,就可以得到相位相差90度的iq两路本振信号,再通过输入的高频信号对这两个iq信号进行重采样,就可以得到严格的相位差90度的iq本振信号输出给混频器。

附图说明

14.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

15.图1示出了本发明实施例一中的iq-除6分频器电路图;图2示出了本发明实施例的锁存电路图;图3示出了本发明实施例二中的iq-除4分频器电路图;图4示出了本发明实施例三中的iq-除2分频器电路图。

具体实施方式

16.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地说明,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

17.实施例一本发明实施例中提供了一种正交六分频电路,包括:由两个反相器级联构成的用

于输入rfn,rfp差分高频信号的输入缓冲驱动电路1和2,及与所述输入缓冲驱动电路1和2连接的分频电路。

18.正交六分频电路采用6个单端锁存电路和一个反相器首尾级联,通过输入的差分高频时钟,前后两个锁存器的时钟输入相反,形成移位锁存。这样对于6级锁存级联结构,6个时钟周期刚好形成180度得相移。而3个锁存就形成90度得相移.由于最后输出给混频器的信号需要0度,90度,180度,270度得严格相位差的信号,否则接收系统就会由于相位差而出现镜像抑制恶化。图1中得到的0度和90度的信号,我们先通过反相器得到接近180度和270度的信号。再通过重采样技术对这几个信号进行高频重采样,就可以得到相位严格相位差的信号。

19.所述分频电路包括锁存电路4,5,6,7,8,9和反相器电路3,10,11,12,13;以及与所述分频电路相连接的输出采样电路,所述输出采样电路包括锁存电路14,16,18,20和由反相器15,17,19,21构成的输出驱动电路。所述输入缓冲驱动电路的输出信号分别为ckn,ckp,其中,所述ckn连接锁存电路4,6,8,14,18的cn以及锁存电路5,7,9,16,20的cp;所述ckp连接锁存电路4,6,8,14,18的cp以及锁存电路5,7,9,16,20的cn。

20.上述锁存电路4,5,6,7,8,9,14,16,18,20的电路相同,均包括2个pmos管p1,p2以及两个nmos管n1,n2;其中,所述pmos管p1的源极接电源vdd漏极p2的源极,栅极和n2管的栅极接一起接到in端;所述pmos管p2的栅极接端口cp,漏极和n1管的漏极接一起接到out端口;所述nmos管n1的栅极接cn端口,源极接n2管的漏极,n2管的源极接地。

21.上述锁存电路4的输出out通过连线d0接锁存电路5的in;锁存电路5的输出out通过连线d1接锁存电路6的in;锁存电路6的输出out通过连线d2接锁存电路7的in;锁存电路7的输出out通过连线d3接锁存电路8的in;锁存电路8的输出out通过连线d4接锁存电路9的in;锁存电路9的输出out通过连线d5接反相器3的输入;反相器3的输出通过连线d6接锁存电路4的输入in。

22.上述反相器10的输入接连线d1,10的输出通过连线i_n接反相器11的输入,同时i_n接采样锁存电路14的输入in,采样锁存电路14的输出接反相器15的输入,反相器15的输出接连线lo_in,上述反相器11的输出通过连线i_p接采样锁存电路18的输入in,锁存电路18的输出接反相器19的输入,反相器19的输出接连线lo_ip。lo_in和lo_ip为分频电路的i路输出。

23.上述反相器12的输入接连线d4,反相器12的输出通过连线q_n接反相器13的输入,同时q_n接采样锁存电路16的输入in,锁存器16的输出接反相器17的输入,反相器17的输出接连线lo_qn。

24.上述反相器13的输出通过连线q_p接采样锁存电路20的输入in,锁存电路20的输出接反相器21的输入,反相器21的输出接连线lo_qp。上述lo_qn和lo_qp为分频电路的q路输出。

25.除6分频是用级联锁存实现,其rfp,rfn时钟变化对应的d0,d2,d2,d3,d4,d6的状态变化如下:

从上面的状态变化可以看出,每过六个时钟周期状态就会循环,从而实现除6功能。从d1和d4输出,刚好实现3个时钟周期的时间延时,也就实现了相位90度的相位差。由于除6电路是单端的,通过反相器10,11,12,13得到四个相位。由于反相器处在时间的延时,因而i_n和i_p以及q_n和q_p不是绝对的差分.因而图1电路通过采样锁存电路14,18以及16,20分别对i_n和i_p以及q_n和q_p进行重采样,从而得到相位严格对称的i路和q路信号。通过简单的单端级联锁存电路对高频信号进行分频,并通过采样技术得到相位失配较小的正交iq本振信号。电路结构简洁,电路的功耗得到有效的降低。高频重采技术保证了相位的匹配性能。

26.在本实施例中,提出的是iq分频除6电路。这个电路也可以实现除2,除4甚至除8

等 iq 分频电路。 只需要相应的改变锁存电路的级数就可以实现。下面将结合实施例来具体说明。

27.实施例二在本实施例中,提供一种iq分频除4电路,如图3所示的。除4分频电路采用4个锁存单元电路和一个反相器级联,再通过采样锁存电路14、16、18、20,采样得到正交输出信号。

28.具体如下:锁存电路4的输出out通过连线d0接锁存电路5的in;锁存电路5的输出out通过连线d1接锁存电路6的in;锁存电路6的输出out通过连线d2接锁存电路9的in;锁存电路9的输出out通过连线d5接反相器3的输入;反相器3的输出通过连线d6接锁存电路4的输入in。

29.反相器10的输入接连线d1,10的输出通过连线i_n接反相器11的输入,同时i_n接采样锁存电路14的输入in,采样锁存电路14的输出接反相器15的输入,反相器15的输出接连线lo_in,上述反相器11的输出通过连线i_p接采样锁存电路18的输入in,锁存电路18的输出接反相器19的输入,反相器19的输出接连线lo_ip。lo_in和lo_ip为分频电路的i路输出。

30.上述反相器12的输入接连线d2,反相器12的输出通过连线q_n接反相器13的输入,同时q_n接采样锁存电路16的输入in,锁存器16的输出接反相器17的输入,反相器17的输出接连线lo_qn。

31.上述反相器13的输出通过连线q_p接采样锁存电路20的输入in,锁存电路20的输出接反相器21的输入,反相器21的输出接连线lo_qp。上述lo_qn和lo_qp为分频电路的q路输出。

32.实施例三在本实施例中,提供一种iq分频除2电路,如图4所示的。除2采用2个锁存单元和一个反相器级联,再通过采样锁存电路14,16,18,20采样得到正交输出信号。

33.具体如下:锁存电路4的输出out通过连线d0接锁存电路5的in;锁存电路5的输出out通过连线d1接反相器3的输入;反相器3的输出通过连线d6接锁存电路4的输入in。

34.反相器10的输入接连线d0,10的输出通过连线i_n接反相器11的输入,同时i_n接采样锁存电路14的输入in,采样锁存电路14的输出接反相器15的输入,反相器15的输出接连线lo_in,上述反相器11的输出通过连线i_p接采样锁存电路18的输入in,锁存电路18的输出接反相器19的输入,反相器19的输出接连线lo_ip。lo_in和lo_ip为分频电路的i路输出。

35.上述反相器12的输入接连线d1,反相器12的输出通过连线q_n接反相器13的输入,同时q_n接采样锁存电路16的输入in,锁存器16的输出接反相器17的输入,反相器17的输出接连线lo_qn。

36.上述反相器13的输出通过连线q_p接采样锁存电路20的输入in,锁存电路20的输出接反相器21的输入,反相器21的输出接连线lo_qp。上述lo_qn和lo_qp为分频电路的q路输出。

37.由上述实施例中可知,本技术中提出的正交六分频电路,主要由输入缓冲驱动电路1和2、分频电路、输出采样电路构成,通过简单的单端级联锁存电路对高频信号进行分

频,并通过采样技术得到相位失配较小的正交iq本振信号,电路结构简洁,电路的功耗得到有效的降低,高频重采技术保证了相位的匹配性能,有效降低了功耗,并且这个电路架构能工作到很高的频率。通过单端级联循环锁存电路,实现了对高频信号的分频,比如:除2分频,只需要两个锁存电路级联,除4用4个锁存电路,除6用6个锁存电路,就可以得到相位相差90度的iq两路本振信号,再通过输入的高频信号对这两个iq信号进行重采样,就可以得到严格的相位差90度的iq本振信号输出给混频器。

38.尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1