一种电平转换电路的制作方法

1.本实用新型涉及电路技术领域,尤其涉及一种电平转换电路。

背景技术:

2.在电子电路设计中,随着低电压逻辑的引入,系统内部常常出现输入/输出逻辑不协调的问题,从而提高了系统设计的复杂性。例如,当1.8v的数字电路与工作在3.3v的模拟电路进行通信时,需要首先解决两种电平的转换问题,这时就需要电平转换电路。

3.在现有技术中,随着不同工作电压的ic不断涌现,逻辑电平转换的必要性更加突出,电平转换方式也将随逻辑电压、数据总线的形式,例如4线spi、32位并行数据总线等,以及数据传输速率的不同而改变。现在虽然许多逻辑芯片都能实现较高的逻辑电平至较低逻辑电平的转换,如将5v电平转换至3v电平,但这些产品不是针对数据速率低于20mbps的串行总线,如spitm、i2ctm、usb等,这些器件具有较大的封装尺寸、较多的引脚数和i/o方向控制引脚,因而不适合小型串行或外设接口和更高速率的总线。

4.因此,如何更好的进行电平转换,是本领域技术人员迫切需要解决的一个技术问题。

技术实现要素:

5.本实用新型的目的在于提出一种电平转换电路,以解决现有技术的问题。

6.为实现上述目的,本申请第一方面提供了一种电平转换电路,所述电平转换电路包括:

7.第一信号端、第二信号端、第一输入端、第二输入端、第一输出端、第二输出端,第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、第六电阻、第一电容、第二电容、第一三极管、第二三极管;

8.所述第一信号端通过第三电阻与所述第一三极管的第三端连接;

9.所述第一三极管的第一端与所述第一电阻、第一电容连接;

10.所述第一三极管的第二端与所述第二电阻、第一输出端连接;

11.所述第一输入端与所述第一电阻、第一电容、第二电阻连接;

12.所述第一输出端与所述第二电阻连接;

13.所述第二信号端与所述第四电阻、第二三极管的第二端连接;

14.所述第二三极管的第一端与所述第二电容、第五电阻连接;

15.所述第二三极管的第三端与所述第六电阻连接;

16.所述第一输入端与所述第二电容、第五电阻连接;

17.所述第二输入端与所述第四电阻连接;

18.所述第二输出端与所述第六电阻连接。

19.具体的,可以实现包括如下的技术效果:

20.本申请通过接入一个持续的电平信号,将持续电平信号转换成一个需要的高低电

平信号,并可以通过调整参数来调整至合适的脉宽,供mcu等后续电路使用,适用于波特率低于460 kbps的应用场合,能够实现不同电平之间的转换,通过设定的参考电压,可以精准的进行电平转换,同时三极管能快速导通,响应速度可调。

附图说明

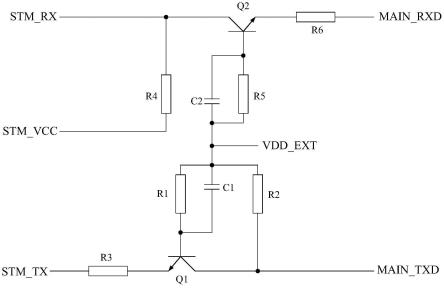

21.图1为本实用新型实施例中提供的一种电平转换电路的结构示意图。

具体实施方式

22.以下实施例用于说明本实用新型,但不用来限制本实用新型的范围。

实施例

23.本申请提供的电平转换电路,如图1所示,本申请所述的电平转换电路,包括:

24.第一信号端stm_tx、第二信号端stm_rx、第一输入端vdd_ext、第二输入端stm_vcc、第一输出端main_rxd、第二输出端main_txd,第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、第六电阻r6、第一电容c1、第二电容c2、第一三极管q1、第二三极管q2;

25.所述第一信号端stm_tx通过第三电阻r3与所述第一三极管q1的第三端连接;

26.所述第一三极管q1的第一端与所述第一电阻r1、第一电容c1连接;

27.所述第一三极管q1的第二端与所述第二电阻r2、第一输出端vdd_ext连接;

28.所述第一输入端vdd_ext与所述第一电阻r1、第一电容c1、第二电阻r2连接;

29.所述第一输出端main_rxd与所述第二电阻r2连接;

30.所述第二信号端stm_rx与所述第四电阻r4、第二三极管q2的第二端连接;

31.所述第二三极管q2的第一端与所述第二电容c2、第五电阻r5连接;

32.所述第二三极管q2的第三端与所述第六电阻r6连接;

33.所述第一输入端vdd_ext与所述第二电容c2、第五电阻r5连接;

34.所述第二输入端stm_vcc与所述第四电阻r4连接;

35.所述第二输出端main_txd与所述第六电阻r6连接。

36.在具体执行时,通过所述第一输入端vdd_ext接入需要的低电平后,利用所述第一信号端stm_tx输入,由于第一三极管q1、第二三极管q2的导通特性,通过设计和计算所述第一电容c1、第二电容c2充电时间则可以得到触发条件,从而执行相应的动作。

37.当输入所述第一信号端stm_tx为较高电平值时,通过电平转换电路,设置所述第一输入端vdd_ext处的电压,所述第二信号端stm_rx得到所需要的电平值。减小所述第一电阻r1与第三电阻r3可以降低上下降沿的延迟,能实现该电路的快速响应,同时也能限流。

38.当所述第一信号端stm_tx为高时,所述第一三极管q1截止,所述第二信号端stm_rx被拉高,随所述第一输入端vdd_ext、第二输入端stm_vcc的电平变化。

39.当所述第一信号端stm_tx为低时,所述第一三极管q1导通,所述第二信号端stm_rx被拉低,随所述第一信号端stm_tx的电平变化。

40.在本说明书的描述中,参考术语“在一实施例中”、“在又一实施例中”、“示例性的”或“在具体的实施例中”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或

者特点包含于本实用新型的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

41.虽然,上文中已经用一般性说明、具体实施方式及试验,对本实用新型作了详尽的描述,但在本实用新型基础上,可以对之作一些修改或改进,这对本领域技术人员而言是显而易见的。因此,在不偏离本实用新型精神的基础上所做的这些修改或改进,均属于本实用新型要求保护的范围。

技术特征:

1.一种电平转换电路,其特征在于,包括:第一信号端、第二信号端、第一输入端、第二输入端、第一输出端、第二输出端,第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、第六电阻、第一电容、第二电容、第一三极管、第二三极管;所述第一信号端通过第三电阻与所述第一三极管的第三端连接;所述第一三极管的第一端与所述第一电阻、第一电容连接;所述第一三极管的第二端与所述第二电阻、第一输出端连接;所述第一输入端与所述第一电阻、第一电容、第二电阻连接;所述第一输出端与所述第二电阻连接;所述第二信号端与所述第四电阻、第二三极管的第二端连接;所述第二三极管的第一端与所述第二电容、第五电阻连接;所述第二三极管的第三端与所述第六电阻连接;所述第一输入端与所述第二电容、第五电阻连接;所述第二输入端与所述第四电阻连接;所述第二输出端与所述第六电阻连接。

技术总结

本实用新型涉及一种电平转换电路,所述电路包括:第一信号端、第二信号端、第一输入端、第二输入端、第一输出端、第二输出端,第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、第六电阻、第一电容、第二电容、第一三极管、第二三极管。本申请将持续电平信号转换成一个需要的高低电平信号,并可以通过调整参数来调整至合适的脉宽,供MCU等后续电路使用,适用于波特率低于460 kbps的应用场合,能够实现不同电平之间的转换,通过设定的参考电压,可以精准的进行电平转换,同时三极管能快速导通,响应速度可调。度可调。度可调。

技术研发人员:郭易宙 吴伟 金明珠 冯昆 叶国华 陈志军 刘聪

受保护的技术使用者:广东博力威科技股份有限公司

技术研发日:2022.03.21

技术公布日:2022/10/11

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1