一种多级电压IO单元及其芯片的制作方法

一种多级电压io单元及其芯片

技术领域

1.本实用新型属于集成电路设计领域,尤其涉及一种多级电压io单元及其芯片。

背景技术:

2.数字逻辑芯片和mcu芯片一般使用foundry厂家(专门生产制造芯片厂家)或第三方ip厂商提供的通用io单元实现多个io引脚,用于高电平或低电平的数字信号输入或输出,这种io引脚的输入状态只有0(低电平)或1(高电平),输出状态也只有0(低电平)或1(高电平)以及三态输出禁止。现有的通用io单元如图1所示。

3.使用该通用io单元存在以下缺陷:一方面,这种通用io不太适用于多电压多电平的多芯互连的复杂系统。常规解决方法是外加电平转换芯片,导致成本增加,例如将自身的3.3v数字信号通过外置芯片转换成1.8v后再连接目标设备,或反之。另一方面,这种通用io也不太适用于数模混合芯片及系统,有些外设需要向其提供多种上拉或者下拉电流,有些外设需要mcu向其动态提供多种参考电压,或者感知外设产生的多种信号电压。常规解决方法需要多个电阻、dac、比较器等,所需元器件较多,成本高,面积较大,不利于io布局。所以,该方案一直未被数模混合型mcu采用,也一直未在io单元库中实现。

4.中国专利cn201910163902.x公开了复用芯片内的可编程dac实现可编程上拉电阻或可编程下拉电阻的功能,但是未能在io单元的多级电平输入输出上有所扩展。

技术实现要素:

5.发明目的:为了解决现有技术中,芯片支持多级电压输入输出而导致电路复杂、元器件多、成本高、不利于商用等问题,本实用新型提供一种多级电压io单元及其芯片。

6.技术方案:一种多级电压io单元,包括:

7.io引脚;

8.可编程dac,输入端输入控制信号及数据信号,输出端连接运放正输入端;

9.第一模拟开关,第一端连接可编程dac输出端,第二端连接io引脚;

10.运放,输出端引出数据信号线,负输入端连接esd保护电路的输出端,esd保护电路的输入端连接io引脚;

11.第二模拟开关,第一端连接运放输出端,第二端连接io引脚。

12.进一步地,所述可编程dac的输入端包括一组数据信号线及至少两根模式控制线,数据信号线输入数据信号,模式控制线输入控制信号。

13.进一步地,所述运放为轨到轨放大器。

14.进一步地,还包括电阻,所述电阻的一端连接第一模拟开关的第二端,电阻的另一端连接io引脚。

15.进一步地,第二模拟开关的第二端连接第一模拟开关的第二端。

16.进一步地,还包括模拟信号比较结果数字化模块,所述模拟信号比较结果数字化模块的输入端连接运放输出端,另一端引出数据信号线。

17.进一步地,所述第二模拟开关嵌入到运放中,第二模拟开关包括第一pmos管和第一nmos管,运放输出端包括第二pmos管和第二nmos管,第一pmos管串联在第二pmos管的漏端或源端,第一nmos管串联在第二nmos管的漏端或源端,第一pmos管及第一nmos管的栅端连接运放的三态输出控制端。

18.进一步地,所述第二模拟开关嵌入到运放中,第二模拟开关包括第三pmos管、第三nmos管、第一组合开关及第二组合开关;运放输出端包括第二pmos管和第二nmos管;第一组合开关及第二组合开关分别连接在第二pmos管和第二nmos管的栅端;所述第三pmos管源端接电源,漏端接第二pmos管栅端;所述第三nmos管源端接地,漏端接第二nmos管栅端。

19.进一步地,还包括数字电平输入模块、输出模块中的至少一个;所述数字电平输入模块的输入端连接esd保护电路的输出端,数字电平输入模块的输出端引出数据信号线;所述输出模块包括输出端、第一输入端及第二输入端,输出端连接io引脚,第一输入端连接使能输出控制端,第二输入端连接数据信号。

20.一种含多级电压io单元的芯片,包括上述多级电压io单元及模式控制单元,所述模式控制单元的输出端连接可编程dac的输入端、第一模拟开关的控制端及第二模拟开关的控制端。

21.本实用新型提供一种多级电压io单元及其芯片,相比较现有技术,存在以下有益效果:

22.(1)结构简单,仅增加一个运放和两个模拟开关,通过一定的连接关系,通过模式组合设计,实现多级电压比较输入和多级电压缓冲输出的功能。

23.(2)采用可编程dac,复用dac自身的电阻,结合两个模拟开关的控制,通过逻辑组合实现多级电平输入输出的多种模式。

24.(3)复用了在芯片中难以随工艺提升而减小面积的模拟器件,例如复用了在芯片中成本较高、占面积较大的电阻和运放;增加了在芯片中容易随工艺提升而减小面积的数字器件,例如增加了模式组合控制。在实现多级电压输入输出的效果下,尽可能减小芯片增加的面积,降低芯片增加的成本。

25.(4)支持多级电压输入和输出,无需增加电平转换芯片。可以为模拟型芯片和数模混合型mcu提供多级电压io单元,适用于数模混合芯片及系统,提升了芯片的性能。

附图说明

26.图1为现有io单元的结构示意图;

27.图2为实施例一多级电压io单元的结构示意图;

28.图3为实施例二嵌入第二模拟开关后的运放结构示意图;

29.图4为实施例三嵌入第二模拟开关后的运放结构示意图;

30.图5为实施例四多级电压io单元的结构示意图;

31.图6为实施例五多级电压io单元的结构示意图。

具体实施方式

32.下面结合附图和具体实施例对本发明做进一步解释说明。

33.实施例一:

34.一种多级电压io单元,如图2所示,包括io引脚pad、可编程dac、第一模拟开关k1、第二模拟开关k2、运放及esd保护电路。可编程dac的输入端输入控制信号及数据信号,输出端连接运放正输入端。第一模拟开关的第一端连接可编程dac输出端,第二端连接io引脚。运放的输出端引出数据信号线c0,负输入端连接esd保护电路的输出端,esd保护电路的输入端连接io引脚,该esd保护电路为二级esd保护,一般由数百欧的电阻加ggnmos或grnmos构成,此外io引脚pad上还连接有一级esd保护。第二模拟开关的第一端连接运放输出端。

35.所述可编程dac的输入端包括一组数据信号线data及至少两根模式控制线pue、pde,数据信号线输入数据信号,模式控制线输入控制信号,用于控制进入何种模式。

36.所述运放为轨到轨放大器,运放的输入和输出均支持轨到轨,该轨到轨运放支持0到电源电压全范围的输入和输出。

37.还可以包括电阻r,所述电阻r的一端连接第一模拟开关的第二端,电阻r的另一端连接io引脚。所述电阻的阻值一般为数十欧到数百欧,第一模拟开关的mos器件兼做esd器件,与电阻r一起兼做运放正输入端的二级esd保护。如果r阻值较小,第二模拟开关的第二端也可以与第一模拟开关第二端连接,但通常是直接连接至io引脚。电阻r是可选的,如果运放正输入端已有一定的esd承受能力,那么电阻r也可以用短接代替。

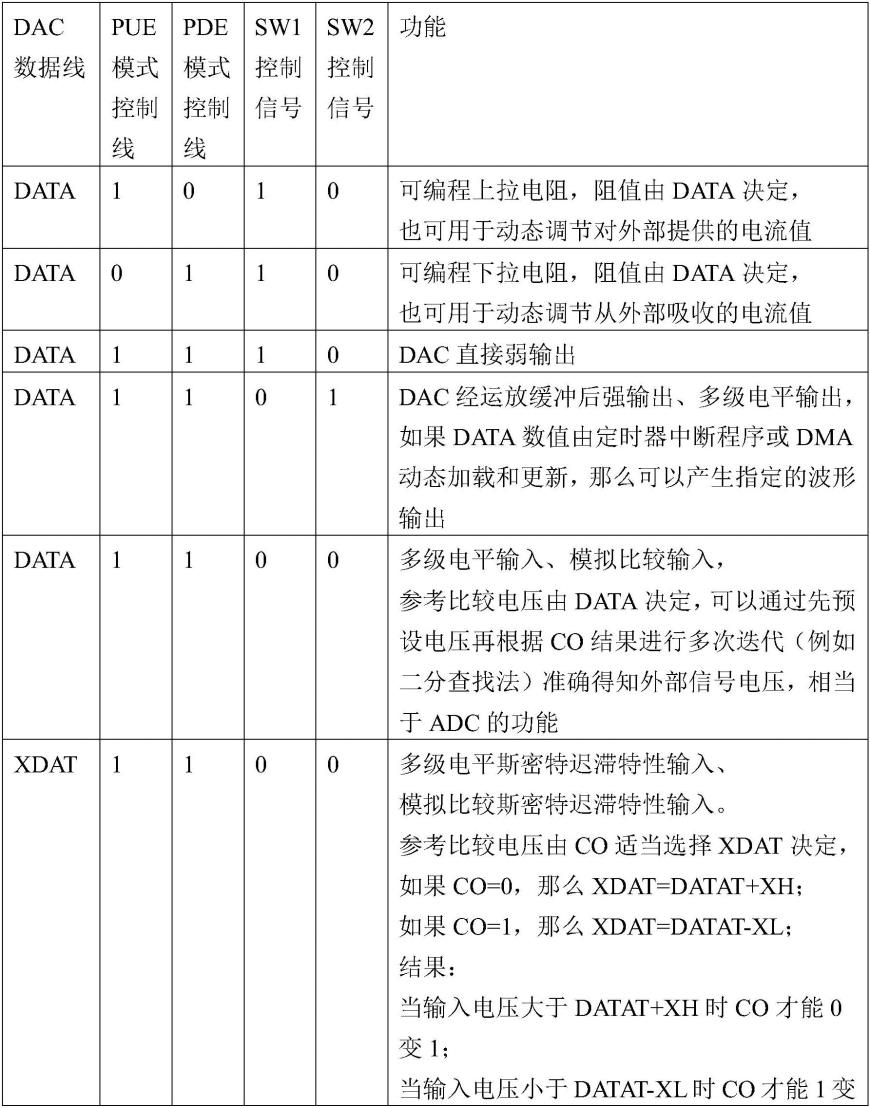

38.一种含多级电压io单元的芯片,尤其是数模混合型mcu,包括上述的多级电压io单元及模式控制单元,所述模式控制单元的输出端连接可编程dac的输入端、第一模拟开关k1及第二模拟开关k2的控制端。模式控制单元通过组合逻辑输出多种模式控制信号,通过控制可编程dac、第一模拟开关及第二模拟开关实现多种工作模式,包括dac直接输出模式、dac缓冲输出模式、可编程上拉电阻模式、可编程下拉电阻模式及多级电平输入模式。表1举例示意了多种工作模式表对应的一系列组合逻辑,但不限于这一种组合。对于在芯片中难以随工艺提升而降低面积的模拟器件,例如电阻和运放,通过模式组合实现了充分的复用,以较少的器件和有效的连接关系,实现多种功能。

39.表1多种工作模式表

[0040][0041][0042]

实施例二:

[0043]

实施例二与实施例一的区别在于,实施例二的第二模拟开关嵌入在运放中。如图3所示,第二模拟开关k2包括第一pmos管p1和第一nmos管n1,运放输出端包括第二pmos管p2和第二nmos管n2,第一pmos管p1串联在第二pmos管p2的漏端或源端,第一nmos管n1串联在

第二nmos管n2的漏端或源端,第一pmos管p1及第一nmos管n1的栅端连接运放的三态输出控制端,所述三态输出控制端原用于运放三态输出启用或禁止,现可通过三态输出控制端的启用或禁止信号,实现控制第二模拟开关开启或关闭的效果。为了直观显示第二模拟开关嵌入在运放中的连接关系。图3示出了一种简化的运放结构,实际使用的运放很可能比这种要复杂得多。另外,技术上稍做微调,上述p1和p2也可以交换位置,上述n1和n2可以交换位置,效果相同。如图为当三态输出控制端为开启信号时,等效为第二模拟开关开启,当三态输出控制端为禁止信号时,等效为第二模拟开关关闭。

[0044]

实施例三:

[0045]

实施例三的第二模拟开关也是嵌入在运放中的,与实施例二相比,区别在于,第二模拟开关的结构不同,与运放的连接关系不同。如图4所示,是实施例三将第二模拟开关嵌入在运放中的方式。第二模拟开关包括第三pmos管p3、第三nmos管n3及两个组合开关k3;运放输出端包括第二pmos管p2和第二nmos管n2;第一组合开关及第二组合开关分别连接在第二pmos管p2和第二nmos管n2的栅端;所述第三pmos管p3源端接电源,漏端接第二pmos管p2栅端;所述第三nmos管n3源端接地,漏端接第二nmos管n2栅端。第一组合开关、第二组合开关均为一对pmos管和nmos管构成的组合开关。运放输出端的第二pmos管p2栅端由第三pmos管p3和第一组合开关控制,第二nmos管n2栅端由第三nmos管n3和第二组合开关控制。开关控制信号如图中swon、swinv所示。当两个组合开关导通时,等效为第二模拟开关打开,运放输出直接连接io引脚,当第三pmos管p3、第三nmos管n3导通时,等效为第二模拟开关断开。

[0046]

这种方式虽然需要更多器件,但所加mos器件所通过的电流小,故器件尺寸较小。

[0047]

对于嵌入第二模拟开关后的运放,co可以由运放的另一不含三态控制的镜像输出端产生,或者从多级运放的前一级引出。

[0048]

实施例四:

[0049]

实施例四与实施例一相比,增加了模拟信号比较结果数字化模块,其输入端连接运放的输出端,另一端引出数据信号线,如图5所示。所述模拟信号比较结果数字化模块可以由若干级反相器实现,或者由level shift模块实现。运放将正负输入端电压进行比较,运放输出端的信号产生比较结果,要么低电平要么高电平,理论上可以直接作为数字信号使用,但为了更好的数字电平匹配效果,例如运放工作于3.3v,而数字内核或模式控制单元希望信号电平1.2v,那么可以加上模拟信号比较结果数字化模块,以实现更好的数字化匹配效果。

[0050]

实施例五:

[0051]

实施例五在实施例一或实施例二或实施例三或实施例四的基础上,增加了数字电平输入模块和输出模块,也可以单独只增加其一。

[0052]

如图6所示,所述数字电平输入模块的输入端连接二级esd保护电路的输出端,数字电平输入模块的输出端引出数据信号线,实现单一数字电平输入,用于兼容现有通用io单元。

[0053]

所述输出模块包括输出端、第一输入端及第二输入端,输出端连接io引脚,第一输入端连接使能输出控制端(选择是否使用单一数字电平输出),第二输入端连接输出数据信号,实现单一数字电平输出,用于兼容现有通用io单元。

[0054]

实施例四可与现有通用io单元的功能兼容,实现更高速的单一数字电平输入和输

出,其输出模块的mos器件还可以兼做一级esd保护器件。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1