一种精简型多通道准同步音频采集电路

1.本实用新型一种精简型多通道准同步音频采集电路属于电子测量技术领域。

背景技术:

2.精简型多通道准同步音频采集电路在仪器与测量领域有广泛应用。目前随着计算机和微电子技术行业的快速发展,例如雷达、通信等的众多电子测量领域对于数据采集有了更高的要求,数据采集正在向着多通道、高采样率、高分辨率和高传输速度方向快速发展,在工业实践和教育教学等环境下有了更广泛的应用。

3.目前的声纳震动等精简型多通道准同步音频采集电路的主要任务就是如何在现有的技术条件下尽可能用较为精简的电路拓展更多的采集通道,实现更多采集通道的扩展;声纳等音频震动信号的需要进行多点实时的监测,且精度不需要太高。现阶段的音频采集电路如ti公司单通道音频采集的tida-01471,和ni公司的多通道pci-6115,4路模拟输入,2路模拟输出,8路数字i/o线,同步采集设备最低售价已达四万块,ni-pxi-6289,32路模拟输入,48路数字i/o,4路模拟输出,售价最低为2.4万。

4.目前市场上存在的多通道数据采集电路通常是电路较为复杂;价格过高;前端模拟电路在处理交流信号时需要提供双电源,增加了成本和电路的功耗,电路不够精简。

技术实现要素:

5.针对上述问题,本实用新型设计了一种精简型多通道准同步音频采集电路,该电路使用5v电源供电,可用电脑或者充电宝进行供电,便于携带;模拟信号前端使用单电源供电,简化了电路结构,降低了电路成本与功耗;使用模数集成型新型芯片stm32g474自带12bit的4路adc进行同步采集,每路adc采用8个通道扫描采样,实现32个通道的数据采集;使用数据选择器,选出通道的模拟输出与模数集成型新型芯片stm32g474内部生成的dac参考进行比较,当达到某一临界值时进行触发,将adc转换的信号进行传输;使用过采样技术提高adc采集信号的信噪比;同时可通过软件插值算法,实现多通道准同步传输。

6.本实用新型的目的是这样实现的:

7.一种精简型多通道准同步音频采集电路,由多通道模拟信号前端单元、stm32g474最小系统单元、数据选择单元、静态存储单元、参考电压基准单元、usb通信供电单元和电压转换单元构成;

8.所述多通道模拟信号前端单元由32个相同的单元构成,每个单元由一个低噪声运算放大器、一个电容、五个电阻和一个两输入端子构成;低噪声运算放大器的反向输入端通过一个电阻ra2连接到低噪声运算放大器的输出端;低噪声运算放大器的同相输入端通过电阻ra5与电阻ra3连接到vcom端,同时,通过电阻ra5与电阻ra6连接到两输入端子ina的引脚1,两输入端子ina的引脚2连接到公共的vcom端;低噪声运算放大器的输出端通过电阻ra4与电容ca1直接耦合到gnd,同时,通过电阻ra4连接八选一数据选择引脚,输出采集到的模拟信号;同时,通过电阻ra4连接单片机stm32g474qet6的u1a,进行模数转换;低噪声运算

放大器的正电源引脚连接到vcc,低噪声运算放大器的负电源引脚连接到gnd;

9.所述stm32g474最小系统单元由128引脚的单片机stm32g474qet6、晶振、电阻、电容和发光二极管组成;所述单片机stm32g474qet6包括u1a、u1b和u1c三部分;u1a的引脚27、28、32、22、23、24、25和39分别与连接到多通道模拟信号前端单元输出的adc1_in1、adc1_in3、adc1_in4、adc1_in6、adc1_in7、adc1_in8、adc1_in9和adc1_in15,配置为adc1的8个输入通道;u1a的引脚28、35、36、37、38、41、34和69分别与连接到多通道模拟信号前端单元输出的adc2_in2、adc2_in3、adc2_in4、adc2_in5、adc2_in11、adc2_in12、adc2_in13和adc2_in14,配置为adc2的8个输入通道;u1b的引脚60、61、56、54和u1a的引脚66、68、69、71分别与连接到多通道模拟信号前端单元输出的adc4_in1、adc4_in2、adc4_in6、adc4_in14、adc4_in3、adc4_in4、adc4_in5和adc4_in13,配置为adc4的8个输入通道;u1a的引脚89、90、72、73、74、76、70和u1b的引脚58分别与连接到多通道模拟信号前端单元输出的adc5_in1、adc5_in2、adc5_in7、adc5_in8、adc5_in9、adc5_in11、adc5_in12和adc5_in16,配置为adc5的8个输入通道;一共配置4个adc,32路adc输入;

10.u1a的引脚40、39、67和65分别连接到数据选择单元的输出comp1_inp、comp4_inp、comp6_inp和comp5_inp,分别作为单片机stm32g474qet6内部配置四个比较器的同相输入端;比较器反相输入端分别由单片机stm32g474qet6内部的四个dac提供,实现内部触发设置;

11.u1b的引脚15、16、17、18、57和97分别连接静态存储单元u2芯片的引脚3、5、2、6、1和7,作为qspi1的传输引脚连接配置;u1a的引脚113、114、115、116和117分别连接静态存储单元u3芯片的引脚5、1、2、3和7,作为qspi2的传输引脚连接配置;u1a的引脚33通过发光二极管d1与电阻r4串联后连接到3v3电源,起到电源指示作用;u1a的引脚123通过电阻r2连接到gnd,用于boot0启动;u1b的引脚21通过电阻r1连接到gnd,用于复位;u1b的引脚19通过电阻r3连接到引脚20;晶振x1的引脚1连接到u1b引脚19,同时,晶振x1的引脚1通过电阻c1直接耦合到晶振x1的引脚2;晶振x1的引脚3连接到u1b引脚20,同时,晶振x1的引脚3通过电阻c2直接耦合到晶振x1的引脚4,晶振x1引脚4直接连接到gnd;u1c的引脚13、31、47、64、79、95、111、128、45、6、43和44连接到+3v3;u1c的引脚12、30、46、63、78、94、110和127连接到gnd;

12.所述数据选择单元由4个相同的单元构成,每个单元包括一个八选一模拟开关74hc4051,八选一模拟开关74hc4051的引脚13、14、15、12、1、5、2和4分别连接到八路模拟信号前端单元输出的adc1_in1、adc1_in3、adc1_in4、adc1_in6、adc1_in7、adc1_in8、adc1_in9和adc1_in10;八选一模拟开关74hc4051的引脚96、98和99分别连接到stm32g474芯片的引脚91、92和93,做通道选择控制;八选一模拟开关74hc4051的引脚3作为输出选出引脚,连接到stm32g474芯片的引脚14,作为单片机内部比较器的同相输出引脚;八选一模拟开关74hc4051的引脚16直接连接到vcc;八选一模拟开关74hc4051的引脚6、7和8直接连接到gnd;

13.所述静态存储单元由两片静态随机存储器u2和u3构成;u2的引脚1、2、3、5、7和6分别连接到u1b的引脚57、17、15、16、97和18,作为qspi1的四条数据线、一条时钟线和一条片选线;u2的引脚4直接连接到gnd;u2的引脚8直接连接到电源端3v3;

14.u3的引脚1、2、3、5、7和6分别连接到u1a的引脚113、115、116、114、117和u1b的引脚

18,作为qspi2的四条数据线、一条时钟线和一条片选线;u3的引脚4直接连接到gnd;u3的引脚8直接连接到电源端3v3;

15.所述参考电压基准单元由低噪声运算放大器和电阻组成;所述低噪声运算放大器的同相输入引脚3通过电阻ra8直接连接到vcc,同时通过电阻ra9直接连接到gnd;低噪声运算放大器的反相输入引脚2通过电阻ra7直接连接到运算放大器的输出引脚1,同时输出引脚作为电压输出vcom;输出参考电压基准的值为vcc/2,提供给输入端子的公共端vcom:

16.所述usb通信供电单元由一个双层usb接口jusb1组成;jusb1的引脚1与引脚5直接连接到vcc电源端;jusb1的引脚6直接连接到u1a的引脚92,jusb1的引脚7直接连接到u1a的引脚93,配置为通信引脚;jusb1的引脚4、引脚8和引脚9直接连接到gnd;

17.所述电压转换单元由线性稳压芯片1117-3v3和多个电容组成;线性稳压芯片1117-3v3的引脚3连接vcc,同时,通过滤波电容e1耦合到gnd;引脚1直接连接gnd;线性稳压芯片1117-3v3引脚2和引脚4作为输出引脚,直接输出3.3v电压,同时,通过滤波电容e2耦合到gnd;电压转换单元转换来自vcc的5v电压,输出3.3v电压给单片机进行供电。

18.有益效果:

19.第一、本实用新型一种精简型多通道准同步音频采集电路,使用单电源的模拟前端进行信号调理,节约了电路实现成本,减小了功耗,同时扩展了采样通道。

20.第二、本实用新型一种精简型多通道准同步音频采集电路,采用4路adc同步采集,每路adc使用8通道扫描模式,组合实现多达32通道adc数据采集的扩展。

21.第三、本实用新型一种精简型多通道准同步音频采集电路,采用过采样技术,可将信号的信噪比提高到16bit。

22.第四、本实用新型一种精简型多通道准同步音频采集电路,使用一片数字处理芯片g474,实现同步采样,过采样,与数据传输功能,无需多余的外围电路,电路的集成度更高,方案实现更简化。

23.第五、使用软件插值算法,增加采样点数,实现多通道的准同步采集。

附图说明

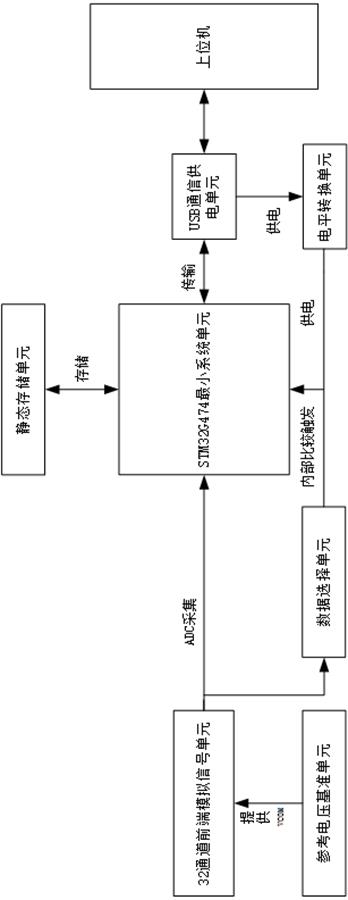

24.图1本实用新型一种精简型多通道准同步音频采集电路的整体模块示意图。

25.图2多通道模拟信号前端单元的电路图。

26.图3 stm32g474最小系统单元的电路图。

27.图4数据选择单元的电路图。

28.图5静态存储单元的电路图。

29.图6参考电压基准单元的电路图。

30.图7 usb通信供电单元的电路图。

31.图8电压转换单元的电路图。

具体实施方式

32.下面结合附图对本实用新型具体实施方式作进一步详细描述。

33.该具体实施方式下的一种精简型多通道准同步音频采集电路,整体模块示意图如图1所示,由多通道模拟信号前端单元、stm32g474最小系统单元、数据选择单元、静态存储

单元、参考电压基准单元、usb通信供电单元和电压转换单元构成;

34.如图2所示,所述多通道模拟信号前端单元由32个相同的单元构成,每个单元由一个低噪声运算放大器、一个电容、五个电阻和一个两输入端子构成;低噪声运算放大器的反向输入端通过一个电阻ra2连接到低噪声运算放大器的输出端;低噪声运算放大器的同相输入端通过电阻ra5与电阻ra3连接到vcom端,同时,通过电阻ra5与电阻ra6连接到两输入端子ina的引脚1,两输入端子ina的引脚2连接到公共的vcom端;低噪声运算放大器的输出端通过电阻ra4与电容ca1直接耦合到gnd,同时,通过电阻ra4连接八选一数据选择引脚,输出采集到的模拟信号;同时,通过电阻ra4连接单片机stm32g474qet6的u1a,进行模数转换;低噪声运算放大器的正电源引脚连接到vcc,低噪声运算放大器的负电源引脚连接到gnd;

35.如图3所示,所述stm32g474最小系统单元由128引脚的单片机stm32g474qet6、晶振、电阻、电容和发光二极管组成;所述单片机stm32g474qet6包括u1a、u1b和u1c三部分;u1a的引脚27、28、32、22、23、24、25和39分别与连接到多通道模拟信号前端单元输出的adc1_in1、adc1_in3、adc1_in4、adc1_in6、adc1_in7、adc1_in8、adc1_in9和adc1_in15,配置为adc1的8个输入通道;u1a的引脚28、35、36、37、38、41、34和69分别与连接到多通道模拟信号前端单元输出的adc2_in2、adc2_in3、adc2_in4、adc2_in5、adc2_in11、adc2_in12、adc2_in13和adc2_in14,配置为adc2的8个输入通道;u1b的引脚60、61、56、54和u1a的引脚66、68、69、71分别与连接到多通道模拟信号前端单元输出的adc4_in1、adc4_in2、adc4_in6、adc4_in14、adc4_in3、adc4_in4、adc4_in5和adc4_in13,配置为adc4的8个输入通道;u1a的引脚89、90、72、73、74、76、70和u1b的引脚58分别与连接到多通道模拟信号前端单元输出的adc5_in1、adc5_in2、adc5_in7、adc5_in8、adc5_in9、adc5_in11、adc5_in12和adc5_in16,配置为adc5的8个输入通道;一共配置4个adc,32路adc输入;

36.u1a的引脚40、39、67和65分别连接到数据选择单元的输出comp1_inp、comp4_inp、comp6_inp和comp5_inp,分别作为单片机stm32g474qet6内部配置四个比较器的同相输入端;比较器反相输入端分别由单片机stm32g474qet6内部的四个dac提供,实现内部触发设置;

37.u1b的引脚15、16、17、18、57和97分别连接静态存储单元u2芯片的引脚3、5、2、6、1和7,作为qspi1的传输引脚连接配置;u1a的引脚113、114、115、116和117分别连接静态存储单元u3芯片的引脚5、1、2、3和7,作为qspi2的传输引脚连接配置;u1a的引脚33通过发光二极管d1与电阻r4串联后连接到3v3电源,起到电源指示作用;u1a的引脚123通过电阻r2连接到gnd,用于boot0启动;u1b的引脚21通过电阻r1连接到gnd,用于复位;u1b的引脚19通过电阻r3连接到引脚20;晶振x1的引脚1连接到u1b引脚19,同时,晶振x1的引脚1通过电阻c1直接耦合到晶振x1的引脚2;晶振x1的引脚3连接到u1b引脚20,同时,晶振x1的引脚3通过电阻c2直接耦合到晶振x1的引脚4,晶振x1引脚4直接连接到gnd;u1c的引脚13、31、47、64、79、95、111、128、45、6、43和44连接到+3v3;u1c的引脚12、30、46、63、78、94、110和127连接到gnd;

38.如图4所示,所述数据选择单元由4个相同的单元构成,每个单元包括一个八选一模拟开关74hc4051,八选一模拟开关74hc4051的引脚13、14、15、12、1、5、2和4分别连接到八路模拟信号前端单元输出的adc1_in1、adc1_in3、adc1_in4、adc1_in6、adc1_in7、adc1_in8、adc1_in9和adc1_in10;八选一模拟开关74hc4051的引脚96、98和99分别连接到

stm32g474芯片的引脚91、92和93,做通道选择控制;八选一模拟开关74hc4051的引脚3作为输出选出引脚,连接到stm32g474芯片的引脚14,作为单片机内部比较器的同相输出引脚;八选一模拟开关74hc4051的引脚16直接连接到vcc;八选一模拟开关74hc4051的引脚6、7和8直接连接到gnd;

39.如图5所示,所述静态存储单元由两片静态随机存储器u2和u3构成;u2的引脚1、2、3、5、7和6分别连接到u1b的引脚57、17、15、16、97和18,作为qspi1的四条数据线、一条时钟线和一条片选线;u2的引脚4直接连接到gnd;u2的引脚8直接连接到电源端3v3;u3的引脚1、2、3、5、7和6分别连接到u1a的引脚113、115、116、114、117和u1b的引脚18,作为qspi2的四条数据线、一条时钟线和一条片选线;u3的引脚4直接连接到gnd;u3的引脚8直接连接到电源端3v3;

40.如图6所示,所述参考电压基准单元由低噪声运算放大器和电阻组成;所述低噪声运算放大器的同相输入引脚3通过电阻ra8直接连接到vcc,同时通过电阻ra9直接连接到gnd;低噪声运算放大器的反相输入引脚2通过电阻ra7直接连接到运算放大器的输出引脚1,同时输出引脚作为电压输出vcom;输出参考电压基准的值为vcc/2,提供给输入端子的公共端vcom:

41.如图7所示,所述usb通信供电单元由一个双层usb接口jusb1组成;jusb1的引脚1与引脚5直接连接到vcc电源端;jusb1的引脚6直接连接到u1a的引脚92,jusb1的引脚7直接连接到u1a的引脚93,配置为通信引脚;jusb1的引脚4、引脚8和引脚9直接连接到gnd;

42.如图8所示,所述电压转换单元由线性稳压芯片1117-3v3和多个电容组成;线性稳压芯片1117-3v3的引脚3连接vcc,同时,通过滤波电容e1耦合到gnd;引脚1直接连接gnd;线性稳压芯片1117-3v3引脚2和引脚4作为输出引脚,直接输出3.3v电压,同时,通过滤波电容e2耦合到gnd;电压转换单元转换来自vcc的5v电压,输出3.3v电压给单片机进行供电。

43.按照以上具体实施方式给出的技术参数,本实用新型一种精简型多通道准同步音频采集电路具有以下指标:模拟信号处理电路为单电源供电,由usb连接的外部设备提供,电压vcc为5v,可使用移动电脑端或者充电宝进行供电,简化了电路结构,降低了电路成本与功耗;使用单片机stm32g474自带的12位分辨率的adc,每个adc使用8通道扫描模式,组合实现32通道adc数据采集的扩展;同时,采用过采样技术,将信号的信噪比提高,增加adc的动态范围指标;使用软件插值算法,增加采样点的个数,实现多通道准同步采样;使用四个八选一数据选择器,将输出结果分别传输到单片机g474内部配置四路比较器的同相输入端,实现触发功能,触发后的数据经usb传输到上位机;使用两片外部sram,可将采集的数据进行存储;仅使用一片数字处理芯片stm32g474,实现准同步采样、过采样、数据传输与数据存储等功能,大大的提高了电路的集成度,使电路更加精简。

44.以上显示和描述了本实用新型的基本原理和主要特征和本实用新型的优点。本行业的技术人员应该了解,本实用新型不受上述实施例的限制,上述实施例和说明书中描述的只是说明本实用新型的原理,在不脱离本实用新型精神和范围的前提下,本实用新型还会有各种变化和改进,这些变化和改进都落入要求保护的本实用新型范围内。本实用新型要求保护范围由所附的权利要求书及其等效物界定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1