射频电路板、射频模组以及终端设备的制作方法

1.本技术涉及射频通信技术领域,尤其涉及一种射频电路板、射频模组以及终端设备。

背景技术:

2.随着通信技术的发展和进步,5g移动通信技术逐渐开始应用于通信设备,例如手机、平板电脑等中。5g组网方式包括非独立组网(non-standalone,nsa)模式和独立组网(standalone,sa)模式。其中,nsa模式是一对多的组网模式,一个核心网带两种基站,简单来说就是4g核心网(lte)/5g核心网(nr core)+4g基站(epc)+5g基站(nr)的组合模式,在nsa模式下,发射信号的5g基站仍接入4g核心网中,并且在整个网络架构中,5g基站和4g基站共存,部分通信功能依然需要借助4g基站实现,因此称为“非独立”组网。而sa模式是一对一的组网模式,一个核心网配一种基站,在sa模式下,端到端将同步支持5g网络通信,即基于5g核心网部署5g基站,因此称为“独立”组网。

3.在通信设备中,射频模组用于实现射频能量和信息传递,是通信设备实现无线通信功能的核心部件。射频模组通常包括射频电路板和位于射频电路板上的元器件。对于支持5g通信技术的通信设备来说,5g sa模式和5g nsa模式对应的射频电路板设计是不同的,二者不能兼容。另外,对于支持5g通信技术的低端和中高端产品来说,射频电路板设计也是不同的,二者也不能兼容。在产品开发阶段,需要为支持5g通信技术的低端产品和中高端产品、支持5g sa模式的产品、支持5g nsa模式的产品分别设计不同的射频电路板,这无疑会增加开发难度、延长开发周期、提高开发成本。因此,急需一种射频电路板的兼容性的方案,用于实现各种规格(例如低端/中端/高端)的产品以及支持不同网络模式(例如5g sa模式和5g nsa模式)的产品的射频模组的共板兼容。

技术实现要素:

4.本技术提供一种射频电路板、射频模组以及终端设备,所述射频电路板能够实现不同规格以及不同网络模式的终端设备的射频模组的共板兼容,从而能够有效地降低所述射频电路板的开发难度、缩短所述射频电路板的开发周期、降低所述射频电路板的开发成本,进而有利于降低终端设备的射频模组的研发和生产成本。

5.第一方面,本技术提供一种射频电路板,所述射频电路板包括基板、设置于所述基板内的兼容电路、以及设于所述基板的一表面上的第一焊接区域和第二焊接区域。所述第一焊接区域和所述第二焊接区域中均设置有与所述兼容电路电连接的焊盘。所述第一焊接区域与第一射频模组的第一功率放大器模组和第二射频模组的第二功率放大器模组中的任意一个均匹配,所述第一焊接区域用于焊接所述第一功率放大器模组或所述第二功率放大器模组。所述第二焊接区域与所述第二射频模组的第三功率放大器模组匹配,并用于焊接所述第三功率放大器模组。所述兼容电路通过所述第一焊接区域中的焊盘与焊接于所述第一焊接区域上的所述第一功率放大器模组或所述第二功率放大器模组电连接,以及通过

所述第二焊接区域中的焊盘与焊接于所述第二焊接区域上的所述第三功率放大器模组电连接。

6.在本技术实施例提供的所述射频电路板中,由于焊接区域以及所述兼容电路能够兼容不同的射频模组所包含的元器件,因此可通过同一种射频电路板来获得不同的射频电路,从而实现了支持不同网络模式射频模组共板兼容,进而能够实现不同地区以及不同规格的终端设备的射频模组的共板兼容。同时还能够有效地降低所述射频电路板的开发难度、缩短所述射频电路板的开发周期、降低所述射频电路板的开发成本,从而有利于降低终端设备的射频模组的研发和生产成本。

7.在实际应用中,可以根据射频模组所支持的组网模式的需要,在所述射频电路板上焊接上所需的元器件,就能得到支持第一网络的第一组网模式的射频模组或支持第一网络的第二组网模式的射频模组。

8.在一种实施例中,所述射频电路板还包括设于所述基板的所述表面上的第三焊接区域,其中,所述第三焊接区域中设置有与所述兼容电路电连接的焊盘。所述第三焊接区域与所述第一射频模组的信号接收模组或所述第二射频模组的信号接收模组匹配,并用于焊接所述信号接收模组,所述兼容电路通过所述第三焊接区域中的焊盘与焊接于所述第三焊接区域上的所述信号接收模组电连接。

9.在一种实施例中,所述射频电路板还包括设于所述基板的所述表面上的第四焊接区域,其中,所述第四焊接区域中设置有与所述兼容电路电连接的焊盘。所述第四焊接区域用于焊接所述第二射频模组的低噪声放大器模组和滤波单元,所述兼容电路还分别通过所述第四焊接区域中的相应焊盘与焊接于所述第四焊接区域上的所述低噪声放大器模组以及所述滤波单元电连接。

10.在一种实施例中,所述射频电路板还包括设于所述基板的所述表面上的第五焊接区域,其中,所述第五焊接区域中设置有与所述兼容电路电连接的焊盘。所述第五焊接区域与所述第一射频模组的第四功率放大器模组或所述第二射频模组的第四功率放大器模组匹配,并用于焊接所述第四功率放大器模组,所述兼容电路还通过所述第五焊接区域中的焊盘与焊接于所述第五焊接区域上的所述第四功率放大器模组电连接。

11.第二方面,本技术提供一种射频模组,所述射频模组支持第一网络的第一组网模式。所述射频模组包括上述的射频电路板以及第一功率放大器模组。所述第一功率放大器模组焊接于所述第一焊接区域中,并通过所述第一焊接区域中的焊盘与所述兼容电路电连接,其中,所述第一功率放大器模组用于对所述射频模组所支持的网络的各频段的射频信号进行功率放大。

12.在一种实施例中,所述第一功率放大器模组包括lmh lpamid器件,所述lmh lpamid器件与所述第一焊接区域在形状和尺寸上均相互匹配,且所述lmh lpamid器件包含与所述第一焊接区域上设置的焊盘一一对应连接的管脚。

13.在本实施例中,所述射频模组采用模组方式将mmmb pa、gsm pa、asm、lna bank、滤波单元(例如滤波器和双工器等)等都集成于所述lmh lpamid器件中,避免采用多个外挂的功率放大器器件、开关器件、滤波器件等,可以提高所述射频模组的集成度,从而可以地减小所述射频模组包含的元器件在所述射频电路板上占用的面积。另外,由于元器件集成度的提高,因此也简化所述射频模组的架构,降低了所述射频电路板的布线复杂性、开发难度

和开发成本。

14.在一种实施例中,所述射频模组还包括信号接收模组,所述信号接收模组用于接收所述射频模组所支持的网络的射频信号。所述射频电路板还包括设于所述基板的所述表面上的第三焊接区域,其中,所述第三焊接区域中设置有与所述兼容电路电连接的焊盘,所述信号接收模组焊接于所述第三焊接区域中,并通过所述第三焊接区域中的焊盘与所述兼容电路电连接。其中,所述信号接收模组包括lmh ldifem器件,所述lmh ldifem器件与所述第三焊接区域在形状和尺寸上均相互匹配,且所述lmh ldifem器件包含与所述第三焊接区域上设置的焊盘一一对应连接的管脚。

15.在一种实施例中,所述射频电路板还包括设于所述基板的所述表面上的第四焊接区域,其中,所述第四焊接区域中设置有与所述兼容电路电连接的焊盘。所述第二焊接区域以及所述第四焊接区域空置。

16.在一种实施例中,所述第一网络包括5g网络,所述第一组网模式为5g网络的sa模式。

17.在一种实施例中,所述射频模组还支持第二网络和第三网络,其中,所述第二网络包括3g网络和4g网络,所述第三网络包括2g网络。

18.所述第一功率放大器模组用于对所述第一网络和所述第二网络的各频段的射频信号进行功率放大。所述射频模组还包括第四功率放大器模组,所述第四功率放大器模组用于对所述第三网络的各频段的射频信号进行功率放大。

19.所述射频电路板还包括设于所述基板的表面上的第五焊接区域,所述第五焊接区域中设置有与所述兼容电路电连接的焊盘,所述第四功率放大器模组焊接于所述第五焊接区域中,并通过所述第五焊接区域中的焊盘与所述兼容电路电连接。

20.其中,所述第四功率放大器模组包括gsm pa器件,所述gsm pa器件与所述第五焊接区域在形状和尺寸上均相互匹配,且所述gsm pa器件包含与所述第五焊接区域上设置的焊盘一一对应连接的管脚。

21.第三方面,本技术提供一种射频模组,所述射频模组支持第一网络的第二组网模式。所述射频模组包括上述的射频电路板、第二功率放大器模组以及第三功率放大器模组。所述第二功率放大器模组焊接于所述第一焊接区域中,并通过所述第一焊接区域中的焊盘与所述兼容电路电连接,其中,所述第二功率放大器模组用于对所述射频模组所支持的网络的第一预设频段的射频信号进行功率放大。所述第三功率放大器模组,焊接于所述第二焊接区域中,并通过所述第二焊接区域中的焊盘与所述兼容电路电连接,其中,所述第三功率放大器模组用于对所述射频模组所支持的网络的第二预设频段的射频信号进行功率放大。

22.在一种实施例中,所述第二功率放大器模组包括mhb lpamid器件,所述mhb lpamid器件与所述第一焊接区域在形状和尺寸上均相互匹配,且所述mhb lpamid器件包含与所述第一焊接区域上设置的焊盘一一对应连接的管脚。所述第三功率放大器模组包括lb lpamid器件,所述lb lpamid器件与所述第二焊接区域在形状和尺寸上均相互匹配,且所述lb lpamid器件包含与所述第二焊接区域上设置的焊盘一一对应连接的管脚。

23.在本实施例中,所述射频模组采用模组方式将mmmb pa、gsm pa、asm、部分lna、部分滤波单元等都集成于所述lb lpamid器件和/或所述mhb lpamid器件中,避免采用多个外

挂的功率放大器器件、开关器件等,从而提高了所述射频模组的集成度,可以减少所述射频模组包含的元器件在所述射频电路板上占用的面积。另外,由于元器件集成度的提高,因此也简化所述射频模组的架构,降低了所述射频电路板的布线复杂性、开发难度和开发成本。

24.在一种实施例中,所述射频模组还包括信号接收模组,所述信号接收模组用于接收对所述射频模组所支持的网络的射频信号。所述射频电路板还包括设于所述基板的所述表面上的第三焊接区域,其中,所述第三焊接区域中设置有与所述兼容电路电连接的焊盘,所述信号接收模组焊接于所述第三焊接区域中,并通过所述第三焊接区域中的焊盘与所述兼容电路电连接。其中,所述信号接收模组包括lmh ldifem器件,所述lmh ldifem器件与所述第三焊接区域在形状和尺寸上均相互匹配,且所述lmh ldifem器件包含与所述第三焊接区域上设置的焊盘一一对应连接的管脚。

25.在一种实施例中,所述射频模组还包括低噪声放大器模组以及滤波单元。所述射频电路板还包括设于所述基板的所述表面上的第四焊接区域,其中,所述第四焊接区域中设置有与所述兼容电路电连接的焊盘,所述低噪声放大器模组以及所述滤波单元分别焊接于所述第四焊接区域中,并通过所述第四焊接区域中的相应焊盘与所述兼容电路电连接。其中,所述滤波单元包括滤波器和双工器。

26.对比上第二方面提供的射频模组和第三方面提供的射频模组可知,虽然所述射频电路板应用到第二方面的射频模组中时会存在多余的第二焊接区域以及第四焊接区域,但在第二方面的射频模组的射频电路板上预留空置的第二焊接区域以及第四焊接区域,可以实现第二方面的射频模组和第三方面的射频模组的共板兼容,有利于缩短两种射频模组的开发周期、降低开发成本。

27.在一种实施例中,所述第一网络包括5g网络,所述第二组网模式为5g网络的nsa模式。

28.在一种实施例中,所述射频模组还支持第二网络和第三网络,其中,所述第二网络包括3g网络和4g网络,所述第三网络包括2g网络。

29.所述第二功率放大器模组用于对所述第一网络和所述第二网络的第一预设频段的射频信号进行功率放大,所述第三功率放大器模组用于对所述第一网络和所述第二网络的第二预设频段的射频信号进行功率放大。

30.所述射频模组还包括第四功率放大器模组,所述第四功率放大器模组用于对所述第三网络的各频段的射频信号进行功率放大。

31.所述射频电路板还包括设于所述基板的表面上的第五焊接区域,所述第五焊接区域中设置有与所述兼容电路电连接的焊盘,所述第四功率放大器模组焊接于所述第五焊接区域中,并通过所述第五焊接区域中的焊盘与所述兼容电路电连接。

32.其中,所述第四功率放大器模组包括gsm pa器件,所述gsm pa器件与所述第五焊接区域在形状和尺寸上均相互匹配,且所述gsm pa器件包含与所述第五焊接区域上设置的焊盘一一对应连接的管脚。

33.对比上第二方面提供的射频模组和第三方面提供的射频模组可知,虽然所述射频电路板应用到第二方面的射频模组中时会存在多余的第二焊接区域以及第四焊接区域,而所述射频电路板应用到第三方面的射频模组中时会存在多余的第五焊接区域,但在第二方面的射频模组的射频电路板上预留空置的第二焊接区域以及第四焊接区域,以及在第三方

面的射频模组的射频电路板上预留空置的第五焊接区域,可以实现第二方面的射频模组和第三方面的射频模组的共板兼容,有利于缩短两种射频模组的开发周期、降低开发成本。

34.第四方面,本技术提供一种终端设备,所述终端设备包括壳体以及上述的射频模组,所述射频模组设置于所述壳体内。

附图说明

35.为了更清楚地说明本技术的实施例中的技术方案,下面将对本技术的实施例中所需要使用的附图作简单地介绍。显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

36.图1为本技术的实施例提供的一种终端设备的立体示意图。

37.图2为图1所示的终端设备的功能模块示意图。

38.图3为本技术的实施例提供的射频模组的第一种架构示意图。

39.图4为本技术的实施例提供的射频模组的第二种架构示意图。

40.图5为本技术的实施例提供的射频模组的第三种架构示意图。

41.图6为本技术的实施例提供的一种射频电路板的表面线路布局示意图。

42.图7为图6所示的射频电路板的一种剖面架构示意图。

43.图8为本技术的实施例提供的第一射频模组的一种架构示意图,所述第一射频模组支持第一网络的第一组网模式。

44.图9为本技术的实施例提供的第二射频模组的一种架构示意图,所述第二射频模组支持第一网络的第二组网模式。

45.图10为本技术的实施例提供的另一种射频电路板的表面线路布局示意图。

46.图11为本技术的实施例提供的第一射频模组的另一种架构示意图,所述第一射频模组支持第一网络的第一组网模式。

47.图12为本技术的实施例提供的第二射频模组的另一种架构示意图,所述第二射频模组支持第一网络的第二组网模式。

48.主要元件符号说明

[0049][0050][0051]

如下具体实施方式将结合上述附图进一步说明本技术。

具体实施方式

[0052]

下面将结合本技术的实施例中的附图,对本技术的实施例中的技术方案进行清楚、完整地描述。其中,附图仅用于示例性说明,表示的仅是示意图,不能理解为对本技术的限制。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

frequency front-end,rffe)、射频收发(rf transceiver)模组和基带(base band,bb)信号处理器四个部分,这四个部分共同组成接收通路/下行链路(即receive,rx)和发射通路/上行链路(即transmit,tx)。其中,所述射频前端为所述终端设备100的无线通信系统200的重要部分,是实现所述终端设备100与其他各类移动终端之间的通信功能的核心部件。

[0061]

从3g时代开始,出于节省电路板pcb的面积、降低手机厂商研发难度的考虑,射频前端逐渐由分立器件走向模组/模块。在4g时代,射频前端以分立和模组两种方式并立于世。在入门级机型,即低端产品上,采用分立器件的方式也完全能够满足各方面的要求。而出于空间和成本的考量,中高端机型通常采用射频前端模组。模组方式要求“高集成度和高性能”,而分立方式要求“中低集成度和中等性能”,两种方式之间存在巨大的技术和市场差异。2016年以后,模组方式渐成为主流,先后有asm(antenna switch module,天线开关模组)、femid(集成双工器的射频前端模组,front-end module with integrated duplexer)登上舞台,最后演进出集成了多模多频放大器模组(multi-mode multi-band bower amplifier module,mmmb pa)、rf开关、滤波器等元件的集成双工器的功率放大器模组(power amplifier module with integrated duplexer,pamid)。

[0062]

随着5g时代的到来,终端设备中的天线和射频通路的数量显著增多,对射频低噪声放大器(low noise amplifier,lna)的数量需求迅速增加,而终端设备的电路板已没有更多的空间。在这种情况下,从pamid到集成了lna的pamid,即lpamid,射频前端可以实现更小尺寸以及支持更多功能。

[0063]

下面结合具体的示意图来对本技术的终端设备100所包含的射频模组的架构进行介绍。应说明的是,本技术所述的“射频模组”对应于上述的射频前端。

[0064]

示例性的,图3为射频模组20的第一种架构示意图,所述射频模组20采用分立方式设置元器件。如图3所示,所述射频模组20可包括射频电路板21以及分立设置于所述射频电路板21上的多个分立元器件,所述多个分立元器件包括但不限于若干个功率放大器模组22、信号接收模组23、低噪声放大器模组(low noise amplifier bank,lna bank)24、若干个滤波单元25、以及天线开关模组(antenna switch module,asm)26等。

[0065]

其中,所述功率放大器模组22可包括全球移动通信系统信号的功率放大器模组(power amplifier module for global system for mobile communication,gsm pa)以及若干个多模多频功率放大器模组(multi-mode multi-band power amplifier module,mmmb pa)。所述信号接收模组23包括分集接收模组(low-band/middle-band/high-band diversity front-end module,lmh ldifem,集成射频低噪声放大器、射频开关和声表面波(surface acoustic wave,saw)滤波器)。所述滤波单元25可包括滤波器和双工器等。其中,所述射频模组20所包括的各个分立元器件均可采用现有的电子器件,其具体结构为现有结构,在此不予详述。

[0066]

从图3所示的所述射频模组20的架构可看出,所述射频模组20采用分立方式设置的元器件在所述射频电路板21上占用了较大的面积。

[0067]

随着5g时代对lpamid需求的增加,如图4所示,本技术的实施例还提供了射频模组30的第二种架构,所述射频模组30采用模组方式设置元器件。其中,所述射频模组30可包括射频电路板31以及设置于所述射频电路板31上的多个元器件,所述多个元器件包括但不限于若干个功率放大器模组32、信号接收模组33、低噪声放大器模组34、以及若干个滤波单元

35等。其中,所述功率放大器模组32可包括lb lpamid器件(主集prx)和mhb lpamid器件(主集prx),所述信号接收模组33可包括lmh ldifem器件(分集drx),所述低噪声放大器模组34可包括lna bank器件(分集drx),所述滤波单元35可包括滤波器和双工器等。

[0068]

在本技术实施例中,所述射频模组30所包括的各个元器件均可采用现有的电子器件,其具体结构为现有结构,在此不予详述。

[0069]

在图4所示的实施例中,所述射频模组30采用模组方式将mmmb pa、gsm pa、asm、lna(主集prx)、滤波单元(主集prx)等都集成于所述lb lpamid器件和/或所述mhb lpamid器件中,避免采用多个外挂的功率放大器器件、开关器件等,从而提高了所述射频模组30的集成度,可以减少所述射频模组30包含的元器件在所述射频电路板31上占用的面积。另外,由于元器件集成度的提高,因此也降低了所述射频电路板31的布线复杂性和开发成本。

[0070]

可以理解的是,随着5g射频复杂度的显著提升,使用分立方式不仅需要占用射频电路板较大的面积,还可能会带来3~5倍的调试时间增加;从成本上来讲,还需要消耗更贵的5g测试设备以及熟悉5g测试的工程师资源,导致成本较高。而使用模组方式,大部分的调试已经在模组设计过程中在模组内部实现了,调试工作量将更多地移到软件端,因此调试效率大大提升,同时还可以达到降低成本的目的。

[0071]

另外,所述射频模组30包含了分立设置的功率放大器模组,即lb lpamid器件和mhb lpamid器件,使得所述射频模组30可以支持对4g lte信号和5g nr信号的同时放大,从而可以实现对4g lte信号和5g nr信号的双发射功能,能满足4g lte信号和5g nr信号不同频段之间的en-dc组合的配置要求。因此,所述射频模组30可应用于支持nsa模式的各种系列,例如低端系列、中端系列、或高端系列的终端设备中。

[0072]

对于非独立组网(nsa)来说,随着时间的发展,它最终也是往独立组网(sa)的方向演进的,由于sa模式是一对一的组网模式,一个核心网配一种基站。为了适应5g网络的发展趋势,有必要提出一种集成度更高的射频模组。如图5所示,本技术的实施例还提供了射频模组40的第三种架构,所述射频模组40采用模组方式设置元器件。其中,所述射频模组40可包括射频电路板41以及设置于所述射频电路板41上的功率放大器模组42和信号接收模组43。所述功率放大器模组42可包括lmh lpamid器件,所述信号接收模组43可包括lmh ldifem。在本技术实施例中,所述射频模组40所包括的各个元器件均可采用现有的电子器件,其具体结构为现有结构,在此不予详述。

[0073]

在图5所示的实施例中,所述射频模组40采用模组方式将mmmb pa、gsm pa、asm、lna bank、滤波单元等都集成于所述lmh lpamid器件中,避免采用多个外挂的功率放大器器件、开关器件、滤波器件等,可以进一步地提高所述射频模组40的集成度,从而可以进一步地减小所述射频模组40包含的元器件在所述射频电路板41上占用的面积以及简化所述射频模组40的架构。另外,由于所述射频模组40的元器件集成度的进一步提高,因此也进一步地降低了所述射频电路板41的布线复杂性和开发成本。所述射频模组40可应用于支持sa模式的各种系列,例如低端系列、中端系列、或高端系列的终端设备中。

[0074]

由于nsa模式的5g网络并不是独立的,而是基于4g网络的基础设施改造,然后接入5g网络;sa模式的5g网络则是基于新建的5g网络的基础设施,然后由5g基站接入5g核心网。相较于nsa模式,sa模式的精细化管理比nsa模式更显优势,且sa模式在低延时、大连接方面也更有优势,覆盖加倍,速率加倍。然而,由于新建的5g基站的成本较大,速度也慢,目前很

多地区都是在原有的4g网络基站之类的设备上升级改造,然后接入5g网络。也就是说,在未来的很长一段时间内,nsa模式和sa模式的5g网络需要共存。

[0075]

由于5g网络的sa模式和nsa模式是两种不同的组网模式,对于支持sa模式的射频模组以及支持nsa模式的射频模组来说,两者在架构、指标/规格上均存在差异。针对架构、指标/规格不同的射频模组,目前通常都是分别设计相应的射频电路板,即,一种射频电路板仅支持一种类型的射频模组。

[0076]

由于5g射频复杂度有显著提升,若针对各种规格(例如低端/中端/高端)的产品、以及不同网络模式(例如5g sa模式和5g nsa模式)的产品的射频模组分别设计相应的射频电路板,这种解决方法无疑会增加需要设计的电路板的数量,从而导致射频电路板的开发难度增加,开发周期延长,物料成本、开发的人力成本、生产成本等均提高。

[0077]

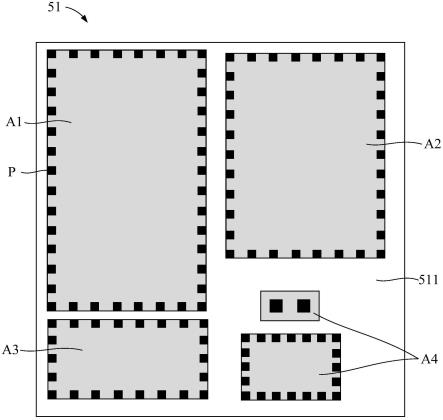

针对支持5g网络的终端设备的射频模组,为了缩短射频电路板的设计周期以及降低射频电路板的开发成本,请一并参阅图6和图7,本技术的实施例还提供了一种射频电路板51,所述射频电路板51用于兼容第一射频模组和第二射频模组,其中,所述第一射频模组支持第一网络的第一组网模式,所述第二射频模组支持所述第一网络的第二组网模式。

[0078]

其中,图6示例性地示出了所述射频电路板51的表面线路布局示意图,图7示例性地示出了所述射频电路板51的一种剖面架构示意图。如图6和图7所示,所述射频电路板51包括基板511以及设置于所述基板511内的兼容电路512。

[0079]

具体地,所述基板511包括多层层叠结构,所述层叠结构至少包括依次层叠设置的第一绝缘层l1、第一金属层m1、第二绝缘层l2、第二金属层m2和第三绝缘层l3。其中,所述第一金属层m1可为金属走线层,所述兼容电路512可设置于所述第一金属层m1中,所述第二金属层m2可为金属接地层。所述第一金属层m1和所述第二金属层m2通过所述第二绝缘层l2间隔开,且彼此绝缘。

[0080]

所述基板511还用于焊接所述第一射频模组或所述第二射频模组所需的元器件。在本实施方式中,所述基板511的一表面,即所述第一绝缘层l1远离所述第一金属层m1的表面上设有第一焊接区域a1、第二焊接区域a2、第三焊接区域a3和第四焊接区域a4,各个焊接区域a1-a4中均设置有与所述兼容电路512电连接的焊盘p。其中,所述焊盘p可以通过电镀、印刷等方式形成于所述基板511的所述表面上。所述第一绝缘层l1中可对应各个所述焊盘p形成有贯通孔,所述贯通孔中可填充有导电材料。可以理解的是,所述兼容电路512可预留有多个连接端口,所述连接端口通过相应的贯通孔中的导电材料与所述基板511表面上设置的相应的焊盘p电连接,从而可实现所述兼容电路512与各个焊盘p的电连接。

[0081]

在本实施例中,所述第一网络包括5g网络,所述第一组网模式可为5g网络的sa模式,所述第一射频模组可包括第一功率放大器模组和信号接收模组。其中,所述第一功率放大器模组用于对所述第一射频模组所支持的网络的各频段(例如低频段、中频段和高频段),即全频段的射频信号进行功率放大。所述第一射频模组包括的信号接收模组用于接收所述第一射频模组所支持的网络的各频段的射频信号。

[0082]

所述第二组网模式可为5g网络的nsa模式,所述第二射频模组可包括第二功率放大器模组、第三功率放大器模组、信号接收模组、低噪声放大器模组以及滤波单元。其中,所述第二功率放大器模组用于对所述第二射频模组所支持的网络的第一预设频段(例如中频段和高频段)的射频信号进行功率放大。所述第三功率放大器模组用于对所述第二射频模

组所支持的网络的第二预设频段(例如低频段)的射频信号进行功率放大。所述第二射频模组包括的信号接收模组用于接收所述第二射频模组所支持的网络的各频段的射频信号。所述滤波单元包括滤波器和双工器等。

[0083]

在本实施例中,所述第一焊接区域a1与所述第一功率放大器模组和所述第二功率放大器模组中的任意一个均匹配,所述第一焊接区域a1用于焊接所述第一功率放大器模组或所述第二功率放大器模组。所述兼容电路512通过所述第一焊接区域a1中的焊盘p与焊接于所述第一焊接区域a1上的所述第一功率放大器模组或所述第二功率放大器模组电连接。具体地,所述第一功率放大器模组和所述第二功率放大器模组可均以封装器件,例如芯片的形态存在,例如,所述第一功率放大器模组可采用图5所示的lmh lpamid器件,所述第二功率放大器模组可采用图4所示的mhb lpamid器件。所述第一功率放大器模组与所述第一焊接区域a1在形状和尺寸上均相互匹配,且所述第一功率放大器模组包含与所述第一焊接区域a1上设置的焊盘一一对应连接的管脚。同样的,所述第二功率放大器模组也与所述第一焊接区域a1在形状和尺寸上均相互匹配,且所述第二功率放大器模组包含与所述第一焊接区域a1上设置的焊盘p一一对应连接的管脚。

[0084]

所述第二焊接区域a2与所述第三功率放大器模组匹配,并用于焊接所述第三功率放大器模组。所述兼容电路512通过所述第二焊接区域a2中的焊盘p与焊接于所述第二焊接区域a2上的所述第三功率放大器模组电连接。具体地,所述第三功率放大器模组可以封装器件,例如芯片的形态存在,例如,所述第三功率放大器模组可采用图4所示的lb lpamid器件。所述第三功率放大器模组与所述第二焊接区域a2在形状和尺寸上均相互匹配,且所述第三功率放大器模组包含与所述第二焊接区域a2上设置的焊盘p一一对应连接的管脚。

[0085]

所述第三焊接区域a3与所述第一射频模组或所述第二射频模组包含的信号接收模组匹配,并用于焊接所述信号接收模组。所述兼容电路512通过所述第三焊接区域a3中的焊盘p与焊接于所述第三焊接区域a3上的所述信号接收模组电连接。具体地,所述信号接收模组可以封装器件,例如芯片的形态存在,例如,所述信号接收模组可采用图4或图5所示的lmh ldifem器件。所述信号接收模组与所述第三焊接区域a3在形状和尺寸上均相互匹配,且所述信号接收模组包含与所述第三焊接区域a3上设置的焊盘p一一对应连接的管脚。

[0086]

所述第四焊接区域a4用于焊接所述低噪声放大器模组和所述滤波单元,所述兼容电路512还分别通过所述第四焊接区域a4中的相应焊盘p与焊接于所述第四焊接区域a4上的所述低噪声放大器模组和滤波单元电连接。

[0087]

应说明的是,在图6和图7所示的实施例中,对各个焊接区域a1-a4的展示只是示意性的,并不表示对其形状和相对位置的限制。各个焊接区域a1-a4的形状由其所需要焊接的元器件的形状来决定,各个焊接区域a1-a4的相对位置可以根据实际设计需求进行调整。同样的,对各个焊接区域a1-a4中的焊盘p的展示只是示意性的,并不表示对其数量的限制。各个焊接区域a1-a4中所设置的焊盘的数量、位置由其所需要焊接的元器件的管脚数量、管脚位置和功能等决定。

[0088]

由于所述第一射频模组的第一功率放大模组与所述第二射频模组的第二功率放大模组共用所述射频电路板51的第一焊接区域a1,而所述第一功率放大器模组可采用lmh lpamid器件,所述第二功率放大器模组可采用mhb lpamid器件,因此可在元器件的封装阶段预先将lmh lpamid器件和mhb lpamid器件的管脚进行统一定义,以实现所述第一焊接区

域a1以及所述兼容电路512对两种器件,即lmh lpamid器件和mhb lpamid器件的兼容。

[0089]

在实际应用中,可以根据射频模组所支持的组网模式的需要,在所述射频电路板51上焊接上所需的元器件,就能得到支持第一网络的第一组网模式的第一射频模组或支持第一网络的第二组网模式的第二射频模组。

[0090]

在本实施例提供的所述射频电路板51中,各个焊接区域a1-a4以及兼容电路512能够兼容不同的射频模组所包含的元器件,因此可通过同一种射频电路板来获得不同的射频电路,从而实现了支持不同网络模式的第一射频模组和第二射频模组的共板兼容,进而能够实现不同地区以及不同规格的终端设备的射频模组的共板兼容。同时还能够有效地降低所述射频电路板51的开发难度、缩短所述射频电路板51的开发周期、降低所述射频电路板51的开发成本,从而有利于降低终端设备的射频模组的研发和生产成本。

[0091]

本技术的实施例还提供一种支持第一网络的第一组网模式的第一射频模组,其中,图8示例性地示出了第一射频模组60的一种架构示意图。如图8所示,所述第一射频模组60可包括所述射频电路板51以及设置于所述射频电路板51上的第一功率放大器模组61和信号接收模组62。其中,所述第一功率放大器模组61用于对所述第一射频模组60所支持的网络的各频段(例如低频段、中频段和高频段),即全频段的射频信号进行功率放大。所述信号接收模组62用于接收所述第一射频模组60所支持的网络的各频段的射频信号。

[0092]

在本实施例中,所述第一网络包括5g网络,所述第一组网模式为5g网络的sa模式。除了所述第一网络之外,所述第一射频模组60还可支持第二网络和第三网络,其中,所述第二网络包括3g网络和4g网络,所述第三网络包括2g网络,例如gsm网络。相应地,所述第一射频模组60所支持的网络的射频信号可包括gsm信号、3g信号、4g lte信号、5gnr信号。各种网络的射频信号的频段可与现有的频段相同,其具体频段划分为现有技术,在此不予详述。

[0093]

在本实施例中,所述第一功率放大器模组61用于对所述第一射频模组60所支持的所有网络的各频段的射频信号进行功率放大。所述信号接收模组62用于接收所述第一射频模组60所支持的所有网络的各频段的射频信号。

[0094]

所述第一功率放大器模组61焊接于所述射频电路板51的第一焊接区域a1中,并通过所述第一焊接区域a1中的焊盘p与所述兼容电路512电连接。所述信号接收模组62焊接于所述射频电路板51的第三焊接区域a3中,并通过所述第三焊接区域a3中的焊盘p与所述兼容电路512电连接。在本实施例中,所述射频电路板51包含的兼容电路512可以理解为所述第一功率放大器模组61和所述信号接收模组62的附属电路。

[0095]

所述第一射频模组60可采用与图5所示的射频模组40相似的架构,即,所述第一功率放大器模组61采用lmh lpamid器件,所述信号接收模组62采用lmh ldifem器件。其中,所述lmh lpamid器件与所述第一焊接区域a1在形状和尺寸上均相互匹配,且所述lmh lpamid器件包含与所述第一焊接区域a1上设置的焊盘p一一对应连接的管脚。所述lmh ldifem器件与所述第三焊接区域a3在形状和尺寸上均相互匹配,且所述lmh ldifem器件包含与所述第三焊接区域a3上设置的焊盘p一一对应连接的管脚。

[0096]

在本实施例中,所述第一射频模组60采用模组方式将mmmb pa、gsm pa、asm、lna bank、滤波单元(例如滤波器和双工器等)等都集成于所述lmh lpamid器件中,避免采用多个外挂的功率放大器器件、开关器件、滤波器件等,可以提高所述第一射频模组60的集成度,从而可以地减小所述第一射频模组60包含的元器件在所述射频电路板51上占用的面

积。另外,由于元器件集成度的提高,因此也简化所述第一射频模组60的架构,降低了所述射频电路板51的布线复杂性、开发难度和开发成本。相应地,所述第二焊接区域a2以及所述第四焊接区域a4空置。

[0097]

可选地,在其他实施例中,所述滤波单元的部分结构,例如滤波器或双工器等也可以独立于所述lmh lpamid器件中,并焊接于所述第四焊接区域a4中。

[0098]

在本实施例中,所述lmh lpamid器件用于主集天线射频链路,所述lmh lpamid器件还可理解为所述第一射频模组60的发射模组和主集接收模组,所述lmh lpamid器件用于实现对所述第一射频模组60所支持的网络的各频段的射频信号的发射和主集接收。

[0099]

所述lmh ldifem器件用于分集天线射频链路,所述lmh ldifem器件可理解为所述第一射频模组60的分集接收模组,所述lmh ldifem器件用于实现对所述第一射频模组60所支持的网络的各频段的射频信号的分集接收。

[0100]

应说明的是,在图8所示的实施例中,对设置于所述射频电路板51上的元器件的展示只是示意性的,可以理解为封装结构的示意图,并不表示对相应的元器件的形状和电路构造的限制。

[0101]

本技术的实施例还提供一种支持第一网络的第二组网模式的第二射频模组,其中,图9示例性地示出了第二射频模组70的一种架构示意图。如图9所示,所述第二射频模组70可包括所述射频电路板51以及设置于所述射频电路板51上的第二功率放大器模组71、第三功率放大器模组72、信号接收模组73、低噪声放大器模组74以及滤波单元75。其中,所述第二功率放大器模组71用于对所述第二射频模组70所支持的网络的第一预设频段的射频信号进行功率放大,所述第三功率放大器模组72用于对所述第二射频模组70所支持的网络的第二预设频段的射频信号进行功率放大,所述信号接收模组73用于接收所述第二射频模组70所支持的网络的各频段的射频信号。所述滤波单元75包括滤波器和双工器等。

[0102]

在本实施例中,所述第一网络包括5g网络,所述第二组网模式为5g网络的nsa模式。除了所述第一网络之外,所述第二射频模组70还可支持第二网络和第三网络,其中,所述第二网络包括3g网络和4g网络,所述第三网络包括2g网络,例如gsm网络。相应地,所述第一射频模组60所支持的网络的射频信号可包括gsm信号、3g信号、4g lte信号、5gnr信号。所述第一预设频段可包括各个网络的中频段和高频段,第二预设频段可包括各个网络的低频段。各种网络的射频信号的频段可与现有的频段相同,其具体频段划分为现有技术,在此不予详述。

[0103]

在本实施例中,所述第二功率放大器模组71用于对所述第二射频模组70所支持的所有网络的第一预设频段的射频信号进行功率放大,所述第三功率放大器模组72用于对所述第二射频模组70所支持的所有网络的第二预设频段的射频信号进行功率放大。所述信号接收模组73用于接收所述第二射频模组70所支持的所有网络的各频段的射频信号。

[0104]

所述第二功率放大器模组71焊接于所述射频电路板51的第一焊接区域a1中,并通过所述第一焊接区域a1中的焊盘p与所述兼容电路512电连接。所述第三功率放大器模组72焊接于所述射频电路板51的第二焊接区域a2中,并通过所述第二焊接区域a2中的焊盘p与所述兼容电路512电连接。所述信号接收模组73焊接于所述第三焊接区域a3中,并通过所述第三焊接区域a3中的焊盘p与所述兼容电路512电连接。所述低噪声放大器模组74和所述滤波单元75分别焊接于所述第四焊接区域a4中,并分别通过所述第四焊接区域a4中的相应焊

盘p与所述兼容电路512电连接。在本实施例中,所述射频电路板51包含的兼容电路512可以理解为所述第二射频模组70所包含的各个元器件的附属电路。

[0105]

所述第二射频模组70可采用与图4所示的射频模组30相似的架构,即,所述第二功率放大器模组71采用mhb lpamid器件,所述第三功率放大器模组72采用lb lpamid器件,所述信号接收模组73采用lmh ldifem器件,所述低噪声放大器模组74采用lna bank器件。其中,所述mhb lpamid器件与所述第一焊接区域a1在形状和尺寸上均相互匹配,且所述mhb lpamid器件包含与所述第一焊接区域a1上设置的焊盘p一一对应连接的管脚。所述lb lpamid器件与所述第二焊接区域a2在形状和尺寸上均相互匹配,且所述lb lpamid器件包含与所述第二焊接区域a2上设置的焊盘p一一对应连接的管脚。所述lmh ldifem器件与所述第三焊接区域a3在形状和尺寸上均相互匹配,且所述lmh ldifem器件包含与所述第三焊接区域a3上设置的焊盘p一一对应连接的管脚。

[0106]

在本实施例中,所述第二射频模组70采用模组方式将mmmb pa、gsm pa、asm、lna(主集prx)、滤波单元(主集prx)等都集成于所述lb lpamid器件和/或所述mhb lpamid器件中,避免采用多个外挂的功率放大器器件、开关器件等,从而提高了所述第二射频模组70的集成度,可以减少所述第二射频模组70包含的元器件在所述射频电路板51上占用的面积。另外,由于元器件集成度的提高,因此也简化所述第二射频模组70的架构,降低了所述射频电路板51的布线复杂性、开发难度和开发成本。

[0107]

在本实施例中,所述lb lpamid器件和所述mhb lpamid器件均用于主集天线射频链路,所述lb lpamid器件和所述mhb lpamid器件还可理解为所述第二射频模组70的发射模组和主集接收模组,所述lb lpamid器件和所述mhb lpamid器件用于实现对所述第二射频模组70所支持的网络的各频段的射频信号的发射和主集接收。

[0108]

所述lmh ldifem器件和所述lna bank器件均用于分集天线射频链路,所述lmh ldifem器件可理解为所述第二射频模组70的分集接收模组,所述lmh ldifem器件用于实现对所述第二射频模组70所支持的网络的各频段的射频信号的分集接收。

[0109]

应说明的是,在图9所示的实施例中,对设置于所述射频电路板51上的元器件的展示只是示意性的,可以理解为封装结构的示意图,并不表示对相应的元器件的形状和电路构造的限制。

[0110]

对比图8所示的第一射频模组60和图9所示的第二射频模组70可知,虽然所述射频电路板51应用到所述第一射频模组60中时会存在多余的第二焊接区域a2以及第四焊接区域a4,但在所述第一射频模组60的射频电路板51上预留空置的第二焊接区域a2以及第四焊接区域a4,可以实现所述第一射频模组60和所述第二射频模组70的共板兼容,有利于缩短所述第一射频模组60和所述第二射频模组70的开发周期、降低开发成本。

[0111]

请参阅图10,本技术的实施例还提供了另一种射频电路板51’。其中,图10所示的射频电路板51’的结构与图6所示的射频电路板51的结构相似,不同之处在于:所述射频电路板51’还包括设于所述基板511的所述表面上的第五焊接区域a5,其中,所述第五焊接区域a5中设置有与所述兼容电路512电连接的焊盘p。

[0112]

在本实施例中,所述射频电路板51’用于兼容图11所示的第一射频模组60’和图12所示的第二射频模组70’,相应地,所述第五焊接区域a5与所述第一射频模组60’包含的第四功率放大器模组63匹配,并用于焊接所述第四功率放大器模组63。所述兼容电路512还通

过所述第五焊接区域a5中的焊盘p与焊接于所述第五焊接区域a5上的所述第四功率放大器模组63电连接。具体地,所述第四功率放大器模组63可以封装器件,例如芯片的形态存在,例如,所述第四功率放大器模组63可采用gsm pa器件。所述第四功率放大器模组63与所述第五焊接区域a5在形状和尺寸上均相互匹配,且所述第四功率放大器模组63包含与所述第五焊接区域a5上设置的焊盘p一一对应连接的管脚。

[0113]

请参阅图11,本技术的实施例还提供了另一种第一射频模组60’。其中,图11所示的第一射频模组60’的结构与图8所示的第一射频模组60的结构相似,不同之处在于:图8所示的第一射频模组60包括的第一功率放大器模组61用于对所述第一射频模组60所支持的所有网络的各频段的射频信号进行功率放大。然而,在图11所示的第一射频模组60’中,除了第一功率放大器模组61’之外,所述第一射频模组60’还包括第四功率放大器模组63,所述第一功率放大器模组61’用于对所述第一射频模组60’所支持的第一网络和第二网络的各频段(例如低频段、中频段和高频段),即全频段的射频信号进行功率放大,所述第四功率放大器模组63用于对所述第一射频模组60’所支持的第三网络的各频段的射频信号进行功率放大。

[0114]

在本实施例中,所述第四功率放大器模组63焊接于所述射频电路板51的第五焊接区域a5中,并通过所述第五焊接区域a5中的焊盘p与所述兼容电路512电连接。如上所述,所述第四功率放大器模组63可包括gsm pa器件,所述gsm pa器件与所述第五焊接区域a5在形状和尺寸上均相互匹配,且所述gsm pa器件包含与所述第五焊接区域a5上设置的焊盘p一一对应连接的管脚。

[0115]

在图8所示的第一射频模组60中,lmh lpamid器件可理解为集成了图11所示的gsm pa、且支持2g/3g/4g/5g网络的pa器件。而在图11所示的第一射频模组60’中,gsm pa器件可理解为从图8所示的lmh lpamid器件中分离出来,从而得到支持2g网络的gsm pa器件和支持3g/4g/5g网络的pa器件(即第一功率放大器模组61’)。

[0116]

由于2g网络的pa器件的设计方法与3g/4g/5g网络的pa器件有较大的不同,将2g网络的pa器件(即gsm pa)与3g/4g/5g网络的pa器件(即第一功率放大器模组61’)进行分离,可以提高所述第一射频模组60’的设计的灵活性,同时为日后2g网络退网做好准备,使所述第一射频模组60’能够灵活切换到2g网络退网后的射频方案中。

[0117]

可选地,在其他实施例中,所述第四功率放大器模组63也可集成于所述第一功率放大器模组61’中,即所述第一功率放大器模组61’采用所述第一功率放大器模组61的结构。相应地,所述第五焊接区域a5空置。

[0118]

请参阅图12,本技术的实施例还提供了另一种第二射频模组70’。其中,图12所示的第二射频模组70’的结构与图9所示的第二射频模组70的结构相似,不同之处在于:图9所示的第二射频模组70包括图6所示的射频电路板51,所述射频电路板51未包含第五焊接区域a5;而图12所示的第二射频模组70’包括图10所示的射频电路板51’,所述射频电路板51’包含第五焊接区域a5,且所述第五焊接区域a5空置。

[0119]

其中,在图9和图12所示的实施例中,mhb lpamid器件和/或lb lpamid器件可理解为集成了的gsm pa的至少部分结构、且支持2g/3g/4g/5g网络的pa器件。

[0120]

对比图11所示的第一射频模组60’和图12所示的第二射频模组70’可知,虽然所述射频电路板51’应用到所述第一射频模组60’中时会存在多余的第二焊接区域a2以及第四

焊接区域a4,而所述射频电路板51’应用到所述第二射频模组70’中时会存在多余的第五焊接区域a5,但在所述第一射频模组60’的射频电路板51’上预留空置的第二焊接区域a2以及第四焊接区域a4,以及在所述第二射频模组70’的射频电路板51’上预留空置的第五焊接区域a5,可以实现所述第一射频模组60’和所述第二射频模组70’的共板兼容,有利于缩短所述第一射频模组60’和所述第二射频模组70’的开发周期、降低开发成本。

[0121]

可选地,在其他实施例中,在图12所示的第二射频模组70’中,除了第二功率放大器模组71和第三功率放大器模组72之外,所述第二射频模组70’还可包括第四功率放大器模组,其中,所述第二功率放大器模组71用于对所述第二射频模组70’所支持的第一网络和第二网络的第一预设频段的射频信号进行功率放大,所述第三功率放大器模组72用于对所述第二射频模组70’所支持的第一网络和第二网络的第二预设频段的射频信号进行功率放大,所述第四功率放大器模组用于对所述第二射频模组70’所支持的第三网络的各频段的射频信号进行功率放大。所述第四功率放大器模组可采用图11所示的gsm pa器件的结构,且焊接于所述射频电路板51’的第五焊接区域a5中,所述第四功率放大器模组的其他具体技术细节请参阅上文对图11所示的第四功率放大器模组63的具体介绍,在此不进行赘述。

[0122]

以上,仅为本技术的部分实施例,本技术的保护范围不局限于此,任何熟知本领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1