锁相环电路、滤波器和通讯设备的制作方法

1.本技术涉及锁相环电路技术领域,特别是涉及锁相环电路、滤波器和通讯设备。

背景技术:

2.对讲机中一般需要用到频率生成模块,在频率生成模块中会应用到锁相环电路。其中小数分频锁相环应用的比较多,且具有较大优势。

3.现有技术中的小数分频能够提高产生的信号的分辨率,但是也具有小数杂散的缺陷,当模拟信道距离小数边界杂散很近,恰好间隔为音频时,此时环路滤波作用很小,小数边界杂散幅度较高,一定会随着信号处理,最终解调出一个音频包含小数边界杂散。接收机被叫时,会叠加对应小数边界杂散的特征音,当小数边界杂散大于-38dbc时,会出现啸叫,严重影响使用体验。因此,需要降低小数杂散对机器特性的影响。

技术实现要素:

4.本技术提供锁相环电路、滤波器和通讯设备,能够减少小数杂散对信号的影响。

5.第一方面,本技术提供一种锁相环电路,该锁相环电路包括电荷泵电路、鉴相分频电路、环路滤波电路和分流电路。鉴相分频电路的输出端连接电荷泵电路,鉴相分频电路的第一输入端用于接收参考频率;环路滤波电路的输入端连接电荷泵电路的输出端,环路滤波电路的输出端连接鉴相分频电路的第二输入端;分流电路,分流电路的第一端连接环路滤波电路,分流电路的第二端接地;其中,电荷泵电路用于向环路滤波电路提供充放电电荷。

6.第二方面,本技术提供一种滤波器,该滤波器包括环路滤波电路和分流电路;分流电路的第一端连接环路滤波电路,分流电路的第二端接地。

7.本技术所提供的锁相环电路,在环路滤波电路处连接了一个分流电路,对环路滤波电路进行分流,从而改变了电荷泵电路下地电荷的脉冲幅度,缓和了控制电压的阶跃特性。分流电路在不改变分频比的情况下,打乱了电荷泵电路的输出,鉴相分频电路所产生的控制信号不会完整的传递给环路滤波电路,使得锁相环电路锁定之后,电荷泵电路的输出不完全与鉴相分频电路的输出线性相关,从而能够减少小数杂散对锁相环电路输出信号的影响,且在不增加失锁、谐振等系统性风险的前提下,改善小数杂散现象。

附图说明

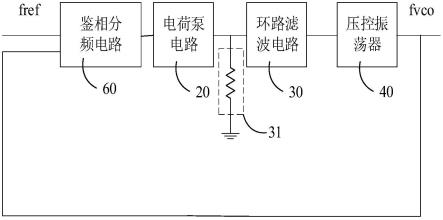

8.图1是本技术锁相环电路实施例第一实施方式的一电路结构示意框图;

9.图2是图1所示锁相环电路的另一电路结构示意框图;

10.图3是图1所示的环路滤波电路和分流电路的第一种电路结构示意图;

11.图4是图1所示的环路滤波电路和分流电路的第二种电路结构示意图;

12.图5是图1所示的环路滤波电路和分流电路的第三种电路结构示意图;

13.图6是本技术锁相环电路实施例第二实施方式的一电路结构示意框图;

14.图7是图6所示的环路滤波电路和分流电路的一结构示意图。

具体实施方式

15.为使本技术的上述目的、特征和优点能够更为明显易懂,下面结合附图,对本技术的具体实施方式做详细的说明。可以理解的是,此处所描述的具体实施例仅用于解释本技术,而非对本技术的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本技术相关的部分而非全部结构。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本技术保护的范围。

16.本技术中的术语“第一”、“第二”等是用于区别不同对象,而不是用于描述特定顺序。此外,术语“包括”和“具有”以及它们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。

17.在本技术中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本技术的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本技术所描述的实施例可以与其它实施例相结合。

18.图1是本技术锁相环电路实施例第一实施方式的一电路结构示意框图。图6是本技术锁相环电路实施例的第二实施方式的电路结构示意框图。图中fref为参考频率,fvco为压控振荡器输出端频率。

19.如图1和图6所示,锁相环电路包括鉴相分频电路60、电荷泵电路20、环路滤波电路30和分流电路31。鉴相分频电路60的输出端连接电荷泵电路20,鉴相分频电路60的第一输入端用于接收参考频率。环路滤波电路30的输入端连接电荷泵电路20的输出端,环路滤波电路30的输出端连接鉴相分频电路60的第二输入端;分流电路31的第一端连接环路滤波电路30。其中,电荷泵电路20用于向环路滤波电路30提供充放电电荷。

20.本技术的锁相环电路可以是小数分频锁相环。小数分频锁相环由于其固有特性和机制,会在特定的频率位置存在小数杂散,小数杂散会影响到电路的输出信号。本技术中,分流电路31在不改变分频比的情况下,打乱了电荷泵电路的输出,让电路锁定之后电荷泵电路20的输出不完全与鉴相分频电路60的输出线性相关,从而能够减少小数杂散对锁相环电路输出信号的影响。

21.本技术锁相环电路实施例对于环路滤波电路30和分流电路31的结构提供多个实施方式,以下示例性地描述其中几种。

22.(一)第一实施方式

23.如图1所示,分流电路31的第一端连接至电荷泵电路20的输出端和环路滤波电路30的输入端之间。换言之,分流电路31的第一端连接电荷泵电路的20的输出端,即连接环路滤波电路30的输入端。

24.图2是本技术锁相环电路实施例第一实施方式的另一电路结构示意框图。请参阅图2,图2所示的锁相环电路中,锁相环电路还包括压控振荡器40。

25.环路滤波电路30的输出端连接压控振荡器40的输入端,压控振荡器40的输出端连

接鉴相分频电路60的第二输入端。压控振荡器40基于环路滤波电路30的输出信号调整自身的频率或者相位。

26.环路滤波电路30的输出端电压可以是控制电压,即cv(control voltage)。压控振荡器40根据控制电压调整自身的频率和相位并在锁相环电路中作为输出电路向外提供载波频率。

27.鉴相分频电路60包括鉴相器10和分频器50。

28.鉴相器10的第一输入端接收参考频率,鉴相器10的第二输入端连接分频器50的输出端,鉴相器10的输出端连接电荷泵电路20的输入端,分频器50用于对压控振荡器40输出端的频率进行分频,鉴相器10用于基于参考频率和分频器50分频后的频率来控制电荷泵电路20的工作状态。

29.可选地,分频器50可以包括计数器、可编程分频器、n分频器、n计数器或者预分频器等。分频器50是用于设置锁相环电路输入频率和输出频率之间的关系的可编程元件,这里不再赘述。锁相环电路输入频率或者鉴相器10输入频率即参考频率。本技术中的分频器50可以是小数n分频计数器,此时本技术的锁相环电路为小数分频锁相环。小数n分频使得锁相环的分辨率可以降至鉴相器10输入频率的一部分。例如,鉴相器10输入频率为1mhz,锁相环电路可以产生分辨率为数百hz(赫兹)的输出频率,同时维持较高的鉴相器10输入频率。

30.电荷泵电路20基于鉴相器10的输出向环路控制器环路滤波电路30提供充放电电荷。

31.本技术中锁相环电路通过反馈控制来锁定其输出信号的频率。压控振荡器40输出端的频率即为锁相环电路的输出频率。鉴相器10比较参考频率和压控振荡器40输出端的频率和相位。鉴相器10在参考频率和压控振荡器40输出端的频率反馈频率之间的相位差小于某个值的概率大于设定值时,锁相环电路就变为锁定状态。反馈频率即压控振荡器40输出端的频率。具体地,小数杂散是由于锁相环电路的固有特性或者机制造成的。以实现100.1分频比为例,在锁相环电路中需要进行9次100分频和1次101分频,平均分频比为(100

×

9+101)/10=100.1。因此在瞬时状态下,分频器50输出信号和参考信号存在相位误差,这个相位误差使鉴相器10输出相应的周期性电压,小数锁相环的环路滤波电路30为低通滤波器,周期性电压将通过环路滤波电路30对压控振荡器40进行周期性频率调制,产生寄生杂散,这种杂散就是小数杂散。小数杂散会出现在特定的频率位置,在频谱上位于参考频率的整数倍的位置会出现幅度较大的杂散,影响锁相环电路输出频谱质量。

32.本技术中电荷泵电路20的输出端和环路滤波电路30的输入端之间设置分流电路31进行分流。由于高低频控制电压和泵电流的正相关属性,利用分流电路31可以调整流经环路滤波电路30的下地电荷的大小与上充电荷不完全相等。分流电路31在不改变分频比的情况下,打乱了电荷泵电路20的输出,分频器50的控制信号不会完整的传递给压控振荡器40。使得锁相环电路锁定之后,电荷泵电路20的输出不完全与分频器50的输出线性相关,从而能够减少小数杂散对锁相环电路输出信号的影响。

33.锁相环电路通过反馈控制实现输出信号的锁定。在锁相环电路中,锁相环电路中的分频是由分频器50完成的,分频器50接收压控振荡器40的输出端信号,进行分频后给到鉴相器10。分频器50的输出信号反馈给鉴相器10后,鉴相器10将分频器50的输出信号与参

考信号进行比较。在一些实施例中,压控振荡器40的输出端信号为频率,即fvco;分频器50反馈的也是反馈频率;参考信号也是频率。鉴相器10判断参考频率与反馈频率之间的相位差小于某个值的概率大于预设概率,锁相环电路就锁定了。然后鉴相器10控制电荷泵电路20进行充放电荷,从而使得环路滤波电路30的输出电压和相位稳定在特定的值。

34.当锁相环电路处于锁定状态,理想状态下环路滤波电路30的输出端的电压会稳定在某个值。但是实际情况是环路滤波电路30的输出端电压会在某个值左右不断变化,只是平均来看的话是稳定在某个值。环路滤波电路30的输出端电压是锁相环电路的输出信号的一部分。一般而言,我们不希望锁相环电路的输出信号出现较大波动。环路滤波电路30的输出端电压的波动与电荷泵电路20的充放电有一定的关系,而电荷泵电路20的充放电受小数杂散的影响。

35.本技术通过在电荷泵电路20的输出端和环路滤波电路30的输入端之间设置分流电路31,从而可以就是在电荷泵电路20处削弱小数杂散的影响。

36.具体地,电荷泵电路20包括上充电荷泵(图未示)和下放电荷泵(图未示)。电荷泵电路20接收鉴相器10的输出,并根据鉴相器10的输出调整上充电荷泵和下放电荷泵的开关状态。锁定状态下,上充电荷泵给环路滤波电路30上充的电荷量与下放电荷泵下放的电荷量在鉴相器10的一个周期内是相等的。电荷泵电路20上充或者下放电荷的动作由分频器50控制,而由上文我们可以知道,小数杂散与分频器50的动作密不可分。上充电荷和下放电荷的路径延迟或者开关管失配,会导致电荷泵开启、关闭时间失配,产生净输出电流,在锁相环电路的输出端引入杂散。

37.在一些实施方式中,上充电荷从电荷泵电路20流向环路滤波电路30的输出端,下放电荷从环路滤波电路30的输出端流向电荷泵电路20。在电荷泵电路20和环路滤波电路30之间设置分流电路31之后,上充电荷不变,依旧从电荷泵电路20流向环路滤波电路30的输出端。但是下放电荷全部或者部分从环路滤波电路30的输出端流经环路滤波电路30和分流电路31,并经分流电路31接地。这是由于锁定状态下,环路滤波电路30的输出端与地之间存在电势差,下放电荷自发的从环路滤波电路30的输出端流向地。下放电荷泵的动作变少了或者直接被电阻给替代了。例如,环路滤波电路30的输出端的电压为3v,而接地端的电压一般为0v。

38.锁相环电路为了保持环路滤波电路30的输出端电压不变,会调整下放电荷泵的工作状态,使得下放电荷泵所提供的下放电荷与流经分流电路31的下放电荷之和与上充电荷泵所提供的上充电荷在鉴相器10的一个周期内依然保持相等。电势上充电荷泵和下放电荷泵的工作平衡已经被打破了。下放电荷泵提供下放电荷的工作部分或者全部被分流电路31所代替。从宏观的角度上看,就削弱了小数杂散的信号强弱。因此,分流电路31可以在不改变分频比的情况下,打乱了电荷泵电路20的输出,分频器50的控制信号不会完整的传递给压控振荡器,从而削弱小数杂散对锁相环电路的输出信号的影响。

39.可选地,上充电荷和下放电荷可以是极性相同的电荷,但是上充电和下放电荷的在电路中的流向是相反的。例如上充电荷和下放电荷均为正电荷,上充电荷由电荷泵电路20流向环路滤波电路30,下放电荷泵由环路滤波电路30流向电荷泵电路20。

40.可选地,分流电路31可以包括阻值固定的第一电阻31a。利用阻值固定的第一电阻31a进行分流,有利于电路的稳定。第一电阻31a的阻值可以设置的较大,由于电荷泵电路20

所提供的电流是固定的,第一电阻31a的阻值设置的较大的时候,分流的电流也较少,电阻发热较少,从而可以减少电路发热所带来的危害,且通过第一电阻31a进行分流来实现削弱小数杂散对锁相环电路的输出信号的影响,成本也比较低,而且电路结构简单,无须鉴相频率的动态配置,代码一致性较好,还能节省空间,调试难度也比较低。其中,第一电阻31a的阻值可以根据实际需要进行设置。图3示出了环路滤波电路30和分流电路31的第一种电路结构。如图3示出的分流电路31,第一电阻31a的第一端连接电荷泵电路20的输出端,第一电阻31a的第二端接地。在图3所示分流电路31的基础上可以增加二极管,通过二极管控制第一电阻31a接入电路的时机。

41.图4示出了环路滤波电路30和分流电路31的第二种电路结构。如图4所示,分流电路31可以包括第一二极管37。第一二极管37的第一端连接电荷泵电路20的输出端,第一二极管37的第二端连接第一电阻31b的第一端,第一电阻31b的第二端接地。利用二极管的导通特性,分段功能无需程序控制,无需开关,节省面积。且控制电压大于第一二极管37的开关电压vth时,分流电路31才会接进环路,第一电阻31b才会对进行分流。控制电压小于二极管37的开关电压vth时,第一电阻31b不会参与到控制电压0-vth这一段的锁定过程,可以减小优化分流电路31对锁定时间的影响。

42.在图3所示分流电路的基础上,可以进一步增加二极管以及电阻的数量实现更有效的分段控制。

43.图5示出了环路滤波电路30和分流电路31的第三种电路结构。

44.如图5所示,分流电路31可以包括第四电阻38、第五电阻39、第一二极管37和第二二极管41。如图5所示,第一二极管37的第一端连接电荷泵电路20的输出端,第一二极管37的第二端连接第一电阻31c的第一端,第一电阻31c的第二端连接第四电阻38的第一端,第四电阻38的第二端接地,第二二极管41的第一端连接第一电阻31c的第二端,第二二极管41的第二端连接第五电阻39的第一端,第五电阻39的第二端接地。

45.第一二极管37、第一电阻31c和第四电阻38构成一通路,而第一二极管37、第一电阻31c、第二二极管41以及第五电阻39构成另一通路。本电路结构利用二极管的导通特性和电阻分压原理,分流电路31可根据控制电压自适应切换接入环路滤波电路30的接地电阻大小,也即上述两个通路的可以依据控制电压与第一二极管37和第二二极管41的开关电路vth之间的关系实现切换,进而实现分段功能,解决单个接地电阻有效作用范围有限,不能全频段优化小数杂散问题,提升产品性能。

46.通过第一二极管37可以控制整个分流电路31何时接入环路滤波电路30。第四电阻38和第五电阻39是接地电阻的组成部分,同时也其分压比例也控制第二二极管41何时导通接入环路滤波电路30,即:

47.例如,第一二极管37的开关电压为vth1,第二二极管41的开关电压vth2,控制电压为cv,第四电阻38的电阻为r4,第五电阻39的电阻为r5。

48.当cv《vth1时,分流电路31不接入环路滤波电路30。

49.当vth1《cv《(r4+r5)/r5*vth2+vth1时,第一二极管37+第一电阻31c+第四电阻38接入环路滤波电路30。

50.当cv》(r4+r5)/r5*vth2+vth1时,第一二极管37+第一电阻31c+第四电阻38+第二二极管41+第五电阻39接入环路滤波电路30。

51.由上述描述可知:本电路结构可以根据控制电压自适应地切换接入环路滤波电路30的分流电路31的阻值大小,而现有技术中大多是通过控制频率切换间接控制电压变化,而现有技术中当控制电压变化或偏移时,分流电路31无法切换或者无法及时切换,而分流电路31的优化效果与控制电压相关,此时优化效果必然打折扣。

52.通过设置本电路结构,每个分段都可选用小数杂散优化效果最好的阻值,从而扩大对小数杂散的优化范围,提升指标竞争力。

53.可选地,分流电路31还可以是由多个阻值固定的电阻进行并联、串联或者并联和串联的组合得到。分流电路31中的各个电阻可以有其各自的作用,例如有的可以具有过流保护作用,有的可以是各个电阻的组合减少电路发热现象等,这里不做限定。

54.可选地,分流电路31还可以是可变电阻器。可变电阻器的电阻可以根据需要设置,具体可以根据锁相环电路的电路参数、使用场景等设置好可变电阻器的阻值并固定在某一数值上。由于可变电阻器能够方便使用者进行设置,使得锁相环电路能够适应更多的应用场景。

55.可选地,分流电路31也可以是其他电路,该电路的等效电阻使得分流电路31依旧可对下放电荷进行分流。同时分流电路31可以实现一部分其他的功能,例如滤波和电路保护等作用。具体根据稳定性等需求进行设计。

56.可选地,环路滤波电路30的输出端电压到达预设电压,且环路滤波电路30的输出端电压保持恒定,流经分流电路31中的电流占流经电荷泵电路20的电流的5%以下。在本技术的另一实施例当中,流经分流电路31中的电流占流经电荷泵电路20的电流的5%以上时,电荷泵电路20会工作在追踪锁定的状态,锁相环电路也无法保持锁定状态,从而会导致一系列的负面影响。因此,本实施例中流经分流电路31中的电流占流经电荷泵电路20的电流的5%以下。

57.可选地,电荷泵电路20可以通过调整电荷泵的开关时间和电流大小来控制其输出的电荷量。从宏观角度来看,环路滤波电路30的等效电阻是固定的。为了使得环路滤波电路30的输出端电压稳定在某一数值上,电荷泵电路20所输出的电流也是固定的。分流电路31部分或者全部替代了电荷泵电路20的下放电荷泵的工作。同时,由于分流电路31本身所存在的电阻值,会对电路中的电流进行分流。流经分流电路31中的电流占流经电荷泵电路20的电流的5%以下,例如设置为流经电荷泵电路20的电流的1%。此时分流电路31对锁相环电路的锁定的影响较小,几乎可以忽略不计。上充电荷与下地电荷是电荷泵电路20中进行等效所使用的物理量,与电荷以及电荷的移动方向有关,并非实际的电流。而此处分流电路31对电路中的电流进行分流所涉及的“电流”为实际存在的电流,是由于分流电路两端的电势差而产生的实际存在的电流。

58.可选地,如图3所示,环路滤波电路30包括:第二电阻32、第三电阻33以及第一电容34、第二电容35、第三电容36;第一电容34的第一端连接电荷泵电路20的输出端,第一电容34的第二端接地,第二电阻32的第一端连接电荷泵电路20的输出端,第二电阻32的第二端连接第二电容35的第一端,第二电容35的第二端接地,第三电阻33的第一端连接电荷泵电路20的输出端,第三电阻33的第二端连接压控振荡器40的输入端,第三电容36的第一端连接第三电阻33的第二端,第三电容36的第二端接地。

59.(二)第二实施方式

60.如图6所示,第二实施方式和上述第一实施方式大致相同,主要不同在于:在第一实施方式中,分流电路31的第一端连接电荷泵电路20的输出端,也即连接环路滤波电路30的输入端,分流电路31的第二端接地。而在第二实施方式中,分流电路31的第一端连接环路滤波电路30的内部,分流电路31的第二端接地。

61.如图7所示,第二电阻32的第二端连接分流电路31的第一端,分流电路31的第二端接地,第三电阻33的第一端连接电荷泵电路20的输出端,第三电容36的第一端连接第三电阻33的第二端,第三电容36的第二端接地,分流电路31的第一端连接第二电阻32的第二端,分流电路31的第二端接地。例如,分流电路31可以包括第一电阻31d,第二电阻32的第二端连接第一电阻31d的第一端,第一电阻31d的第二端接地。

62.优化原理与前述第一实施例的优化小数杂散电路大致相同。在实际应用中,通过将分流电路31接入环路滤波电路30的内部,可以根据pcb板的需要灵活调整分流电路31的位置,使布局走线更顺畅。

63.环路滤波电路30是锁相环电路的重要组成单元,决定了锁相环电路的性能,是滤波器的一种。环路滤波电路30起到了维持环路稳定性、控制带内外噪声和杂散、防止压控振荡器40调谐电压突变的作用。环路滤波电路30可以滤除高频噪声。

64.由于环路滤波电路30是滤波器的一种,上述图1至图7实际上示出了增加了分流电路31的滤波器的电路结构,该滤波器包括环路滤波电路30和分流电路31。分流电路31的第一端连接环路滤波电路30,分流电路31的第二端接地。

65.图1至图5示出的滤波器的电路结构主要为:分流电路31的第一端可以连接环路滤波电路30的输入端,分流电路31的第二端接地。

66.环路滤波电路30可以包括第二电阻32、第三电阻33以及第一电容34、第二电容35、第三电容36以及分流电路31。第一电容34的第一端连接电荷泵电路20的输出端,第一电容34的第二端接地,第二电阻32的第一端连接电荷泵电路20的输出端,第二电阻32的第二端连接第二电容35的第一端,第二电容35的第二端接地,第三电阻33的第一端连接电荷泵电路20的输出端,第三电阻33的第二端连接压控振荡器40的输入端,第三电容36的第一端连接第三电阻33的第二端,第三电容36的第二端接地。分流电路31的第一端连接第一电容34的第一端,分流电路31的第二端接地。

67.关于分流电路31的具体结构可以参见上述第一实施方式以及图1至图5的描述,在此不再赘述。

68.图6和图7示出的滤波器的电路结构主要为分流电路31的第一端连接环路滤波电路30的内部,分流电路31的第二端接地。

69.环路滤波电路30可以包括第二电阻32、第三电阻33、第一电容34、第二电容35、第三电容36以及分流电路31的第一电阻31d。第一电容34的第一端连接电荷泵电路20的输出端,第一电容34的第二端接地,第二电阻32的第一端用于连接电荷泵电路20的输出端,第二电阻32的第二端连接第二电容35的第一端,第二电容35的第二端接地,第二电阻32的第二端连接分流电路31的第一端,分流电路31的第二端接地,第三电阻33的第一端连接电荷泵电路20的输出端,第三电容36的第一端连接第三电阻33的第二端,第三电容36的第二端接地。

70.本技术所提供的环路滤波电路30通过分流电路31进行分流,全部或者部分替代了

下放电荷泵的工作。当锁相环电路处于锁定状态时,锁相环电路的输出电压恒定,分流电路31调整流经环路滤波电路30的下地电荷的大小与上充电荷不完全相等。分流电路31在不改变分频比的情况下,打乱了电荷泵的输出,让电路锁定之后电荷泵电路20的输出不完全与分频器50的输出线性相关,从而能够减少小数杂散对锁相环电路输出信号的影响。电荷泵电路20的输出可以是电荷的上充和下放,电荷的上充和下放可以具有一定的频率和相位,且与分频器50的输出有一定的相关关系。

71.本技术还提供一种通讯设备,通讯设备包括频率生成模块;频率生成模块应用了前述的锁相环电路。该通讯设备能够产生高分辨率的信号,同时能够减弱小数杂散对信号的影响。

72.以上所述仅为本技术的实施方式,并非因此限制本技术的专利范围,凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1