电路板控深铣深度界测试结构的制作方法

1.本实用新型涉及电路板制造领域,特别涉及一种电路板控深铣深度界测试结构。

背景技术:

2.3oz以上属于厚铜板,当板件在有控深盲槽结构要求的情况下,制作盲槽目前基本上通过控深铣形成盲槽的做法。业内常规h(h指控深深度界限到不铣穿次层铜距离)最小距离能力为≥0.15mm;但h≥0.15mm时实际只适用于内层铜厚≤3oz的非厚铜板;而当内层铜厚>3oz时,由于内层填胶量大,板厚均匀性差,导致不同残铜率导致介质厚不一,计算理论h值与实际值不匹配,业内暂无明确定义内层铜厚>3oz时,h最小距离能力。如果按照目前行业较为通用的h≥0.15mm控制方法制作,此方法控制方法存在以下不足:(1)计算理论h值与实际值不匹配,控深铣深铣穿次层铜,导致开路风险;(2)计算理论h值与实际值不匹配,控深铣深层次铜外露,导致漏电风险。

技术实现要素:

3.本实用新型提供了一种电路板控深铣深度界测试结构,以解决至少一个上述技术问题。

4.为解决上述问题,作为本实用新型的一个方面,提供了一种电路板控深铣深度界测试结构,包括由上至下依次结合的用于形成第一测试控深铣盲槽的第一铜层、第一粘结层、第二铜层、第二粘结层、第三铜层、第三粘结层和用于形成第二测试控深铣盲槽的第四铜层,所述第二铜层上形成有多个残铜率不同的第一区域,所述第三铜层上形成有多个残铜率不同的第二区域,所述第一铜层、第二铜层、第三铜层、第四铜层的铜厚均为140um。

5.优选地,所述多个第一区域的残铜率分别为20%、30%、40%、50%、60%、70%、80%、90%。

6.优选地,所述多个第二区域的残铜率分别为20%、30%、40%、50%、60%、70%、80%、90%。

7.由于采用了上述技术方案,本实用新型不但可以反映内层铜厚>3oz时,h安全距离能力,而且还可以分别测试出内层不同残铜率对应h最小距离能力,从而给印制线路板设计提供有力依据。

附图说明

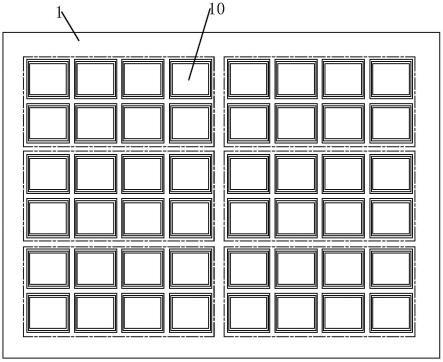

8.图1示意性地示出了第一铜层的示意图;

9.图2示意性地示出了本实用新型的截面图;

10.图3示意性地示出了第二铜层的示意图。

11.图中附图标记:1、第一铜层;2、第一粘结层;3、第二铜层;4、第二粘结层;5、第三铜层;6、第三粘结层;7、第四铜层;8、第一区域;9、第二区域;10、第一测试控深铣盲槽。

具体实施方式

12.以下对本实用新型的实施例进行详细说明,但是本实用新型可以由权利要求限定和覆盖的多种不同方式实施。

13.作为本实用新型的一个方面,提供了一种电路板控深铣深度界测试结构,包括由上至下依次结合的用于形成第一测试控深铣盲槽10的第一铜层1、第一粘结层2、第二铜层3、第二粘结层4、第三铜层5、第三粘结层6和用于形成第二测试控深铣盲槽的第四铜层7,所述第二铜层3上形成有多个残铜率不同的第一区域8,所述第三铜层5上形成有多个残铜率不同的第二区域9,所述第一铜层1、第二铜层3、第三铜层5、第四铜层7的铜厚均为140um。

14.优选地,所述多个第一区域8的残铜率分别为20%、30%、40%、50%、60%、70%、80%、90%。

15.优选地,所述多个第二区域的残铜率分别为20%、30%、40%、50%、60%、70%、80%、90%。

16.如图1所示,第一铜层的图形中分为六个模块(每个虚线框为一个模块,每个模块具有多个第一测试控深铣盲槽10)均为设计相同的电路图形,对应六种不同区域的控深深度情况。如图2所示,本实用新型由刚性pcb板形成,包括第一铜层1、第一粘结层2、第二铜层3、第二粘结层4、第三铜层5、第三粘结层6和第四铜层7,第一粘结层2、第三粘结层6由4张3313粘结材料层(1张粘结片厚度0.17mm)构成,图中h为控深深度界限到不铣穿次层铜距离,其中:六个模块的h设计理论值可分别为0.15mm、0.2mm、0.25mm、0.3mm、0.35mm、0.4mm。

17.如图3所示,其也分为6个模块,均为设计相同的电路图形,分别对应第一铜层的6个模块。单个模块的残铜率分别为20%、30%、40%、50%、60%、70%、80%、90%。

18.需要测试时,先形成本申请中的层叠结构,然后在第一铜层和第四铜层上进行控深铣,即可通过对各模块的观察,看出不同残铜率对应h最小距离能力之间关系,得出不同残铜率对应h最小距离能力。

19.由于采用了上述技术方案,本实用新型不但可以反映内层铜厚>3oz时,h安全距离能力,而且还可以分别测试出内层不同残铜率对应h最小距离能力,从而给印制线路板设计提供有力依据。

20.以上所述仅为本实用新型的优选实施例而已,并不用于限制本实用新型,对于本领域的技术人员来说,本实用新型可以有各种更改和变化。凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

技术特征:

1.一种电路板控深铣深度界测试结构,其特征在于,包括由上至下依次结合的用于形成第一测试控深铣盲槽(10)的第一铜层(1)、第一粘结层(2)、第二铜层(3)、第二粘结层(4)、第三铜层(5)、第三粘结层(6)和用于形成第二测试控深铣盲槽的第四铜层(7),所述第二铜层(3)上形成有多个残铜率不同的第一区域(8),所述第三铜层(5)上形成有多个残铜率不同的第二区域(9),所述第一铜层(1)、第二铜层(3)、第三铜层(5)、第四铜层(7)的铜厚均为140um。2.根据权利要求1所述的电路板控深铣深度界测试结构,其特征在于,所述多个第一区域(8)的残铜率分别为20%、30%、40%、50%、60%、70%、80%、90%。3.根据权利要求1所述的电路板控深铣深度界测试结构,其特征在于,所述多个第二区域的残铜率分别为20%、30%、40%、50%、60%、70%、80%、90%。

技术总结

本实用新型提供了一种电路板控深铣深度界测试结构,包括由上至下依次结合的用于形成第一测试控深铣盲槽的第一铜层、第一粘结层、第二铜层、第二粘结层、第三铜层、第三粘结层和用于形成第二测试控深铣盲槽的第四铜层,所述第二铜层上形成有多个残铜率不同的第一区域,所述第三铜层上形成有多个残铜率不同的第二区域,所述第一铜层、第二铜层、第三铜层、第四铜层的铜厚均为140um。实用新型不但可以反映内层铜厚>3OZ时,H安全距离能力,而且还可以分别测试出内层不同残铜率对应H最小距离能力,从而给印制线路板设计提供有力依据。从而给印制线路板设计提供有力依据。从而给印制线路板设计提供有力依据。

技术研发人员:王志明 李成 陈广 刘鑫 任平平

受保护的技术使用者:深圳市迅捷兴科技股份有限公司

技术研发日:2022.07.25

技术公布日:2023/1/6

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1