用于3D存储器的选择栅极结构及制造方法与流程

本公开内容的实施方式涉及电子器件的领域,及用于制造电子器件的方法及装置。更特定而言,本公开内容的实施方式提供漏极选择栅极(select-gate-for-drain;sgd)晶体管及其形成方法。

背景技术:

0、背景

1、半导体技术飞速进步,且器件尺寸已随着技术进步而缩小以提供每单位空间更快的处理及储存。在nand器件中,串电流需要足够高以获得足够电流来区分接通(on)及关断(off)单元。串电流取决于载流子迁移率,通过扩大硅沟道的晶粒大小来增强该载流子迁移率。

2、当前3d-nand器件在两个狭缝之间具有多个存储器孔,所述3d-nand器件具有包括氧化物材料及氮化物材料的交替层的存储器堆叠。为了由字线及位线访问每一单元,需要通过漏极选择栅极(sgd)切口来划分狭缝之间的存储器孔。举例而言,具有八个存储器孔及一个虚设孔的东芝96l堆叠3d nand具有一个sgd切口,其将所述孔分离成两组。为了减小3d-nand的阵列大小,需要增加狭缝之间的孔数(nhole)。若nhole增加8个孔以上,则对于相同技术而言,需要一个以上sgd切口。应可通过位线(bit line;bl)与字线(word line;wl)的组合单独地访问同一位线电平下的孔。换言之,通过漏极选择栅极(sgd)及位线独立地选择同一位线下的孔。出于此目的,应通过sgd切口使狭缝之间的sgd分离。当狭缝之间的孔数(nhole)小(例如,≤8)时,一个sgd切口将漏极选择栅极(sgd)分离开。然而,当狭缝之间的孔数(nhole)大(例如,≥12)时,每四个孔需要添加sgd切口。

3、因此,本领域需要一种具有漏极选择栅极(sgd)切口的3d-nand器件,及制造3d-nand器件的方法。

技术实现思路

0、概述

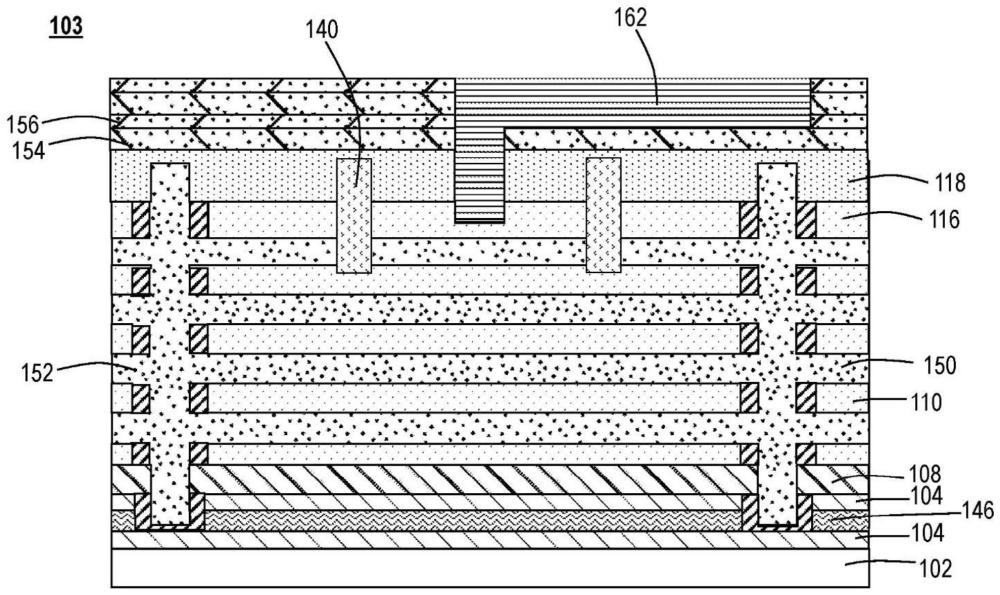

1、本公开内容的一个或多个实施方式涉及一种半导体存储器器件。在一个或多个实施方式中,一种半导体存储器器件包括:存储器阵列,其包括至少一个漏极选择栅极(sgd)晶体管及至少一个存储器晶体管,该存储器阵列具有至少一个搭接区域及至少一个搭接接触件,该搭接接触件将漏极选择栅极(sgd)晶体管连接至搭接线。

2、本公开内容的其他实施方式涉及一种半导体存储器器件。在一个或多个实施方式中,一种半导体存储器器件包括:在基板上的存储器堆叠,该存储器堆叠包括字线及介电材料的交替层;延伸经过存储器堆叠的多个存储器晶体管;经填充的狭缝,延伸经过存储器堆叠且与该多个存储器晶体管相邻;及在存储器堆叠的顶部部分中的多个漏极选择栅极(sgd)晶体管,其中该多个漏极选择栅极(sgd)晶体管中的至少一者电连接至搭接线。

3、本公开内容的额外实施方式涉及一种形成半导体器件的方法。在一个或多个实施方式中,一种形成半导体器件的方法包括:形成延伸经过存储器堆叠的多个存储器孔,该存储器堆叠包括在基板上的第一层及第二层的交替层;在该多个存储器孔中沉积晶体管层以形成多个存储器串;在该多个存储器串中的每一者的顶表面上形成位线衬垫;在存储器堆叠的顶部部分上形成漏极选择栅极(sgd)晶体管;形成延伸经过存储器堆叠至基板的狭缝;去除第一层以在存储器堆叠中形成开口;在该开口中沉积介电材料;使第二层凹陷以形成凹陷区域;在该凹陷区域中沉积低电阻率材料;填充该狭缝以形成经填充的狭缝;形成漏极选择栅极接触件;及在存储器堆叠的顶表面上形成搭接线,该搭接线接触该漏极选择栅极接触件。

技术特征:

1.一种半导体存储器器件,包括:

2.如权利要求1所述的半导体存储器器件,其中所述至少一个搭接区域包括第一多个存储器孔,所述第一多个存储器孔的密度小于非搭接区域中的第二多个存储器孔。

3.如权利要求1所述的半导体存储器器件,其中所述漏极选择栅极(sgd)晶体管包括多晶硅字线。

4.如权利要求1所述的半导体存储器器件,其中所述存储器晶体管包括第一材料及第二材料,所述第一材料具有比所述第二材料高的电阻。

5.如权利要求4所述的半导体存储器器件,其中所述第二材料与所述存储器阵列的狭缝区域相邻。

6.如权利要求1所述的半导体存储器器件,其中所述搭接线包括钨(w)、铝(al)、铜(cu)、钛(ti)、钽(ta)、钼(mo)及钌(ru)中的一者或多者。

7.一种半导体存储器器件,包括:

8.如权利要求7所述的半导体存储器器件,其中所述多个漏极选择栅极(sgd)晶体管中的每一者包括多晶硅字线。

9.如权利要求7所述的半导体存储器器件,其中所述多晶硅字线包括第一材料及第二材料,所述第一材料具有比所述第二材料高的电阻,所述第二材料与所述经填充的狭缝相邻。

10.如权利要求9所述的半导体存储器器件,其中所述第二材料包括钨(w)、钼(mo)、钛(ti)、铝(al)、钌(ru)、钽(ta)或上述的硅化物中的一者或多者。

11.如权利要求7所述的半导体存储器器件,其中所述多个存储器晶体管中的每一者包括选自氧化铝(alo)、阻挡氧化物、陷阱材料、穿隧氧化物及沟道材料的一个或多个晶体管层。

12.如权利要求7所述的半导体存储器器件,其中所述经填充的狭缝包括选自氧化硅、氮化硅及氮氧化硅中的一者或多者的绝缘体材料。

13.如权利要求7所述的半导体存储器器件,其中所述基板为公共源极线,所述公共源极线包括牺牲层、氧化物层及多晶硅层。

14.如权利要求7所述的半导体存储器器件,其中所述搭接线包括钨(w)、铝(a1)、铜(cu)、钛(ti)、钽(ta)、钼(mo)及钌(ru)中的一者或多者。

15.一种形成半导体器件的方法,所述方法包括以下步骤:

16.如权利要求15所述的方法,其中所述晶体管层包括氧化铝(a1o)层、阻挡氧化物层、陷阱层、穿隧氧化物层及沟道层中的一者或多者。

17.如权利要求15所述的方法,其中所述低电阻率材料包括钨(w)、钌(ru)、铝(a1)、铱(ir)、钽(ta)、钛(ti)、铂(pt)、钼(mo)、镍(ni)或上述的硅化物中的一者或多者。

18.如权利要求15所述的方法,其中所述经填充的狭缝包括选自氧化硅、氮化硅及氮氧化硅中的一者或多者的绝缘体材料。

19.如权利要求15所述的方法,其中所述基板为公共源极线,所述公共源极线包括牺牲层、氧化物层及多晶硅层。

20.如权利要求15所述的方法,其中所述搭接线包括钨(w)、铝(al)、铜(cu)、钛(ti)、钽(ta)、钼(mo)及钌(ru)中的一者或多者。

技术总结

描述一种半导体存储器器件及制造方法。半导体存储器器件包括存储器阵列,其包括至少一个漏极选择栅极(SGD)晶体管及至少一个存储器晶体管,该存储器阵列具有至少一个搭接区域及至少一个搭接接触件,搭接接触件将漏极选择栅极(SGD)晶体管连接至搭接线。

技术研发人员:姜昌锡,北岛知彦,李吉镛,姜声官

受保护的技术使用者:应用材料公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!