基于曲面绝缘栅堆垛结构的铁电存储器件及其制备方法

本发明属于fefet,具体涉及一种基于曲面绝缘栅堆垛结构的铁电存储器件及其制备方法。

背景技术:

1、氧化铪基铁电存储器由于具有非易失性、功耗低、抗辐射性能优异、与cmos工艺兼容等突出优点而被公认为新一代最具潜力的新型存储器之一。氧化铪基铁电场效应晶体管(fefet)是铁电存储器的基本存储单元,相对于传统的金属氧化物半导体场效应晶体管(mosfet),其在结构上除了用铁电薄膜取代线性栅介质之外,其它结构与传统的mosfet基本相同。

2、最初的fefet是基于mosfet结构将铁电薄膜(fe层)直接沉积在si衬底上,形成了金属-铁电薄膜-半导体硅(mfs)结构的mfs-铁电存储,但其弊端在于铁电层/半导体衬底之间存在严重的元素扩散污染。为了解决这一问题,研究者在铁电层与半导体衬底之间增添一层绝缘层,形成了金属-铁电薄膜-绝缘层-半导体(mfis)的mfis-铁电存储,有效避免了元素扩散导致的污染问题。但是该mfis栅结构引入了新的问题,在长期栅极电压作用下由于绝缘层与铁电层界面处能带发生弯曲使得电子(空穴)跃迁到导带(价带)的有效势垒宽度变窄,或是跃迁到邻近的缺陷能级上的几率变大,从而导致绝缘层隧穿电荷数量增加,最终导致器件经过1e4-1e6次擦写后发生击穿失效。

3、根据氧化铪基铁电存储的失效机理,即降低绝缘层的电场强度是关键。现有技术提出:(1)在绝缘层与铁电层之间加入金属层作为等势面,同时使铁电层/绝缘层面积比小于1,即设计金属-铁电层-金属-绝缘层-半导体(mfmis)栅结构。这种方法在维持铁电层极化强的同时,减缓极化导致的绝缘层的电场,以此改善器件的疲劳失效问题。(2)可以通过降低器件操作电压的方式,即降低铁电层的剩余极化强度。(3)通过外延方式调控氧化铪基铁电层的极化方向,使得垂直于沟道层表面方向的极化分量降低。(4)采用高介电常数绝缘层代替现有工艺中的氧化硅,使在同样极化强度作用下绝缘层的能带弯曲减缓。(5)增加绝缘层的厚度以抑制电子隧穿效应。

4、然而,上述技术存在以下问题:(1)铁电层和绝缘层面积不同的mfmis结构中,铁电层和绝缘层中加入一层金属层易增加器件漏电的概率,此外随着先进工艺节点的发展,该结构不利于栅堆垛结构的厚度微缩,并且mfmis-fet结构器件的制备工艺较为复杂,这也大大限制了其应用的前景。(2)降低器件的工作电压,尽管可以抑制疲劳失效,但同时降低了器件的存储窗口。(3)尽管高介电常数绝缘层在同等电压作用下能带弯曲减缓,但高介电材料的击穿电场通常低于氧化硅。如氧化硅的介电常数为3.9,击穿电场为10mv/cm,而非晶氧化铪的介电常数约为15,但击穿电场仅为5-6mv/cm。因此综合来看,器件的疲劳性能改善效果不佳。(4)增加绝缘层的厚度,但随之而来的器件工作电压也需要同步增大,一方面不利于低功耗器件的发展,另一方面由于工作电压增大,则绝缘层上的厚度也进一步增大,整体而言其电场的改变量十分有限。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种基于曲面绝缘栅堆垛结构的铁电存储器件及其制备方法。本发明要解决的技术问题通过以下技术方案实现:

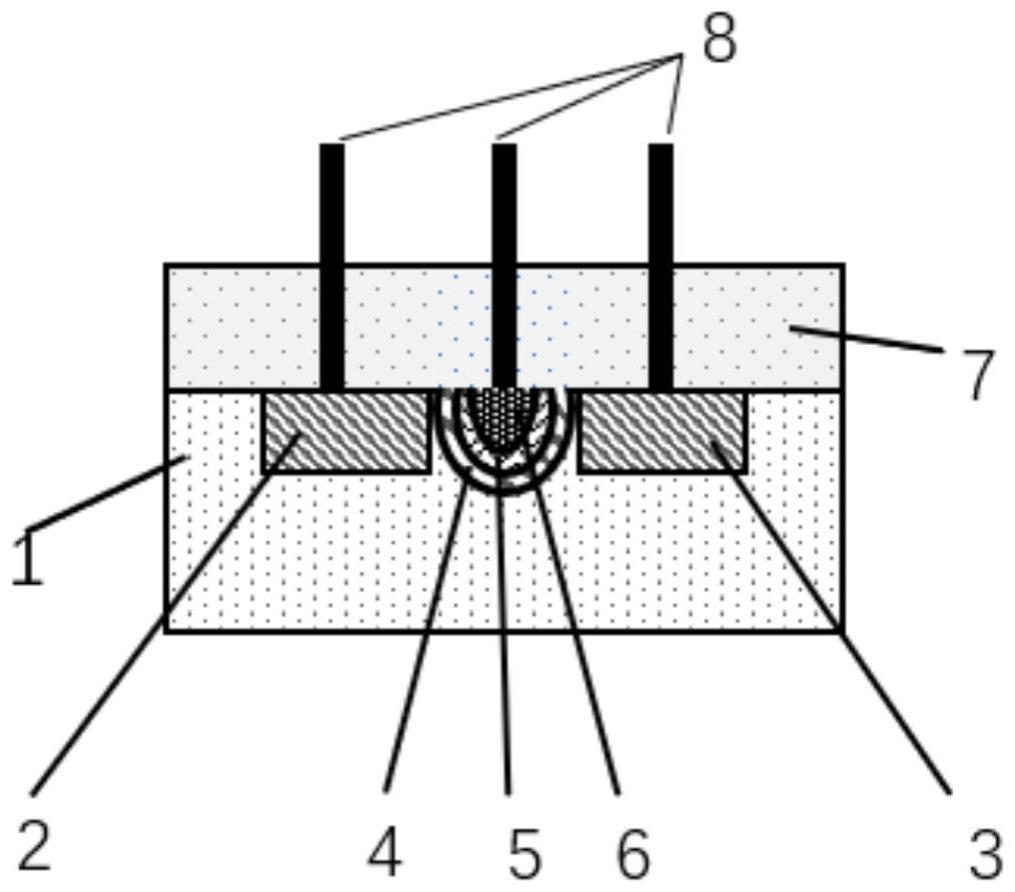

2、本发明提供了一种基于曲面绝缘栅堆垛结构的铁电存储器件,包括衬底、沟道层、源极、漏极以及曲面绝缘栅堆垛结构,其中,

3、所述沟道层位于所述衬底的上表面,所述源极和所述漏极分别嵌入在所述沟道层左右两侧,所述曲面绝缘栅堆垛结构设置在所述沟道层上表面且位于所述源极与所述漏极之间;

4、所述曲面绝缘栅堆垛结构包括凸状曲面和凹状曲面两种曲面类型,且所述凸状曲面和凹状曲面均包括自下而上依次堆叠的绝缘层、铁电层和栅极金属层,不同类型堆垛栅结构中绝缘层界面面积均大于铁电层界面面积。

5、在本发明的一个实施例中,当所述曲面绝缘栅堆垛结构为凹状曲面时,所述沟道层的上表面中心开设有一个球面凹槽;所述源极和所述漏极分别嵌入在所述沟道层上表面且位于所述球面凹槽左右两侧;

6、所述绝缘层、所述铁电层和所述栅极金属层自下而上依次设置在所述球面凹槽,并且所述绝缘层、所述铁电层和所述栅极金属层均呈凹面形状。

7、在本发明的一个实施例中,当所述曲面绝缘栅堆垛结构为凸状曲面时,所述曲面绝缘栅堆垛结构设置在所述沟道层上表面且位于所述源极与所述漏极之间;

8、所述曲面绝缘栅堆垛结构包括自下而上依次堆叠的绝缘层、铁电层和栅极金属层,并且所述绝缘层、所述铁电层和所述栅极金属层的表面均为凸面。

9、在本发明的一个实施例中,所述绝缘层的材料包括sio2、hfo2、zro2、la2o3、al2o3或ceo2,所述栅极金属层的材料包括al、cu、au、pt、w或tin,所述铁电层材料包括铁电氧化铪、铁电氧化锆、掺杂掺杂元素包括si、zr、sr、la、lu、gd、sc、nd、ga中一种或多种。

10、在本发明的一个实施例中,所述绝缘层的厚度为0.5nm-5nm;所述铁电层的厚度为5nm-50nm。

11、一种基于曲面绝缘栅堆垛结构的铁电存储器件的制备方法,所述曲面绝缘栅堆垛结构为凹状曲面,所述制备方法包括:

12、s1:选取衬底并清洗;

13、s2:在所述衬底上表面形成沟道层,在所述沟道层两侧形成源极区域和漏极区域;

14、s3:在所述源极区域与所述漏极区域之间的栅极区域沟道层上利用反应离子刻蚀基底表面形成凹槽;

15、s4:在所述沟道层上表面及所述凹槽内部自下而上依次堆叠生长绝缘层、铁电层和栅极金属层,形成多层薄膜结构;

16、s5:采用刻蚀技术刻蚀非凹槽区域的多层薄膜结构,形成凹槽内部的凹面栅结构;

17、s6:采用场氧法在所述沟道层和所述凹面栅结构上生长sio2场氧层;

18、s7:在所述源极区域和所述漏极区域上方的场氧层上刻蚀sio2层形成上下连通的通孔,并在所述通孔内部填充金属,以完成源极和漏极的制备。

19、在本发明的一个实施例中,所述s4包括:

20、s4.1:在所述沟道层表面及所述凹槽内部沉积形成厚度为0.5-5nm的绝缘层;

21、s4.2:利用薄膜沉积技术在所述绝缘层上沉积5-50nm厚度的铁电层,其中,沉积温度为室温-700°;

22、s4.3:在所述铁电层上表面沉积10-100nm厚的栅极金属层;

23、s4.4:退火,退火温度为300℃-1050℃,使所述铁电层完成结晶。

24、一种基于曲面绝缘栅堆垛结构的铁电存储器件的制备方法,所述曲面绝缘栅堆垛结构为凸状曲面,所述制备方法包括:

25、s1:选取衬底并清洗;

26、s2:对衬底进行处理,使其衬底表面为凸状结构;

27、s3:在衬底凸状结构上表面形成沟道层,在所述沟道层两侧形成源极区域和漏极区域;

28、s4:在所述沟道层表面自下而上依次堆叠生长绝缘层、铁电层和栅极金属层,所述绝缘层和所述铁电层表面分别为凸状结构;

29、s5:刻蚀非栅极区域的多层薄膜结构,形成栅堆垛结构,并对所述栅堆垛结构上表面进行不同程度刻蚀,使得铁电层的上表面面积小于绝缘层上表面面积,形成凸状绝缘栅堆垛结构;

30、s6:采用场氧法在所述衬底和所述凸状绝缘栅堆垛结构上生长sio2场氧层;

31、s7:在所述源极区域和所述漏极区域上方的场氧层刻蚀形成上下连通的通孔,并在所述通孔内部填充金属,以完成源极和漏极的制备。

32、在本发明的一个实施例中,所述s4包括:

33、s4.1:在所述衬底凸状结构上沉积形成厚度为0.5-5nm的绝缘层;

34、s4.2:利用薄膜沉积技术在所述绝缘层上沉积厚度为5-50nm的铁电层,其中,沉积温度为室温-700°;

35、s4.3:在所述铁电层上表面沉积10-100nm厚的栅极金属层;

36、s4.4:退火,退火温度为300℃-1050℃,使所述铁电层完成结晶。

37、与现有技术相比,本发明的有益效果有:

38、1.本发明利用曲面绝缘栅堆垛结构及其晶体管的设计来增强fefet的抗疲劳性性能。该结构可以通过调节铁电层和绝缘层实际承受栅极电压的有效面积比例,降低铁电层与绝缘层界面处铁电层偶极子的实际分布密度,减少绝缘层上单位面积承受的有效电场强度,可达到抑制循环电场作用下绝缘层中电子隧穿的目的,进而增强铁电存储器的抗疲劳性能,解决fefet器件由于反复擦写造成的存储窗口退化问题,可有效提升fefet器件的使用寿命。

39、2.本发明无需通过常规更换绝缘层材料或提高绝缘层厚度的方法即可抑制绝缘层因隧穿电流的产生而导致的fefet器件失效问题,避免了引入新绝缘层材料带来的元素污染问题和提升绝缘层厚度造成的功耗提升问题。

- 还没有人留言评论。精彩留言会获得点赞!