半导体装置及其制造方法与流程

本专利文档总体上涉及半导体技术,并且更具体地,涉及包括晶体管的半导体装置及其制造方法。

背景技术:

1、电子行业的持续发展需要逐渐小型化、性能更高、集成程度更高、运行速度更高的电子产品。为了满足这一要求,有必要开发能够保持和/或改善诸如晶体管的半导体装置的各种单元元件特性,同时减小元件的尺寸或占地面积的技术。

技术实现思路

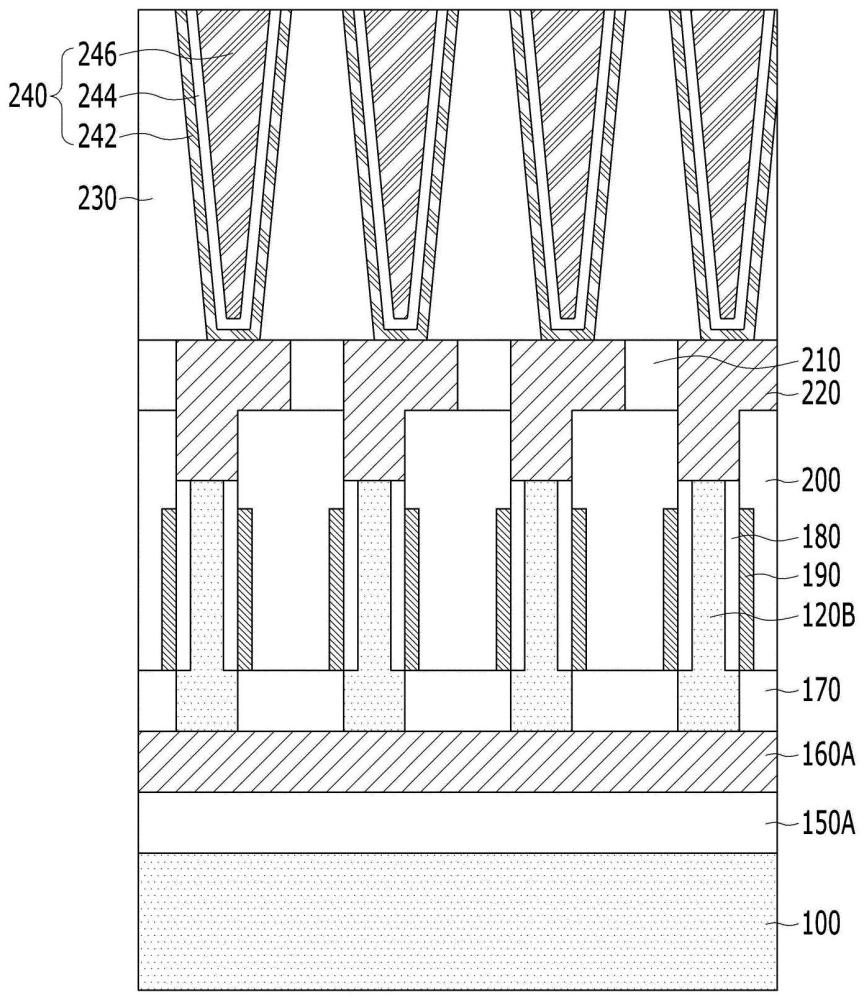

1、在一个实施例中,一种半导体装置可以包括:衬底;多个半导体柱,其设置在所述衬底之上并且布置在第一方向和与所述第一方向交叉的第二方向上;绝缘层图案,其设置在所述衬底与所述半导体柱之间并且在所述第二方向上延伸;第一导电线,其设置在所述绝缘层图案与所述半导体柱之间并且在所述第二方向上延伸;第二导电线,其形成在所述半导体柱的侧壁之上并且在所述第一方向上延伸;以及储存节点,其设置在所述半导体柱的每一个之上。

2、在另一个实施例中,一种用于制造半导体装置的方法可以包括:在衬底之上形成在第二方向上延伸的多个堆叠结构,所述堆叠结构的每一个包括牺牲层和设置在所述牺牲层之上的半导体层;通过选择性地刻蚀半导体层来形成布置在所述第二方向上和与所述第二方向交叉的第一方向上多个半导体柱;通过去除所述牺牲层来形成第一凹槽;形成填充所述第一凹槽的底部的绝缘层图案;形成填充形成有所述绝缘层图案的所述第一凹槽的剩余空间的第一导电线;在所述半导体柱的侧壁之上形成在所述第一方向上延伸的第二导电线;在所述半导体柱的每一个之上形成储存节点。

3、从所附附图和详细描述中,本发明的这些和其他的特征和优点对于本领域的技术人员来说将是显而易见的。

技术特征:

1.一种半导体装置,包括:

2.根据权利要求1所述的半导体装置,其中,所述第一导电线通过所述绝缘层图案而与所述衬底物理地且电气地分隔开。

3.根据权利要求1所述的半导体装置,其中,所述第一导电线的两个侧壁与所述绝缘层图案的两个侧壁在第一方向上对齐。

4.根据权利要求1所述的半导体装置,其中,所述半导体柱具有与所述衬底不同的材料或不同的晶体结构。

5.根据权利要求1所述的半导体装置,还包括:

6.根据权利要求1所述的半导体装置,还包括:

7.根据权利要求1所述的半导体装置,还包括:

8.根据权利要求1所述的半导体装置,其中,所述衬底包括单元区和外围电路区,以及

9.根据权利要求8所述的半导体装置,其中,所述外围半导体层图案的底表面位于与所述半导体柱的每一个的底表面相同的高度处,以及

10.根据权利要求8所述的半导体装置,其中,所述半导体柱和所述外围半导体层图案由相同的材料组成。

11.根据权利要求8所述的半导体装置,其中,所述外围半导体层图案通过所述绝缘层而与所述衬底物理地且电气地分隔开。

12.根据权利要求8所述的半导体装置,其中,所述绝缘层的底表面位于与所述绝缘层图案的底表面相同的高度处,以及

13.根据权利要求8所述的半导体装置,其中,所述绝缘层和所述绝缘层图案由相同的材料组成。

14.根据权利要求8所述的半导体装置,还包括:

15.一种用于制造半导体装置的方法,所述方法包括:

16.根据权利要求15所述的方法,其中,形成所述半导体柱是在硬掩模层被形成在所述堆叠结构之上的状态下进行的,所述硬掩模层在所述第一方向上延伸。

17.根据权利要求15所述的方法,其中,形成所述第二导电线是在形成通过覆盖所述第一导电线用于所述半导体柱的突出部分的绝缘材料的状态下进行的。

18.根据权利要求16所述的方法,其中,在所述储存节点形成之前,所述方法还包括:

19.根据权利要求18所述的方法,其中,所述第二孔的面积大于所述半导体柱的每一个的顶表面的面积。

20.根据权利要求15所述的方法,其中,所述牺牲层包括掺杂有杂质的半导体材料,以及

21.根据权利要求15所述的方法,其中,在形成所述第一凹槽之后或者在形成所述绝缘层图案之后,所述方法还包括:

22.根据权利要求15所述的方法,其中,在形成所述第一凹槽之后或者在形成所述绝缘层图案之后,所述方法还包括:

23.根据权利要求15所述的方法,其中,在形成所述第一凹槽之后或者在形成所述绝缘层图案之后,所述方法还包括:

24.根据权利要求15所述的方法,

25.根据权利要求24所述的方法,还包括:

技术总结

本发明涉及半导体装置及其制造方法。所述半导体装置可以包括:衬底;多个半导体柱,其设置在衬底之上并且布置在第一方向和与第一方向交叉的第二方向上;绝缘层图案,其设置在衬底与半导体柱之间并且在第二方向上延伸;第一导电线,其设置在绝缘层图案与半导体柱之间并且在第二方向上延伸;第二导电线,其形成在半导体柱的侧壁之上并且在第一方向上延伸;以及储存节点,其设置在半导体柱的每一个之上。

技术研发人员:金世渊

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/1/5

- 还没有人留言评论。精彩留言会获得点赞!