电平转换电路及DC/DC转换器、门极驱动器的制作方法

本发明涉及集成电路,尤其涉及一种电平转换电路及dc/dc转换器、门极驱动器。

背景技术:

1、对于dc/dc转换器,都需要用到电平转换电路。以降压转换器为例,高边开关一般是高压nmos,为了能使高边开关开通,一般会采用自举的方式,使高边的驱动电路工作在bst和sw的电压域中。同时因为控制逻辑是在vlv低压域中产生,所以这时候需要是用低到高的电平转换电路,把控制信号从vlv到地的域转换到bst到sw的域中。另外一方面,为了实现高低边开关的非交叠控制,需要对高边开关的开关状态进行检测,这时候就需要一个高到低的电平转换电路,将该信息返回到低压vlv电压域,从而可以进行之后的一系列的判断。

2、这种高到低或低到高的电平转换电路,需要满足以下要求:(1)因为sw是开关信号,所以在转换时会有很快的共模电平的变化,这样电平转换电路要避免误翻转;(2)因为电平转换电路是用在开关系统中,所以也需要提供较小的传输延迟;(3)相比一些靠边沿或者脉冲触发的转换电路,电平转换电路无法一直保持直流通路,。

3、现有的电平转换电路不能同时解决满足上述要求;(1)一些电平转换电路,抗共模干扰能力差,无法实现短的传输延迟;(2)一些电平转换电路,无法时刻保持有直流通路,会存在无法翻转或误翻转的问题。

技术实现思路

1、本发明提供一种电平转换电路及dc/dc转换器、门极驱动器,以解决现有技术中抗共模干扰能力差、无法实现短的传输延迟、无法时刻保持有直流通路的问题。

2、为解决上述技术问题,本发明是通过如下技术方案实现的:

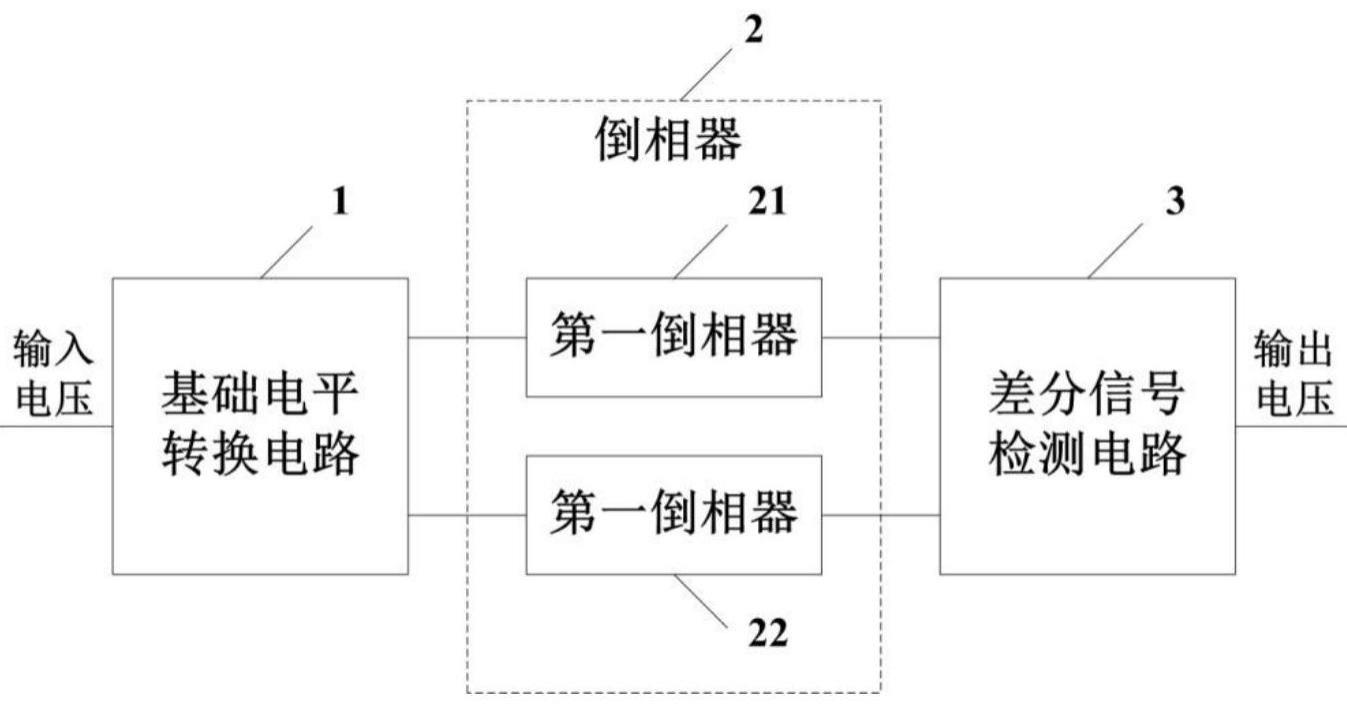

3、根据本发明的第一方面,提供一种电平转换电路,其包括:基础电平转换电路、倒相器、差分信号检测电路;其中,

4、所述基础电平转换电路的输出包括:第一输出、第二输出;

5、所述倒相器包括:第一倒相器、第二倒相器;

6、所述第一倒相器的输入端接所述基础电平转换电路的第一输出,所述第二倒相器的输入端接所述基础电平转换电路的第二输出;

7、所述差分信号检测电路的第一输入端、第二输入端分别接所述第一倒相器的输出端、所述第二倒相器的输出端,所述差分信号检测电路的一输出端的输出为输出电压;

8、所述输入电压位于第一电压域,所述输出电压位于第二电压域;

9、所述基础电平转换电路的第一输出被配置为:能够在所述第二电压域中提供对应的输出信号,所述基础电平转换电路的第二输出被配置为:能够在所述第二电压域中提供互补的输出信号;

10、所述差分信号检测电路被配置为:能够当检测到其第一输入端、第二输入端的输入信号电平不同时,对所述输出电压进行翻转。

11、较佳地,还包括:快速拉电路,所述快速拉电路的输入端连接所述倒相器、所述差分信号检测电路,所述快速拉电路的输出端包括两个:第一快速拉电路输出端、第二快速拉电路输出端,所述第一快速拉电路输出端直接或间接连接所述第一输出,所述第二快速拉电路输出端直接或间接连接所述第二输出。

12、较佳地,所述快速拉电路包括:逻辑门、第一快速拉晶体管、第二快速拉晶体管;

13、所述逻辑门的输入端作为所述快速拉电路的输入端,连接所述倒相器、所述差分信号检测电路;

14、所述逻辑门的输出包括两个:第一逻辑门输出、第二逻辑门输出;

15、所述第一快速拉晶体管的栅极连接所述第一逻辑门输出、所述第二快速拉晶体管的栅极连接所述第二逻辑门输出;

16、所述逻辑门被配置为:能够当所述输入电压发生变化时,控制所述第一快速拉晶体管导通或所述第二快速拉晶体管导通;

17、所述第一快速拉晶体管的漏极作为所述第一快速拉电路输出端,直接或间接连接所述第一电平转换电路的输出端;所述第二快速拉晶体管的漏极作为所述第二快速拉电路输出端,直接或间接连接所述第二电平转换电路的输出端。

18、较佳地,所述快速拉电路为快速上拉电路;

19、所述第一快速拉晶体管、所述第二快速拉晶体管为p型高压管;

20、所述第一快速拉晶体管的源极、所述第二快速拉晶体管的源极接所述第二电压域的高电平。

21、较佳地,所述快速拉电路为快速下拉电路;

22、所述第一快速拉晶体管、所述第二快速拉晶体管为n型高压管;

23、所述第一快速拉晶体管的源极、所述第二快速拉晶体管的源极接所述第一电压域的低电平。

24、较佳地,所述基础电平转换电路包括:第一电平转换电路、第二电平转换电路;

25、所述第一电平转换电路的输入与所述第二电平转换电路的输入互补;

26、所述第一电平转换电路的输出为所述第一输出,所述第二电平转换电路的输出为所述第二输出。

27、较佳地,所述第一电平转换电路包括:第一n型高压管、第一p型高压管、第一cmos管;

28、所述第二电平转换电路包括:第二n型高压管、第二p型高压管、第二cmos管;

29、所述第一n型高压管的栅极、所述第二n型高压管的栅极分别直接或间接接所述输入电压,所述第一n型高压管的栅极输入与所述第二n型高压管的栅极输入互补;

30、所述第一n型高压管的源极、所述第二n型高压管的源极接所述第一电压域的低电平;

31、所述第一n型高压管的漏极接所述第一p型高压管的漏极,所述第一p型高压管的栅极接所述第二电压域的低电平;所述第一p型高压管的源极接所述第一cmos管的漏极端,作为所述第一电平转换电路的输出端;

32、所述第一cmos管连接在所述第二电压域的高电平与所述第二电压域的低电平之间;

33、所述第二n型高压管的漏极接所述第二p型高压管的漏极,所述第二p型高压管的栅极接所述第二电压域的低电平;所述第二p型高压管的源极接所述第二cmos管的漏极端作为所述第二电平转换电路的输出端;

34、所述第二cmos管连接在所述第二电压域的高电平与所述第二电压域的低电平之间;

35、所述第一cmos管中的晶体管、所述第二cmos管中的晶体管为低压管。

36、较佳地,所述第一cmos管的栅极端反相连接所述第二倒相器的输出端;

37、所述第二cmos管的栅极端反相连接所述第一倒相器的输出端。

38、较佳地,所述第一电平转换电路包括:第三p型高压管、第三n型高压管、第三cmos管;

39、所述第二电平转换电路包括:第四p型高压管、第四n型高压管、第四cmos管;

40、所述第三p型高压管的栅极、所述第四p型高压管的栅极分别直接或间接接所述输入电压,所述第三p型高压管的栅极输入与所述第四p型高压管的栅极输入互补;

41、所述第三p型高压管的源极、所述第四p型高压管的源极接所述第二电压域的高电平;

42、所述第三p型高压管的漏极接所述第三n型高压管的栅极,所述第三n型高压管的栅极接所述第一电压域的高电平;所述第三n型高压管的漏极接所述第三cmos管的漏极端,作为所述第一电平转换电路的输出;

43、所述第三晶体管单元连接在所述第一电压域的高电平与所述第一电压域的低电平之间;

44、所述第四p型高压管的漏极接所述第四n型高压管的栅极,所述第四n型高压管的栅极接所述第一电压域的高电平;所述第四n型高压管的漏极接所述第四cmos管的漏极端,作为所述第二电平转换电路的输出;

45、所述第四晶体管单元连接在所述第一电压域的高电平与所述第一电压域的低电平之间。

46、较佳地,所述第三cmos管的栅极端反相连接所述第二倒相器的输出端;

47、所述第四cmos管的栅极端反相连接所述第一倒相器的输出端。

48、较佳地,所述差分信号检测电路包括:第一非门、第二非门、第一与非门、第二与非门、第三与非门、第四与非门;

49、所述第一非门的输入端接所述第一倒相器的输出端;所述第一与非门的一输入端接所述第一非门的输出端,所述第一与非门的另一输入端接所述第二非门的输出端;

50、所述第二非门的输入端接所述第二倒相器的输出端;所述第二与非门的一输入端接所述第二非门的输出端,所述第二与非门的另一输入端接所述第一非门的输出端;

51、所述第三与非门的一输入端接所述第一与非门的输出端,所述第三与非门的另一输入端接所述第四与非门的输出端;

52、所述第四与非门的一输入端接所述第二与非门的输出端,所述第四与非门的另一输入端接所述第三与非门的输出端;

53、所述第三与非门的输出端的输出为所述输出电压。

54、根据本发明的第二方面,提供一种dc/dc转换器,其包括:上述任一项所述的电平转换电路。

55、根据本发明的第三方面,提供一种门极驱动器,其包括:上述任一项所述的电平转换电路。

56、本发明提供的电平转换电路及dc/dc转换器、门极驱动器,通过倒相器选取不同的尺寸比例,可以调节第一输出和第二输出的翻转阈值,能够实现抗干扰和传输延迟性能上的折中,在抗干扰满足要求的基础上,还能减少传输延迟;通过差分信号检测电路,当第二电压域的低电平有共模电压变化导致其两输入信号同时发生变化时,其输出状态仍旧保持不变,这样就算有很大的共模电压变化,电平转换电路仍旧可以保持正确的输出状态,达到了更高的抗干扰能力。

57、本发明提供的电平转换电路及dc/dc转换器、门极驱动器,通过基础电平转换电路来实现电平转换,其时刻保持有直流通路,可以保证转换电路在任何工作环境下都会最终保持正确的输出状态。

58、本发明的一可选方案中,增加了快速拉电路电路,实现了在电平转换的过程中帮助基础电平转换电路快速上拉或快速下拉,进一步减小了电平转换电路的传输延迟。

59、本发明的一可选方案中,电平转换电路中的cmos管的栅极采用倒相器经过反相器后的输出进行驱动,增加了驱动能力,进一步减小了电平转换电路的传输延迟。

- 还没有人留言评论。精彩留言会获得点赞!