一种提升大信号响应速度的运算放大器的制作方法

本发明属于cmos工艺集成电路领域,具体涉及一种提升运算放大器大信号响应速度的方案。

背景技术:

1、运算放大器作为一个线性放大元器件,其需要工作在闭环状态形成负反馈电路而实现放大功能。运算放大器在工作的过程中,其输入端的信号通常都会从一个电压状态快速的转换为另一个电压状态,这个变动会导致运算放大器消耗一定的时间使得其输出电压从一个稳定状态转换为另一种稳定状态,其所消耗的时间定义为运算放大器的响应速度。响应速度越快,代表运算放大器处理信号的速度越快。

2、理想的运算放大器具有无限的响应速度,即输出电压信号不需要消耗任何时间来响应输入电压的变化。但实际运算放大器由于其带宽的有限性限制了其响应速度。而运算放大器的带宽由运算放大器的自身消耗的功耗以及电路本身的补偿电容和寄生电容决定,即运算放大器的自身功耗越大以及电路本身的补偿电容和寄生电容越小,运算放大器的带宽越大,其响应速度越快。但是运算放大器的本身功耗的增加会提升电路系统的功耗,运算放大器中寄生电容由工艺器件本身决定,运算放大器的补偿电容决定运算放大器的稳定性。

3、因此,对于一个给定设计参数的运算放大器,如何以一种结构简单的方案提升运算放大器的大信号响应速度的问题一直都是个难点。

技术实现思路

1、本发明的目的在于提供一种提升大信号响应速度的运算放大器,当运算放大器的两个输入端有较大的电压差时,响应速度提升电路会检测到该电压差,并通过给运算放大器中关键节点加入额外的电流来提升运算放大器的响应速度,从而极大的提升了运算放大器的大信号响应速度。

2、为了实现上述目的,本发明采用如下的技术方案:

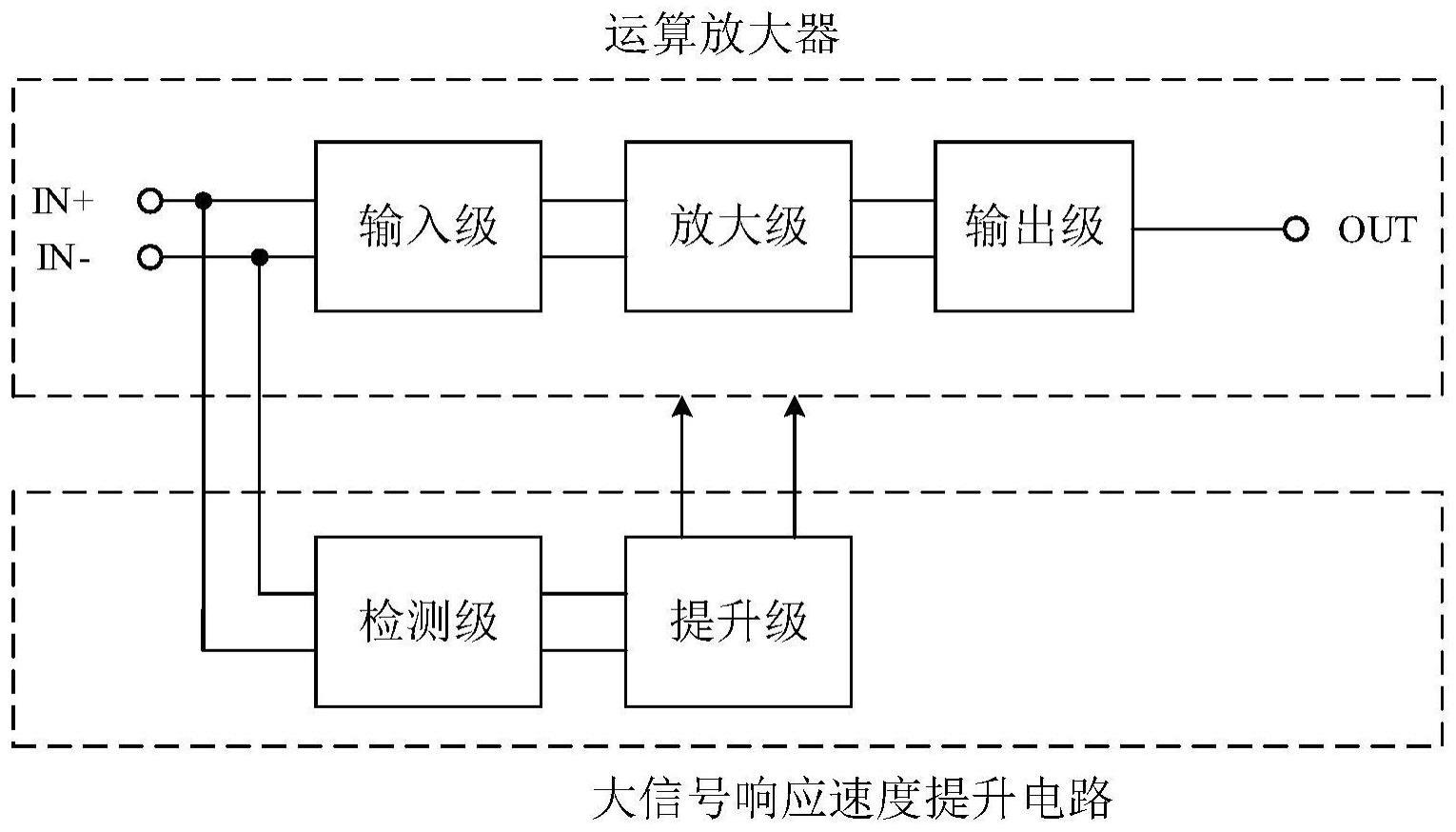

3、参见图1,一种提升大信号响应速度的运算放大器,包括输入级、放大级、输出级、检测级以及提升级。其中输入级、放大级以及输出级组成运算放大器的主体结构,检测级以及提升级构成大信号响应速度提升电路。运算放大器的正向输入端in+和负向输入端in-分别都与输入级和检测级相连,运算放大器通过输出级提供输出端out。其基本工作原理为:

4、检测级检测运算放大器的正向输入端in+和负向输入端in-的电压差,当电压差达到一定的值后,检测级控制提升级对运算放大器中影响大信号响应速度的电路中的关键节点进行电流的注入或拉出,从而提升运算放大器的大信号响应速度.

5、如图2所示,一种提升运算放大器大信号响应速度的电路,包括:输入级、放大级、输出级、pmos晶体管mp101、pmos晶体管mp102、pmos晶体管mp103、pmos晶体管mp104、pmos晶体管mp105、pmos晶体管mp106、nmos晶体管mn101、nmos晶体管mn102、nmos晶体管mn103、nmos晶体管mn104、nmos晶体管mn105、nmos晶体管mn106、nmos晶体管mn107、nmos晶体管mn108、nmos晶体管mn109、nmos晶体管mn110、电流源ib101、电流源ib102、电流源ib103、电流源ib104、电流源ib105、电流源ib106、电流源ib107、电流源ib108、电流源ib109、电流源ib110、反相器inv0、反相器inv1、反相器inv2以及反相器inv3。

6、输入级、放大级以及输出级组成传统的运算放大器电路,正向输入端in+和负向输入端in-接入输入级,输出级连接运算放大器的输出端out。

7、其中pmos晶体管mp101、pmos晶体管mp102、pmos晶体管mp103、pmos晶体管mp104、nmos晶体管mn101、nmos晶体管mn102、nmos晶体管mn103、nmos晶体管mn104、nmos晶体管mn105、nmos晶体管mn106、nmos晶体管mn107、nmos晶体管mn108、电流源ib101、电流源ib102、电流源ib103、电流源ib104、电流源ib105、电流源ib106、电流源ib107、电流源ib108、反相器inv0、反相器inv1、反相器inv2以及反相器inv3组成检测级。

8、进一步,pmos晶体管mp105、pmos晶体管mp106、nmos晶体管mn109、nmos晶体管mn110、电流源ib109以及电流源ib110组成了提升级。

9、pmos晶体管mp101的栅极连接运算放大器的正向输入端in+,pmos晶体管mp102的栅极连接运算放大器的负向输入端in-,pmos晶体管mp101的源极、pmos晶体管mp102的源极以及电流源ib101的一端电连接于一点,电流源ib101的另外一端与电源电压vdd相接,pmos晶体管mp101的漏极、nmos晶体管mn101的漏极、nmos晶体管mn101的栅极以及nmos晶体管mn102的栅极接于一点,pmos晶体管mp102的漏极、nmos晶体管mn102的漏极、nmos晶体管mn106的漏极、nmos晶体管mn106的栅极以及nmos晶体管mn105的源极接于一点,nmos晶体管mn101的源极与电流源ib103的一端相连,nmos晶体管mn102的源极与电流源ib104的一端相连,电流源ib103的另外一端、电流源ib104以及nmos晶体管mn104的源极的另外一端与gnd相连,nmos晶体管mn104的栅极、nmos晶体管mn104的漏极以及nmos晶体管mn103的源极连接于一点,nmos晶体管mn103的栅极、nmos晶体管mn103的漏极、nmos晶体管mn105的栅极以及电流源ib102的一端连接于一点,nmos晶体管mn105的漏极、pmos晶体管mp103的栅极、pmos晶体管mp103的漏极、pmos晶体管mp104的栅极以及电流源ib107的一端连接于一点,电流源ib102的另外一端、电流源ib107的另外一端、pmos晶体管mp103的源极以及pmos晶体管mp104的源极与电源电压vdd相连,nmos晶体管mn106的源极、nmos晶体管mn107的栅极、nmos晶体管mn107的漏极、nmos晶体管mn108的栅极以及电流源ib105的一端连接于一点,电流源ib105的另外一端、nmos晶体管mn107的源极以及nmos晶体管mn108的源极与gnd连接,pmos晶体管mp104的漏极、电流源ib106的一端以及反相器inv0的输入端连接于一点,电流源ib106的另外一端与gnd相连,nmos晶体管mn108的漏极、电流源ib108的一端以及反相器inv2的输入端连接于一点,电流源ib108的另外一端与电源电压vdd相连,反相器inv0的输出端、反相器inv1的输入端以及pmos晶体管mp105的栅极连接于一点,反相器inv2的输出端、反相器inv3的输入端以及nmos晶体管mn110的栅极连接于一点,反相器inv1的输出端和nmos晶体管mn109的栅极连接于一点,反相器inv3的输出端和pmos晶体管mp106的栅极连接于一点,pmos晶体管mp105的源极、pmos晶体管mp106的源极以及电流源ib109的一端连接于一点,电流源ib109的另外一端与电源电压vdd相连,nmos晶体管mn109的源极、nmos晶体管mn110的源极以及电流源ib110的一端连接于一点,电流源ib110的另外一端与gnd相连,pmos晶体管mp105的漏极输出电流信号ibd1,pmos晶体管mp106的漏极输出电流信号ibp1,nmos晶体管mn109的漏极输出电流信号ibd2,nmos晶体管mn110的漏极输出电流信号ibp2。

10、与现有技术相比,本发明具有以下有益效果:

11、1、本发明通过检测运算放大器两个输入端的压差,当运算放大器两个输入端的电压差较大时,提升级输出电流流入运算放大器输入级、放大级或者输出级关键节点处,从而增强运算放大器的大信号响应速度。

12、2、本发明通过检测运算放大器两个输入端的压差,当运算放大器两个输入端的电压差较小时,提升级不会输出电流到运算放大器输入级、放大级或者输出级,从而避免影响运算放大器稳定时的工作状态以及运算放大器的特性。

13、3、本发明的大信号响应提升的运算放大器电路具有结构简单、消耗功耗小以及面积小等特点。

- 还没有人留言评论。精彩留言会获得点赞!