半导体存储装置及其制造方法与流程

本实施方式涉及一种半导体存储装置及其制造方法。

背景技术:

1、nand(not and,与非)型闪速存储器等半导体存储装置有具备将存储单元三维地排列而成的立体型存储单元阵列的情况。如果在此种存储单元阵列的存储器孔内残留空隙或缝隙等空间,那么之后形成的源极层的金属材料进入到存储器孔内的空间,而使存储单元阵列的特性劣化。

技术实现思路

1、一个实施方式提供一种能够抑制存储单元阵列的特性的劣化的半导体存储装置及其制造方法。

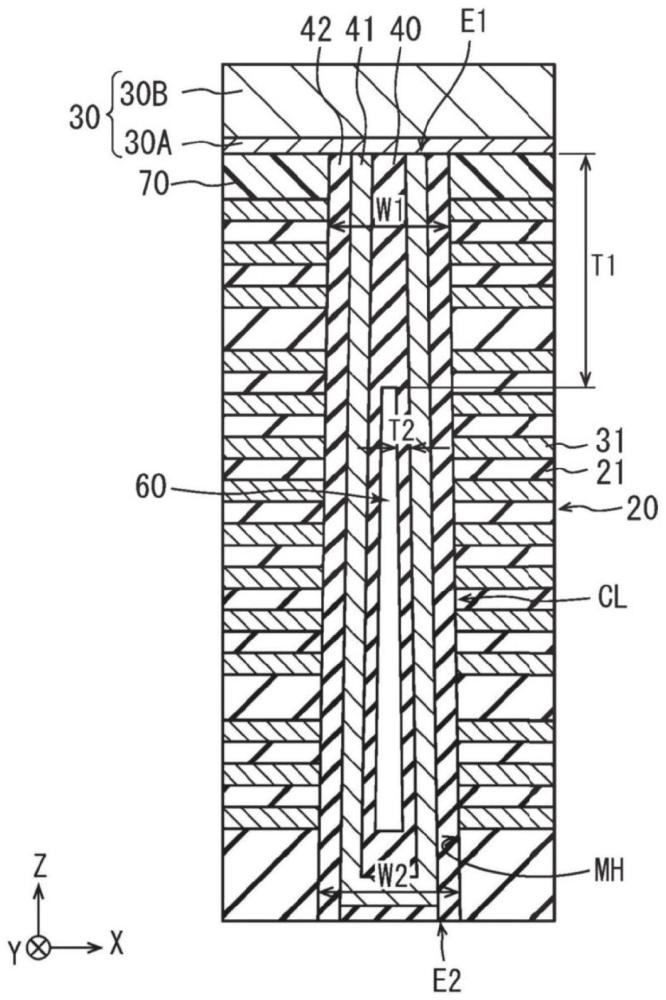

2、本实施方式的半导体存储装置具备将第1绝缘层与第1导电层在第1方向交替地积层而成的积层体。柱状体包含在积层体内在第1方向延伸的第1绝缘体部、设置在第1绝缘体部与积层体之间的第1半导体部、及设置在第1半导体部与积层体之间的第2绝缘体部、以及设置在第2绝缘体部与积层体之间的第3绝缘体部,且具有第1端部与处于该第1端部的相反侧的第2端部。第2导电层设置在积层体上,且在柱状体的第1端部电连接于第1半导体部。第1绝缘体部在柱状体的第1端部封闭第1半导体部的内侧,且在比第1端部接近第2端部的位置在第1半导体部的内侧具有空间。

3、根据所述构成,能够提供一种能够抑制存储单元阵列的特性的劣化的半导体存储装置及其制造方法。

技术特征:

1.一种半导体存储装置,具备:积层体,将第1绝缘层与第1导电层在第1方向交替地积层而成;柱状体,包含在所述积层体内在所述第1方向延伸的第1绝缘体部、设置在所述第1绝缘体部与所述积层体之间的第1半导体部、及设置在所述第1半导体部与所述积层体之间的第2绝缘体部、以及设置在所述第2绝缘体部与所述积层体之间的第3绝缘体部,且具有第1端部与处于该第1端部的相反侧的第2端部;以及第2导电层,设置在所述积层体上,且在所述柱状体的所述第1端部电连接于所述第1半导体部;所述第1绝缘体部在所述柱状体的所述第1端部封闭所述第1半导体部的内侧,在比所述第1端部接近所述第2端部的位置在所述第1半导体部的内侧具有空间。

2.根据权利要求1所述的半导体存储装置,其中所述积层体包含接近所述第2导电层的第1积层体、及比所述第1积层体与所述第2导电层相隔更远的第2积层体,所述柱状体包含在所述第1积层体内在所述第1方向延伸的第1柱状体、及在所述第2积层体内在所述第1方向延伸的第2柱状体,在所述第1积层体中所述第1柱状体内的所述第1绝缘体部在所述第1柱状体的所述第1端部封闭所述第1半导体部的内侧,在比所述第1端部接近所述第2端部的位置所述第1及第2柱状体的所述第1绝缘体部在其内部具有空间。

3.根据权利要求1所述的半导体存储装置,其中所述积层体包含接近所述第2导电层的第1积层体、及比所述第1积层体与所述第2导电层相隔更远的第2积层体,所述柱状体包含在所述第1积层体内在所述第1方向延伸的第1柱状体、及在所述第2积层体内在所述第1方向延伸的第2柱状体,在所述第1积层体中所述第1柱状体内的所述第1绝缘体部填充所述第1半导体部的内部,在所述第2积层体中所述第2柱状体的所述第1绝缘体部在其内侧具有空间。

4.根据权利要求1所述的半导体存储装置,其中所述第1方向的截面中的所述柱状体的宽度随着接近所述第2导电层而变小。

5.根据权利要求1所述的半导体存储装置,其中所述第1端部的所述第1绝缘体部的厚度,比所述空间的部分中的处于所述第1半导体部的内壁的所述第1绝缘体部的膜厚更厚。

6.根据权利要求1所述的半导体存储装置,其中所述积层体包含接近所述第2导电层的第1积层体、比所述第1积层体与所述第2导电层相隔更远的第2积层体、及比所述第2积层体与所述第2导电层相隔更远的第3积层体,所述柱状体包含在所述第1积层体内在所述第1方向延伸的第1柱状体、在所述第2积层体内在所述第1方向延伸的第2柱状体、及在所述第3积层体内在所述第1方向延伸的第3柱状体,在所述第1积层体中所述第1柱状体内的所述第1绝缘体部填充所述第1半导体部的内部,在所述第2积层体中所述第2柱状体内的所述第1绝缘体部在其内侧存在空间,在所述第3积层体中所述第3柱状体内的所述第1绝缘体部填充所述第1半导体部的内部。

7.根据权利要求1至6中任一项所述的半导体存储装置,其中所述第1绝缘体部在所述第1端部比所述第1半导体部更向所述第2端部侧凹陷而形成凹陷部,所述第2导电层埋入在所述凹陷部且连接于所述第1半导体部的内侧面。

8.根据权利要求2或6所述的半导体存储装置,其中所述第1积层体的所述第1绝缘体部与所述第2积层体的所述第1绝缘体部分离。

9.一种半导体存储装置的制造方法,具备以下步骤:

技术总结

本发明涉及一种半导体存储装置及其制造方法。本实施方式的半导体存储装置具备将第1绝缘层与第1导电层在第1方向交替地积层而成的积层体。柱状体包含在积层体内在第1方向延伸的第1绝缘体部、设置在第1绝缘体部与积层体之间的第1半导体部、及设置在第1半导体部与积层体之间的第2绝缘体部、以及设置在第2绝缘体部与积层体之间的第3绝缘体部,且具有第1端部与处于该第1端部的相反侧的第2端部。第2导电层设置在积层体上,且在柱状体的第1端部电连接于第1半导体部。第1绝缘体部在柱状体的第1端部封闭第1半导体部的内侧,且在比第1端部接近第2端部的位置在第1半导体部的内侧具有空间。

技术研发人员:滨田龙文,満野阳介,九鬼知博,森川雄介,増田亮二,佐藤弘康

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!