一种对高速模数转换器进行测试的系统及方法

本发明涉及集成电路测试领域,具体涉及一种能高效地、自动化地对高速模数转换器芯片进行测试的系统。

背景技术:

1、adc,全称为analog-to-digital converter,是一种能将模拟信号输入转换为数字信号输出的电子元件。它突破了模拟信号与数字信号相隔离的局限,使得模拟信号最终能够在数字领域进行处理、存储或者传输。高速adc芯片在诸多领域中有着广泛应用,如军工、航空航天、通信、医疗、工业控制等。随着无线通信、物联网和人工智能等技术的快速发展,通信和数据处理速度不断提升,对adc的采样速率和分辨率要求也越来越高,对高速adc芯片的需求也在不断增加。因而芯片测试行业也与时俱进地需要高速、高精度的adc芯片测试系统来满足要求。然而,对于高速adc芯片测试仍然是一个具有挑战性的任务,需要高精度、高速度和高可靠性的测试设备和测试方案。

2、高速信号处理方面:高速adc通常具有很高的采样率和宽带,测试时需要处理大量的高速信号。这对测试设备和测试算法提出了更高的要求,需要具备高速数据捕获和处理的能力。

3、信号完整性方面:高速adc的测试需要保证信号的完整性,避免信号失真和干扰。这对测试系统的设计和布局提出了挑战,需要考虑信号传输的阻抗匹配、信号线路的布线和屏蔽等因素。

4、高精度校准方面:高精度adc的测试需要进行准确的校准,以确保测试结果的准确性和可靠性。这包括对adc的增益、偏移、非线性等进行校准,需要使用高精度的校准设备和算法。

5、高效测试方面:高速和高精度adc的测试通常需要较长的测试时间和更高的测试成本。这是因为需要进行更多的采样和处理,并且需要使用更昂贵的测试设备和仪器。因此,如何在保证测试质量的前提下,提高测试效率和降低测试成本是一个挑战。

6、数据处理与分析方面:高速adc产生的数据量庞大,对数据处理和分析的能力提出了挑战。传统的数据处理方法可能无法处理如此大量的数据,需要采用高效的数据处理算法和技术,以确保数据能够被快速、准确地处理和分析。在某些应用场景下,高速adc的数据处理和分析需要具备实时性,即需要在数据产生后立即进行处理和分析,以满足实时监测和控制的要求。这对数据处理和分析的速度和效率提出了更高的要求。高速adc采集的数据可能存在噪声、失真等问题,需要进行数据校正和滤波等处理,以提高数据的准确性。这需要采用适当的算法和技术,以确保数据处理和分析的准确性和可靠性。

技术实现思路

1、针对现有技术中存在不足,本发明提供了一种对高速模数转换器芯片进行测试的系统,不仅可以对高速模数转换器芯片进行高精度、高速度和高可靠性测试,还能降低成本。

2、本发明是通过以下技术手段实现上述技术目的的。

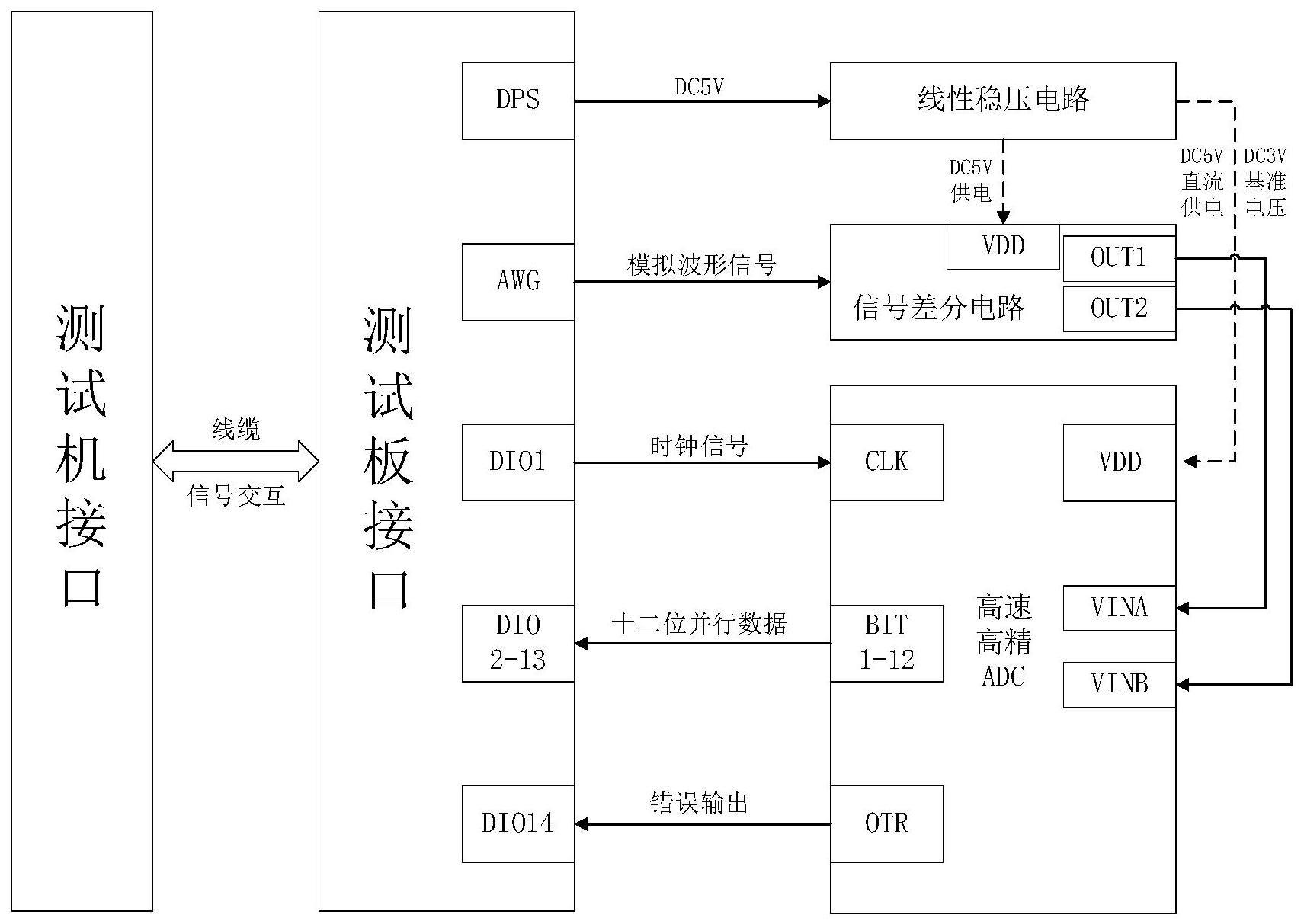

3、一种对高速模数转换器进行测试的系统,包括一种测试用电路板;所述测试用电路板包括电路板主体、元器件;所述电路板主体设有单元电路若干,包括相连接的接口模块、电源模块、单端转差分模块、待测芯片模块;

4、所述的接口模块,使用一个pin总数为96p,间距为2.54mm,行数为3,公母属性为母,安装方式为直插,额定电流为3a的板对板连接器,用于与测试机相连接,传输信号和进行供电;

5、所述的电源模块,采用dc-dc降压变换模式,包括一个dc5v转dc3v子电路模块、一个电源滤波子电路模块、一个电源指示灯子电路模块;其中,所述的dc5v转dc3v子电路模块采用低压差线性稳压器ldo;所述的电源滤波子电路模块采用电容滤波结构,多级电容相并联,用于吸收纹波,滤除不同频率的干扰信号;所述的电源指示灯子电路模块采用led与保护电阻相串联的结构,用于指示电源模块电路是否正常工作;所述电源模块的输入电压为dc5v,经过滤波后的输出电压分为两路:dc5v,用于给单端转差分模块和芯片模块供电;dc3v用于给待测芯片模块提供基准电压;

6、所述的单端转差分模块运用低失真差分adc驱动器作为主要元器件,单端信号经过电阻输入所述低失真差分adc驱动器的同相输入端,反相输入端通过一个电阻接地,参考电压输入端通过一个电容接地,两个差分输出端分别通过电阻与同相输入端和反相输入端相连;工作电压为dc5v,-3db带宽为320mhz(g=+1),压摆率为1150v/μs,可以在较高频率条件下驱动最新型的10位至16位转换器,用于在单端输入信号条件下提供一对两路差分输出,来平衡差分adc的输入,使adc性能达到较高;

7、所述的待测芯片模块,包括一个可快速装卸qfp48封装芯片的芯片座和一个电阻、电容基本电路;所述电阻、电容基本电路包括:待测芯片时钟输入引脚通过隔离电阻与外部输入时钟信号相连,输出使能引脚通过一个电阻接地,超出范围输出引脚通过一个隔离电阻输出信号,参考输入/输出引脚通过一个电容接地,降噪引脚通过一个电容组接地;待测芯片模块的工作电压为dc5v,需要dc3v的基准电压,所述的电阻、电容基本电路用于支持高速模数转换器正常工作。

8、本发明的一种对高速模数转换器进行测试的方法,用于支持测试机通过测试用电路板对高速模数转换器芯片进行测试,以验证其功能性是否正常;具体为:

9、基于c++编程语言设计,根据测试项目大致分为5个阶段,包括系统启动及初始化程序阶段、系统复位程序阶段、osn测试阶段、adc静态测试阶段和adc动态测试阶段,程序具有普遍性,兼容不同管脚数和不同种类型的高速模数转换器芯片。

10、进一步,系统启动及初始化程序段和系统复位程序段,其特征在于,系统启动及初始化程序段在整个测试过程开始前执行一次,系统复位程序段在每个测量结束时执行。

11、进一步,所述的osn测试,首先把包括电源引脚在内的所有引脚接地,其次对所述被测引脚施加一个大小为100ua、方向为从待测芯片流出的电流,再次测量采集导通压降,最后分析导通压降数值来分析判断所述被测引脚的开短路状态。

12、5.根据权利要求2所述的方法,其特征在于,所述的adc静态测试,首先对单端转差分模块单元电路输入斜波,其次将经过转化后的双路差分信号输入给待测芯片,再次采集adc转换后输出的数字信号,最后通过数据的后处理计算得到相应的具体静态参数值,与芯片数据手册相对比,得到测试结果。

13、进一步,所述的adc动态测试,首先对单端转差分模块单元电路输入正弦波,其次将经过转化后的双路差分信号输入给待测芯片,再次采集adc转换后输出的数字信号,然后对采集到的数字信号进行快速傅里叶变换,最后处理计算得到相应的具体动态参数值,与芯片数据手册相对比得到测试结果。

14、本发明的有益效果为:

15、(1)本发明成功地对高速模数转换器芯片进行了性能参数测试,能够得到正确、规范的测试结果。

16、(2)本发明集成了数字、模拟混合信号测试功能,支持125mhz采样时钟频率,250mbps速率数据传输,确保对高速模数转换器进行测试过程中数据的完整性和可靠性。

技术特征:

1.一种对高速模数转换器进行测试的系统,其特征在于,包括一种测试用电路板;所述测试用电路板包括电路板主体、元器件;所述电路板主体设有单元电路若干,包括相连接的接口模块、电源模块、单端转差分模块、待测芯片模块;

2.一种对高速模数转换器进行测试的方法,其特征在于,用于支持测试机通过测试用电路板对高速模数转换器芯片进行测试,以验证其功能性是否正常;具体为:

3.根据权利要求2所述的方法,其特征在于,系统启动及初始化程序段和系统复位程序段,其特征在于,系统启动及初始化程序段在整个测试过程开始前执行一次,系统复位程序段在每个测量结束时执行。

4.根据权利要求2所述的方法,其特征在于,所述的osn测试,首先把包括电源引脚在内的所有引脚接地,其次对所述被测引脚施加一个大小为100ua、方向为从待测芯片流出的电流,再次测量采集导通压降,最后分析导通压降数值来分析判断所述被测引脚的开短路状态。

5.根据权利要求2所述的方法,其特征在于,所述的adc静态测试,首先对单端转差分模块单元电路输入斜波,其次将经过转化后的双路差分信号输入给待测芯片,再次采集adc转换后输出的数字信号,最后通过数据的后处理计算得到相应的具体静态参数值,与芯片数据手册相对比,得到测试结果。

6.根据权利要求2所述的方法,其特征在于,所述的adc动态测试,首先对单端转差分模块单元电路输入正弦波,其次将经过转化后的双路差分信号输入给待测芯片,再次采集adc转换后输出的数字信号,然后对采集到的数字信号进行快速傅里叶变换,最后处理计算得到相应的具体动态参数值,与芯片数据手册相对比得到测试结果。

技术总结

本申请提供一种对高速模数转换器进行测试的系统及方法,所述高速模数转换器芯片测试系统包括一种测试用电路板和一种测试流程方法;所述测试用电路板作为高速模数转换器芯片的测试搭载平台,为待测芯片提供基本外围工作电路,并将其与测试机相连接,完成硬件设置;所述测试流程方法基于C++编程语言设计,用于对高速模数转换器芯片进行OSN测试、ADC静态测试和ADC动态测试等。基于上述测试系统,本申请实施例对高速模数转换器芯片进行了测试,在保证高精度、高速度、高准确性的同时降低了测试成本,简化了测试步骤。

技术研发人员:白雪,徐雷钧,陶长恒,杨旸,舒鹏

受保护的技术使用者:江苏大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!