应用于电流读出的运放失调修正方法及电路

本发明涉及一种应用于电流读出的运放失调修正方法及电路,属于集成电路。

背景技术:

1、在传感器、存算一体芯片等领域,其芯片系统通常由器件阵列及外围电路组成,随着对系统精度的要求不断提高,其对模拟信号处理电路的精度要求也在不断提高,模拟信号处理电路作为器件阵列的重要外围电路之一,起着将器件的输出信号传送至后级电路的作用。其中,电流读出电路作为模拟信号处理电路的重要模块起到将器件阵列的输出信号完成信号转换的作用。

2、在现有技术中,有如图1所示的电流读出电路,由运算放大器及调整管组成(cn101256167a),该结构利用理想运算放大器的“虚短”、“虚断”特性,将器件端电压vcell钳位至运算放大器的同相输入端电压vref,但对于实际运算放大器而言,由于制造工艺的不确定性和封装后的机械压力存在着失调电压vos,即由实际运算放大器组成的钳位电路,其钳位电压为:

3、vcell=vos+vref

4、通常vos的量级为mv级,目前运算放大器的失调电压消除有两种常用的技术:自动调零技术(cn113872542a)及斩波调制技术(cn217363034u),这两种技术适用于运算放大器开环工作状态,且电路结构或时序复杂,不适用于电流读出电路。

5、综上,现有结构的电流读出电路失调电压误差较大,现有运算放大器的失调修正方法不适用于电流读出电路,需要一种应用于电流读出电路的运放失调修正电路。

技术实现思路

1、为了修正电流读出电路中运算放大器的失调电压,本发明提供了一种应用于电流读出的运放失调修正方法及电路,所述技术方案如下:

2、本发明的第一个目的在于提供一种应用于电流读出的运放失调修正电路,包括运算放大器模块、失调补偿模块及mos调整管;

3、所述运算放大器模块和mos调整管连接,用于钳位器件端电压,所述失调补偿模块基于电容电荷守恒特性,补偿运算放大器的失调电压。

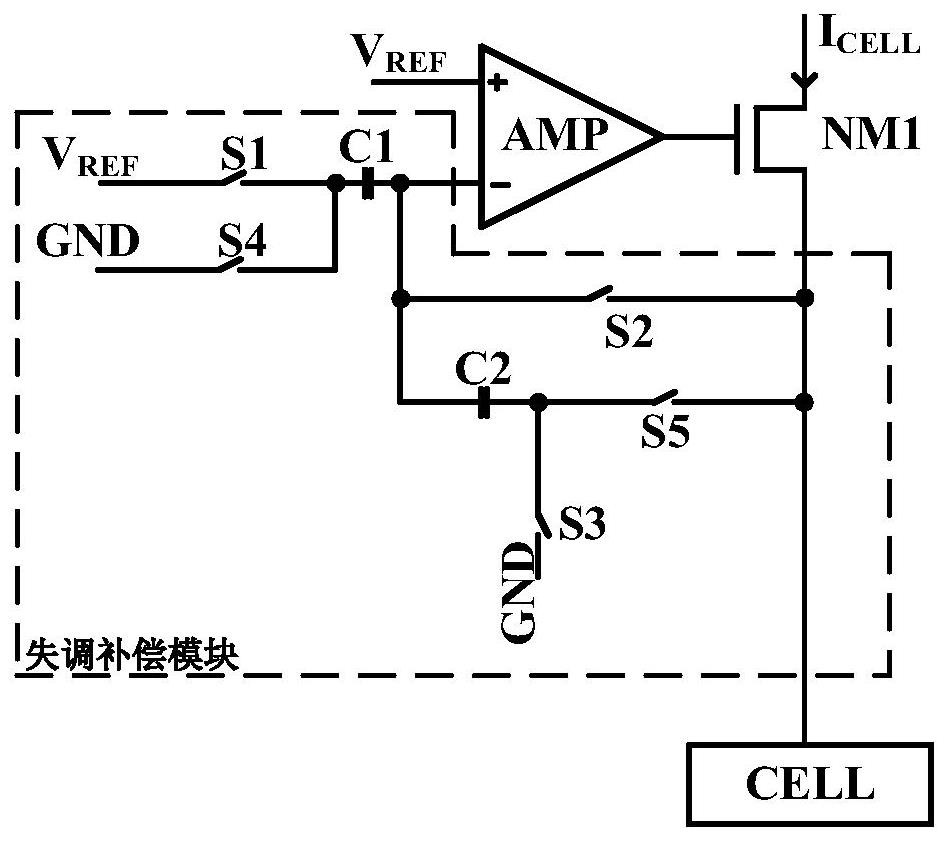

4、可选的,所述失调补偿模块包括:第一开关s1、第二开关s2、第三开关s3、第四开关s4、第五开关s5、第一电容c1、第二电容c2;

5、所述第一开关s1一端与参考电压vref连接,另一端通过所述第一电容c1与所述运算放大器的负输入端连接;所述第二开关s2一端与所述第一电容c1、所述运算放大器的负输入端连接,另一端与所述mos调整管的源端连接;所述第三开关s3的一端与所述第二电容c2连接,另一端接地;所述第四开关s4一端与所述第一电容c1连接,另一端接地;所述第五开关s5一端与所述第二电容c2连接,另一端与所述mos调整管的源端连接;

6、所述第一电容c1一端分别与所述第一开关s1、第四开关s4连接,另一端分别与所述运算放大器的负输入端、第二开关s2、第二电容c2连接;所述第二电容c2一端与所述第一电容c1连接,另一端分别与所述第三开关s3、第五开关s5连接。

7、可选的,所述运算放大器模块包括运算放大器amp,所述mos调整管采用nmos管或pmos管。

8、可选的,所述应用于电流读出的运放失调修正电路还包括:第一pmos管pm1、第二pmos管pm2、第三pmos管pm3、第四pmos管pm4;

9、所述第一pmos管pm1、第二pmos管pm2的源极均连接电源电压vdd,漏端分别连接所述第三pmos管pm3、第四pmos管pm4的漏端,栅端连接所述mos调整管的漏端;所述第三pmos管pm3、第四pmos管pm4的栅端连接偏置电压vb,所述第三pmos管pm3的漏端连接所述mos调整管的漏端;所述mos调整管的栅端连接所述运算放大器amp的输出端,源端连接存算单元。

10、可选的,所述应用于电流读出的运放失调修正电路还包括:第一pmos管pm1、第二pmos管pm2;

11、所述第一pmos管pm1、第二pmos管pm2的源极均连接电源电压vdd,所述第一pmos管pm1漏端、栅端、所述第二pmos管pm2的栅端连接所述mos调整管的漏端,所述mos调整管的栅端连接所述运算放大器amp的输出端,源端连接传感器系统的输出。

12、本发明的第二个目的在于提供一种应用于电流读出的运放失调修正方法,采用上述的应用于电流读出的运放失调修正电路进行器件端电压的钳位,钳位过程包括:

13、t1阶段:所述第一开关s1、第二开关s2、第三开关s3、第四开关s4、第五开关s5断开;

14、t2阶段:所述第一开关s1、第二开关s2、第三开关s3闭合,所述第四开关s4、第五开关s5断开,所述运算放大器的失调电压存储在电容极板上;

15、t3阶段:所述第四开关s4、第五开关s5闭合,所述第一开关s1、第二开关s2、第三开关s3断开,利用电容电荷守恒特性减小所述运算放大器失调电压对钳位电压的影响。

16、可选的,所述t2阶段电容存储电荷量表达式如下:

17、q1=c1*(vref-vref-vos)+c2*(0-vref-vos)

18、其中,q1表示t2阶段电容电荷存储量,c1、c2表示电容且容值相等,vref表示参考电压,vos表示运算放大器的失调电压。

19、可选的,所述t3阶段电容存储电荷量表达式如下:

20、q2=c1*(0-vref-vos)+c2*(vbl-vref-vos)

21、其中,q2表示t3阶段电容电荷存储量,vbl表示存算单元端电压;

22、由于电荷守恒,有如下表达式:

23、q1=q2

24、代入化简得:

25、vbl=vref

26、从而减小运算放大器的失调电压对于存算单元的电流读出误差影响。

27、本发明的第三个目的在于提供一种存算系统,包括存算单元,采用上述的运放失调修正电路对所述存算单元的输出电压进行钳位及输出电流读出。

28、本发明的第四个目的在于提供一种传感系统,包括传感器,采用上述的运放失调修正电路对所述传感器的输出电压进行钳位及输出电流读出。

29、本发明有益效果是:

30、本发明通过运算放大器及mos调整管使得钳位电压不受器件输出信号变化的影响,通过失调补偿模块减小非理想因素给电流读出电路带来的误差,利用电容电荷守恒特性减小运算放大器失调电压对钳位电压的影响,电路结构简单易实现,面积开销低,开关时序简单。

31、实验结果证明,本发明的应用于电流读出的运放失调修正电路在增加很小的电路面积前提下,极大地提升了电流读出电路的精度。

技术特征:

1.一种应用于电流读出的运放失调修正电路,其特征在于,所述运放失调修正电路包括运算放大器模块、失调补偿模块及mos调整管;

2.根据权利要求1所述的运放失调修正电路,其特征在于,所述失调补偿模块包括:第一开关(s1)、第二开关(s2)、第三开关(s3)、第四开关(s4)、第五开关(s5)、第一电容(c1)、第二电容(c2);

3.根据权利要求2所述的运放失调修正电路,其特征在于,所述运算放大器模块包括运算放大器(amp),所述mos调整管采用nmos管或pmos管。

4.根据权利要求3所述的运放失调修正电路,用于存算系统,其特征在于,所述运放失调修正电路还包括:第一pmos管(pm1)、第二pmos管(pm2)、第三pmos管(pm3)、第四pmos管(pm4);

5.根据权利要求3所述的运放失调修正电路,用于传感器系统,其特征在于,所述运放失调修正电路还包括:第一pmos管(pm1)、第二pmos管(pm2);

6.一种应用于电流读出的运放失调修正方法,其特征在于,所述方法采用权利要求3-5任一项所述的运放失调修正电路的进行器件端电压的钳位,钳位过程包括:

7.根据权利要求6所述的运放失调修正方法,其特征在于,所述t2阶段电容存储电荷量表达式如下:

8.根据权利要求7所述的运放失调修正方法,其特征在于,所述t3阶段电容存储电荷量表达式如下:

9.一种存算系统,包括存算单元,其特征在于,所述存算系统采用权利要求4所述的运放失调修正电路对所述存算单元的输出电压进行钳位及输出电流读出。

10.一种传感系统,包括传感器,其特征在于,所述传感系统采用权利要求5所述的运放失调修正电路对所述传感器的输出电压进行钳位及输出电流读出。

技术总结

本发明公开了一种应用于电流读出的运放失调修正方法及电路,属于集成电路技术领域。本发明的电路包括运算放大器模块、失调补偿模块及MOS调整管;运算放大器模块和MOS调整管连接,用于钳位器件端电压,失调补偿模块利用电容电荷守恒特性,补偿运算放大器的失调电压。本发明通过运算放大器及MOS调整管使得钳位电压不受器件输出信号变化的影响,通过失调补偿模块减小非理想因素给钳位电路带来的误差,利用电容电荷守恒特性减小运算放大器失调电压对钳位电压的影响,电路结构简单易实现,面积开销低,开关时序简单。实验结果证明,本发明的应用于电流读出的运放失调修正电路在增加较小的电路面积前提下,极大地提升了电流读出电路的精度。

技术研发人员:虞致国,高点点,顾晓峰

受保护的技术使用者:江南大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!