一种用于流水线型模数转换器的差分时钟接收电路

本发明属于集成电路领域,具体涉及一种用于流水线型模数转换器的差分时钟接收电路。

背景技术:

1、高速高精度流水线型模数转换器,采样过程需要满足奈奎斯特采样定律,暨采样频率需要为输入频率的两倍,故采样过程往往需要很高的采样率,因而需要高频率高质量的时钟信号。然而时钟信号在接收过程中除了传输通道造成的信号失真,还会由于接收电路的自身结构面临信号串扰、反射、阻抗失配和损耗等非理想问题,不可避免地引入时钟信号相位噪声和时钟抖动,使得时钟信号完整性受到影响,这种影响随着时钟频率的不断增加而越发明显。由外部干扰或内部噪声的影响而发生的时钟抖动,使得时钟信号不稳定,而时钟信号的不稳定,会导致模数转换器的采样周期出现抖动,造成采样周期的不确定性,严重影响采样模块结构的准确性,进而对整体模数转换精度产生直接影响,甚至使整体电路的工作,尤其数字电路模块,出现无法避免的时序问题。当输入信号频率较高时,为保持整体的信噪比不下降,就需要更小时钟抖动的时钟信号,这对时钟接收模块以及后续对时钟的传输提出了更高的要求。

2、相关技术中,接收高速时钟信号的方案主要包括两种:一种是传统的高速全差分接收电路,另一种是在差分接收端采用简单的差分对输入结构的运算放大器,后续再通过复杂且面积大的占空比校正模块进行时钟信号的校准。然而,前一种现有方案中,电路本身引入的噪声无法避免,这一问题在高速时钟应用场景下尤为突出,因此如果模数转换器需要保证具有足够的精度,就需要复杂的占空比调制电路,然而复杂的占空比调制电路将不可避免地使电路整体面积和功耗的增大。第二种现有方案中,在进行高速低电压域设计时,会受到电源纹波的影响,使得时钟在校准过程中再次引入噪声。

3、因此,如何在接收高速时钟信号时保持其信号的完整性的同时降低时钟抖动,是一项亟待解决的技术问题。

技术实现思路

1、为了解决现有技术中所存在的上述问题,本发明提供了一种用于流水线型模数转换器的差分时钟接收电路。

2、本发明要解决的技术问题通过以下技术方案实现:

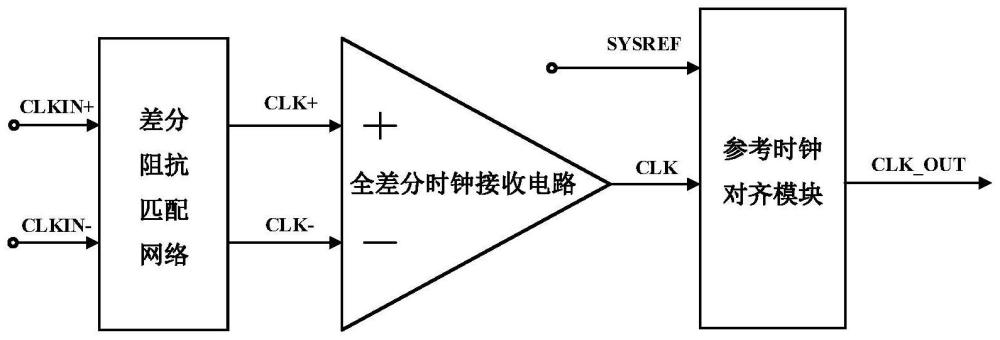

3、本发明提供了一种用于流水线型模数转换器的差分时钟接收电路,包括:差分阻抗匹配网络、全差分时钟接收模块及参考时钟对齐模块;其中,

4、所述差分阻抗匹配网络,用于对外部输入的第一差分时钟信号进行阻抗匹配,得到第二差分时钟信号;

5、所述全差分时钟接收模块,包括:全差分时钟接收运放、差分转单端运放以及第一反相器链;

6、其中,所述全差分时钟接收运放用于接收并放大所述第二差分时钟信号,得到第三差分时钟信号;所述全差分时钟接收运放为全pmos管搭建的套筒式运放,所述套筒式运放的同相输入端和同相输出端之间跨接电容c1,反相输入端和反相输出端之间跨接电容c2;

7、所述差分转单端运放,用于将所述第三差分时钟信号转为第一时钟信号;

8、所述第一反相器链用于对所述第一时钟信号进行波形整形,得到第二时钟信号;

9、所述参考时钟对齐模块,用于对所述第二时钟信号和参考时钟信号进行比较,得到时钟延时信号;比较所述时钟延时信号和参考延时信号;若所述时钟延时信号的延时大于所述参考延时信号的延时,对所述第二时钟信号进行至少一次的脉宽调制,直至所述第二时钟信号的上升沿与所述参考时钟信号的上升沿对齐后将其输出;若所述时钟延时信号的延时不大于所述参考延时信号的延时,输出所述第二时钟信号;其中,所述参考时钟信号为与所述第一差分时钟信号的正信号同相位的时钟信号;所述参考延时信号是将所述参考时钟信号延时预设时长得到的,所述预设时长为所述参考时钟信号的最大允许延时。

10、在一个实施例中,本发明的差分阻抗匹配网络包括:内部静态偏置电路、电阻网络和二极管保护电路;

11、所述内部静态偏置电路,用于为所述差分阻抗匹配网络提供固定的内部直流弱驱动偏置;

12、所述电阻网络,用于对所述第一差分时钟信号进行阻抗匹配,得到所述第二差分时钟信号;

13、所述二极管保护电路,用于为所述差分阻抗匹配网络提供静电保护。

14、在一个实施例中,本发明的差分阻抗匹配网络包括:nmos管nm1、电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、二极管dio1、二极管dio2、二极管dio3和二极管dio4;其中,电阻r2连接电阻r3,nmos管nm1的栅极连接第一偏置电压,源极接地,漏极通过电阻r1连接电阻r2与电阻r3两者的连接节点;

15、电阻r2远离所述连接节点的一端接收所述第一差分时钟信号的第一子信号,并通过电阻r4输出所述第二差分时钟信号的第一子信号;

16、电阻r3远离所述连接节点的一端接收所述第一差分时钟信号的第二子信号,并通过电阻r5输出所述第二差分时钟信号的第二子信号;同一差分时钟信号的第一子信号和第二子信号振幅相同、相位相反;

17、二极管dio1的正端接地,负端连接所述第一差分时钟信号的第一子信号;

18、二极管dio2的正端连接所述第一差分时钟信号的第一子信号,负端连接电源电压;

19、二极管dio3的正端接地,负端连接所述第一差分时钟信号的第二子信号;

20、二极管dio4的正端连接所述第一差分时钟信号的第二子信号,负端连接电源电压。

21、在一个实施例中,本发明的全差分时钟接收运放包括:pmos管pm1、pmos管pm2、pmos管pm3、pmos管pm4、pmos管pm5、pmos管pm6、pmos管pm7、pmos管pm8、电容c1、电容c2和电阻r6;

22、其中,pmos管pm1的栅极连接第二偏置电压,源极连接电源电压,漏极连接pmos管pm2的源极和pmos管pm3的源极;

23、pmos管pm2的栅极接收所述第二差分时钟信号的第一子信号,源极连接pmos管pm1的漏极和pmos管pm3的源极,漏极连接pmos管pm4的源极;

24、pmos管pm3的栅极接收所述第二差分时钟信号的第二子信号,源极连接pmos管pm1的漏极和pmos管pm2的源极,漏极连接pmos管pm5的源极;

25、pmos管pm4的栅极连接第三偏置电压,源极连接pmos管pm2的漏极;pmos管pm4的漏极连接pmos管pm6的源极,连接处为第一节点;所述第一节点输出所述第三差分时钟信号的第二子信号;

26、pmos管pm5的栅极连接所述第三偏置电压,源极连接pmos管pm3的漏极;pmos管pm5的漏极连接pmos管pm7的源极,连接处为第二节点;所述第二节点输出所述第三差分时钟信号的第一子信号;

27、pmos管pm6的栅极连接第四偏置电压,源极连接pmos管pm4的漏极,漏极连接pmos管pm8的源极;

28、pmos管pm7的栅极连接所述第四偏置电压,源极连接pmos管pm5的漏极,漏极连接pmos管pm8的源极;

29、pmos管pm8的源极连接pmos管pm6的漏极和pmos管pm7的漏极,栅极连接第五偏置电压,漏极接地;

30、电阻r6的一端连接所述第一节点,另一端连接所述第二节点;

31、电容c1的一端连接第二差分时钟信号的第一子信号,另一端连接所述第二节点;

32、电容c2的一端连接第二差分时钟信号的第二子信号,另一端连接所述第一节点。

33、在一个实施例中,本发明的差分转单端运放包括:pmos管pm9、pmos管pm10、nmos管nm2、nmos管nm3、nmos管nm4和nmos管nm5;

34、其中,nmos管nm2的栅极与漏极均连接所述第二节点,源极接地;

35、nmos管nm3的栅极与漏极均连接所述第一节点,源极接地;

36、nmos管nm4的栅极分别连接nmos管nm2的栅极和所述第二节点,漏极连接pmos管pm9的栅极和漏极以及pmos管pm10的栅极,源极接地;

37、nmos管nm5的栅极分别连接nmos管nm3的栅极和所述第一节点,漏极连接pmos管pm10的栅极和漏极以及pmos管pm9的栅极,源极接地;

38、pmos管pm9的栅极和漏极均连接nmos管nm4的漏极以及pmos管pm10的栅极,源极连接电源电压;

39、pmos管pm10的栅极分别连接pmos管pm9栅极和漏极以及nmos管nm4的漏极,源极连接电源电压;pmos管pm10漏极连接nmos管nm5的漏极,连接处为第三节点,所述第三节点输出第一时钟信号。

40、在一个实施例中,本发明的第一反相器链包括:第一级反相器、第二级反相器和nmos管nm8;

41、其中,所述第一级反相器的输入端连接所述第三节点,输出端连接所述第二级反相器的输入端;

42、nmos管nm8的栅极分别连接所述第一级反相器的输出端和所述第二级反相器的输入端,源极接地,漏极连接所述第一级反相器的输入端及所述第三节点;

43、所述第二级反相器的输出端输出所述第二时钟信号。

44、在一个实施例中,本发明的参考时钟对齐模块,包括:上升沿判别电路;

45、所述参考时钟对齐模块,对所述第二时钟信号和所述参考时钟信号进行比较,得到所述时钟延时信号,包括:

46、由所述上升沿判别电路对所述第二时钟信号和所述参考时钟信号进行比较,得到所述时钟延时信号;

47、所述上升沿判别电路包括:d触发器dff1、d触发器dff2以及与门and1;

48、其中,所述d触发器dff1和所述d触发器dff2的d端均接电源电压,所述d触发器dff1的clk端输入所述参考时钟信号,dff2的clk端输入所述第二时钟信号,所述d触发器dff1和所述d触发器dff2的q端分别连接与门and1的两个输入端,与门and1的输出端连接所述d触发器dff1和所述d触发器dff2的reset端,所述d触发器dff1的q端输出所述时钟延时信号。

49、在一个实施例中,本发明的参考时钟对齐模块,还包括:延时判别模块;

50、所述参考时钟对齐模块,比较所述时钟延时信号和所述参考延时信号,包括:

51、由所述延时判别模块对所述时钟延时信号和所述参考延时信号进行比较;

52、所述延时判别模块包括:n个非门、与门and2和与门and3;n为偶数;

53、其中,所述n个非门串联形成第二反相器链,所述第二反相器链的输入端接入所述参考时钟信号,输出端输出所述参考延时信号;

54、与门and2的两个输入端分别输入所述参考时钟信号和所述时钟延时信号,输出端连接与门and3的一个输入端,所述参考延时信号接入与门and3的另一个输入端,与门and3的输出端输出延时判别结果;

55、所述延时判别结果在所述时钟延时信号的延时不大于所述参考时钟延时信号的延时时为低电平;所述延时判别结果在所述时钟延时信号的延时大于所述参考时钟信号的延时时为高电平。

56、在一个实施例中,本发明的参考时钟对齐模块,还包括:脉宽调制模块;

57、所述参考时钟对齐模块,对所述第二时钟信号进行脉宽调制,包括:

58、由所述脉宽调制模块对所述第二时钟信号进行至少一次的脉宽调制,直至所述第二时钟信号的上升沿与所述参考时钟信号的上升沿对齐;

59、所述脉宽调制模块包括:上升沿对齐模块和下降沿对齐模块;

60、其中,所述上升沿对齐模块包括:或门or1、与门and4、与非门nand1、与非门nand2、与非门nand3和非门n1;

61、或门or1的两个输入端分别连接所述参考时钟信号和所述第二时钟信号,输出端连接与非门nand1的一个输入端;

62、与门and4的两个输入端分别连接所述参考时钟信号和所述第二时钟信,输出端连接与非门nand2的一个输入端;

63、与非门nand1的两个输入端分别连接或门or1的输出端和非门n1的输出端,与非门nand1输出端连接与非门nand3的一个输入端;

64、非门n1的输入端输入使能信号,输出端连接与非门nand1的其中一个输入端,所述使能信号为所述延时判别结果取反后的信号;

65、与非门nand2的两个输入端分别连接与门and4的输出端和使能信号,输出端连接与非门nand3的另一个输入端;

66、与非门nand3的两个输入端分别连接与非门nand1的输出端和与非门nand2的输出端,输出端输出上升沿调制后的第二时钟信号;

67、所述下降沿对齐模块包括:电流饥饿反相器、反相器in1、nmos管nm11、反相器in2以及反相器in3;

68、所述电流饥饿反相器的输入端输入所述上升沿调制后的第二时钟信号;输出端分别连接反相器in1的输入端和nmos管nm11的漏极;

69、nmos管nm11的漏极分别连接所述电流饥饿反相器的输出端和反相器in1的输入端,栅极分别连接反相器in1的输出端和反相器in2的输入端,源极接地;

70、反相器in1的输入端分别连接所述电流饥饿反相器的输出端和nmos管nm11的漏极,输出端分别连接反相器in2的输入端及nmos管nm11的栅极;

71、反相器in2的输入端分别连接反相器in1的输出端和nmos管nm11的栅极,输出端连接反相器in3的输入端;

72、反相器in3的输入端连接反相器in2的输出端,输出端输出下降沿调制后的第二时钟信号。

73、本发明提供的一种用于流水线型模数转换器的差分时钟接收电路具有如下有益效果:

74、本发明提出的全差分时钟接收运放采用全pmos管实现,全pmos管运放的电路噪声相对于nmos管运放有明显降低。全差分时钟接收运放中pmos管构成套筒式运算放大器,该结构保障了全差分时钟接收运放的整体增益。全差分时钟接收运放中的电容c1与电容c2分别跨接在同相输入输出端和反向输入输出端,消除了寄生电容的密勒效应,保障了运放的带宽,并且起到了隔离直流信号的作用。

75、全差分时钟接收模块的第一反向器链利于恢复输入的时钟信号,对时钟信号的跳变边沿整形,使其更加陡峭,降低时钟跳变时间。由第一反相器链输出的时钟信号,拥有较低的时钟相位噪声、时钟抖动和较高的占空比精度,相较于传统结构来说不需要附加大面积的占空比校正电路,因而可以有效地节省整体芯片的面积与功耗。

76、进一步的本发明提出参考时钟对齐模块,使第一反相器链输出的第二时钟信号与参考时钟信号对齐。该校准技术通过校准上升沿下降沿来有效降低第二时钟信号的时钟抖动,以此提高整个模数转换器的信噪比。

77、综上所述,全差分时钟接收电路提高了电路增益,降低了在时钟接收过程中引入的噪声,保证了输入时钟信号的完整性,减小了时钟信号在时钟接收电路中的相位噪声与时钟抖动。

78、以下将结合附图及对本发明做进一步详细说明。

- 还没有人留言评论。精彩留言会获得点赞!