芯片组装结构及其形成方法与流程

本申请的实施例涉及芯片组装结构及其形成方法。

背景技术:

1、存储器阵列需要控制电路来控制存储器阵列内的存储器单元的操作。控制电路需要在半导体衬底上形成场效应晶体管。因此,在半导体衬底上形成控制电路,并且在覆盖控制电路的后端制程(beol)结构内形成存储器阵列。这种方法产生了存储器阵列和控制电路集成在同一半导体管芯内的器件。

技术实现思路

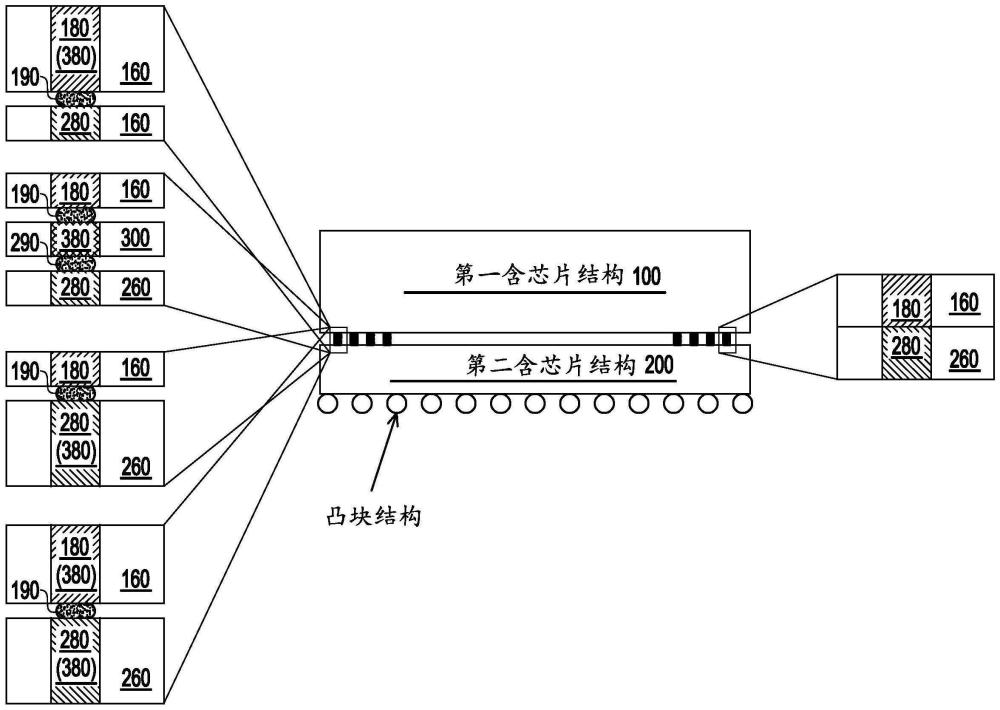

1、根据本申请的实施例的一个方面,提供了一种芯片组装结构,包括:第一含芯片结构,包括后端制程(beol)存储器管芯,beol存储器管芯包括存储器单元阵列和电连接到存储器单元阵列的对应节点的金属互连结构,其中,beol存储器管芯没有任何半导体材料部分或者beol存储器管芯内的每个半导体材料部分的横向范围小于存储器单元阵列内的每个存储器单元的横向范围,第一含芯片结构包括第一接合结构,并且第一接合结构的子集电连接到beol存储器管芯中的金属互连结构;以及第二含芯片结构,包括控制电路,控制电路包括配置为控制存储器单元阵列的操作的场效应晶体管并且还包括第二接合结构;其中,第二接合结构通过金属对金属接合或衬底贯通孔介导接合而接合到第一接合结构。

2、根据本申请的实施例的一个方面,提供了一种芯片组装结构,包括:第一含芯片结构,包括后端制程(beol)存储器管芯,beol存储器管芯包括存储器单元阵列和电连接到存储器单元阵列的对应节点的金属互连结构,其中,beol存储器管芯不含任何场效应晶体管,第一含芯片结构包括第一接合结构,并且第一接合结构的子集电连接到beol存储器管芯中的金属互连结构;以及第二含芯片结构,包括控制电路,控制电路包括配置为控制存储器单元阵列的操作的场效应晶体管并且还包括第二接合结构,其中,第二接合结构通过金属对金属接合或衬底贯通孔介导接合而接合到第一接合结构。

3、根据本申请的实施例的一个方面,提供了一种形成芯片组装结构的方法,方法包括:形成第一含芯片结构,第一含芯片结构包括后端制程(beol)存储器管芯,其中beol存储器管芯包括存储器单元阵列和电连接到存储器单元阵列的对应节点的金属互连结构,其中,beol存储器管芯没有任何半导体材料部分或者beol存储器管芯内的每个半导体材料部分的横向范围小于存储器单元阵列内的每个存储器单元的横向范围,并且第一接合结构的子集电连接到beol存储器管芯中的金属互连结构;提供第二含芯片结构,包括控制电路,控制电路包括配置为控制存储器单元阵列的操作的场效应晶体管并且还包括第二接合结构;以及通过诱导第二接合结构和第一接合结构之间的金属对金属接合或衬底贯通孔介导接合而将第二含芯片结构与第一含芯片结构接合。

技术特征:

1.一种芯片组装结构,包括:

2.根据权利要求1所述的芯片组装结构,其中,从所述第一接合结构和所述第二接合结构中选择的接合结构的至少一个集合包括衬底贯通孔结构的阵列,所述衬底贯通孔结构的对应高度大于对应横向尺寸。

3.根据权利要求1所述的芯片组装结构,其中,从所述第一接合结构和所述第二接合结构中选择的接合结构的至少一个集合包括金属接合焊盘的阵列,所述金属接合焊盘的对应横向尺寸大于对应厚度。

4.根据权利要求1所述的芯片组装结构,其中:

5.根据权利要求1所述的芯片组装结构,其中:

6.根据权利要求1所述的芯片组装结构,其中,所述后端制程存储器管芯不含任何场效应晶体管。

7.根据权利要求1所述的芯片组装结构,其中,所述后端制程存储器管芯不含任何半导体材料。

8.根据权利要求1所述的芯片组装结构,其中:

9.一种芯片组装结构,包括:

10.一种形成芯片组装结构的方法,所述方法包括:

技术总结

提供了一种芯片组装结构及其形成方法,该结构包括第一含芯片结构和第二含芯片结构。第一含芯片结构包括后端制程(BEOL)存储器管芯,其包括存储器单元阵列和电连接到存储器单元阵列的对应节点的金属互连结构。BEOL存储器管芯没有任何半导体材料部分或者BEOL存储器管芯内的每个半导体材料部分的横向范围小于存储器单元阵列内的每个存储器单元的横向范围。第一含芯片结构包括第一接合结构,并且第一接合结构的子集电连接到BEOL存储器管芯中的金属互连结构。第二含芯片结构包括控制电路,该控制电路包括配置为控制存储器单元阵列的操作的场效应晶体管并且还包括第二接合结构。第二接合结构通过金属对金属接合或衬底贯通孔介导接合而接合到第一接合结构。

技术研发人员:野口紘希,王奕

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!